NIST-Intel Partnership Workshop

In November, 2014, NIST hosted the seventh in a series of workshops in a NIST-Intel partnership effort on Emerging Nanoscale Interface and Architecture Characterization (ENIAC). The nanoscale metrology initiative began in 2011, strengthened by Material Transfer Agreements and Cooperative Research and Development Agreements. The program has resulted in the sharing of state-of-the-art samples for evaluation by about 20 NIST characterization techniques that do not exist anywhere else in the world.

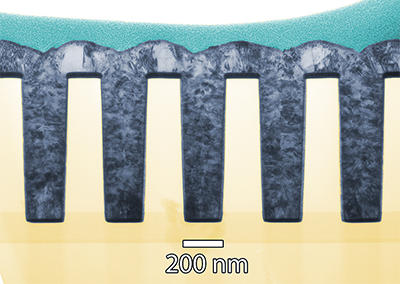

Metrology for future electronic materials and devices has become so complex and difficult that NIST's metrology expertise is critical for advancing the frontiers of nanoelectronics. "This partnership is a win-win for both Intel and NIST," said workshop co-organizer David Seiler, Chief of PML's Semiconductor and Dimensional Metrology Division. "New, innovative measurement techniques, including three-dimensional imaging, need to be developed and tested to understand and control device performance.

"NIST benefits greatly from the program because we get access to state-of-the-art structures and devices to test the usefulness and limits of our world-class measurement capabilities."