Summary

Our group is developing FPGA based digital phase noise measurement and control systems.

Description

Until recently, the precision measurement of phase noise, spectral purity, and related quantities had been a challenging process, with only a handful of qualified experts in the world. However, Field Programmable Gate Array (FPGA) based measurement systems, similar to software defined radio (SDR), are revolutionizing metrology and making these measurements accessible to non-experts. Our group continues research in this area and is currently developing the next generation of amplitude and phase noise analyzers. By incorporating fast and modern ADC and FPGA platforms, we hope to implement analyzers that maximize data use for the fastest averaging rates. Specifically, we are developing:

I. Digital phase and amplitude noise measurement systems (DPANMS)

Most current DPANMS only perform the data acquisition and the initial decimation in the FPGA fabric. All further analytical processing occurs in software after a transfer from the FPGA to the CPU. This results in a system that is computationally limited, therefore discarding vast amounts of useful data and significantly restricting the averaging rate for the high offset frequency FFTs. The data for a 250 MHz, 1024-point FFT can be acquired in 4µs. This corresponds to 250k FFT/s and would allow 106 spectra to be averaged in 4 seconds, thereby supporting a cross-spectral improvement of 30 dB at a 100 MHz offset frequency. These speeds are currently unheard of in digital phase noise metrology.

The goal of this project is to make a DPANMS that is entirely acquisition time limited, and allow for each acquired data point to be fully utilized in analysis. At the effective analysis sample rate, we would like to calculate and average one frequency-domain point for each time-domain point processed.

II. Digital measurement and control systems for optical physics experiments

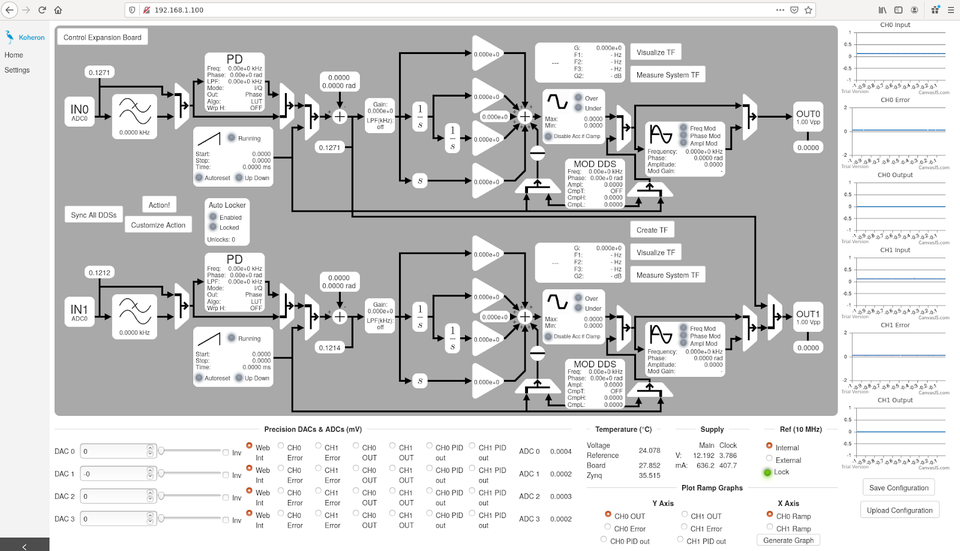

We are developing a general-purpose, dual-channel FPGA based digital servo with a minimum latency around 200 ns and bandwidths in excess of 1 MHz. This servo implements a proportional, dual-integration and derivative (PIID) controller along with internal numerically controlled oscillators (NCO), a phase detector (PD) utilizing a fast in-phase and quadrature (I/Q) detection algorithm (80 ns), NCO modulator, network analyzer, auto-locker, ramp generator, and low pass filters. A web interface and/or python commands over TCP/IP allow full control over all system parameters. The servo has been successfully used to lock Pound-Drever-Hall cavities, phase-locked loops and optical frequency combs.

Web interface to control and monitor the servo. Each block is interactive and allows the user to change its configuration and parameters.

III. Multi-channel time measurement system and time scales

The goal of this project is to develop a multi-channel, all-digital FPGA based time-difference measurement system for clock metrology and ensemble time scale implementation. When a laboratory has multiple clocks, a reliable and redundant time scale can be generated with the careful measurement of all the individual clocks and combination of the results to produce a weighted average time scale. The performance and reliability of a generated time scale will be greater than that of any individual clock comprising the ensemble. High-performance clock metrology is typically done using a dual-mixer time-difference (DMTD) measurement system implemented with analog mixers, a transfer oscillator, zero-crossing detectors and time interval counters. These systems allow for careful measurement of phase offset between the oscillators in order to characterize them as clocks. However, each of these analog components contribute to technical and environmental noise.

Throughout the last decade, all-digital time measurement systems have emerged with a 10-fold improvement in performance over the analog DMTD systems. By digitizing the clock inputs directly in analog-to-digital converters (ADC) and performing all the subsequent signal processing in the digital domain, one can limit most of the environmental issues to the initial ADC stage. These systems utilize digital down converters (DDC) which are comprised of direct digital synthesizers, digital quadrature mixing, and coordinate rotation digital computers (CORDIC) for the determination of the phase evolution between the measured signals. This architecture lends itself perfectly to implementation in a FPGA where processing is stable, deterministic and environmentally insensitive.