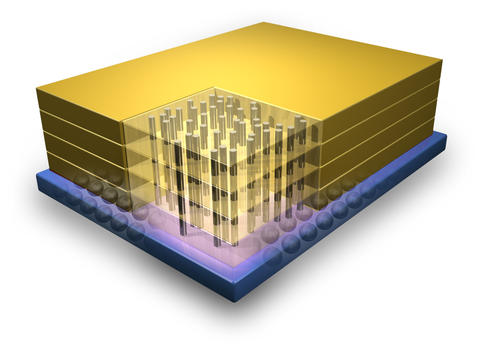

Graphical representation of a stack of individual chips connected by vertical pipelines or through silicon vias (TSVs).

Could three-dimensional stacked integrated circuits (3DS-ICs) be the next big innovation in technology development? Imagine layer upon layer of integrated circuits ground as thin as possible and stacked like the world's smallest Dagwood sandwich, and you have the basic concept. Tiny interconnecting pillars, or through-silicon vias (TSVs), connect the layers, providing power and signal distribution. The end result is a multi-functioning integration of systems that takes up much less real estate and consumes less power than previously possible.

Early examples of 3DS-ICs already on the market can be found in digital cameras, with the image sensor bonded face-to-face to a chip with the control circuitry. The back of the image sensor chip is then thinned enough so the light impinges from the back side, without being partially blocked by the wiring. In addition, there are numerous high-volume applications of 3DS-ICs projected, starting in 2012 with memory for portable devices and in the longer term heterogeneous integration of two or more chips from entirely different processes, bringing together functions such as MicroElectroMechanical Systems (MEMS), logic, memory, radio frequency (RF), and optoelectronic in a single stack.

An important issue related to the production of 3DS-ICs is that the individual layers of such a stacked circuit will likely be mass-produced by different companies. As a result, standards are needed for ensuring that these disparate layers successfully work with each other. Issues that must be addressed include tools to design a stacked chip, bonding, yield (which is decreased due to the stacking of wafers) and reliability due to the adherence of the layers, the behavior of the TSV connections, and various other factors. Additional standards are needed for the safe transport of thinned wafers, which will originate from different locations and will be stacked and packaged at still another location. This is where NIST comes in.

The Semiconductor and Dimensional Metrology Division (SDMD) in NIST's Physical Measurement Laboratory (PML) developed the world's first standards for MEMS over the last decade. MEMS technology is prevalent in many consumer products: for example, the heads of inkjet printers, smart phones (accelerometers, gyroscopes, and microphones), and automobiles (sensors for airbags, tire pressure, and braking systems). The long-term reliability for these devices, especially in the automotive applications, is critical.

The most recent of the NIST-led MEMS standards was on wafer bond strength measurements, which relates to the strength of the adhesion between two wafers. SEMI, an international industry association serving the manufacturing supply chain for the micro- and nano-electronics industries, sought out NIST's unique expertise and impartiality for help in completing this particular standard. Richard Allen of the SDMD led this task, co-writing the standard and leading the round-robin to validate the data. SEMATECH, a consortium created to perform research and development on chip manufacturing, took notice. SEMATECH was a part of the task force (led by Allen) assigned to develop this standard because of their concerns with wafer bonding reliability in 3DS-ICs. Dr. Sitaram Arkalgud, the Director of 3D integration at SEMATECH, was impressed: "This critical validated standard ... would not exist today without Mr. Allen's leadership."

Almost immediately after the publication of the MEMS wafer bond strength measurement standard in 2010, SEMATECH pursued Allen to begin efforts on other standards that are critically needed for this new technique. SEMATECH requested that Allen be detailed to its Albany, NY, facility to work directly with its staff and member companies and drive the development of standards for 3DS-ICs. In early 2011, the agreement was made, and Allen left for Albany, where he'll stay until March 2013.

Since joining SEMATECH as an assignee, Allen took on the role of co-chair of the recently set-up SEMI Three-Dimensional Stacked Integrated Circuits Committee and has already played a role in the development of five separate SEMI standards related to 3DS-ICs. The first two of these are being balloted; the other three are expected to be balloted in 2012:

Specification for Parameters for Bonded Wafer Stacks. Wafer thickness, diameters, and other characteristics are changed when wafer stacks are bonded together, or wafer stacks are bonded and thinned. Additionally, there is no existing guidance available on how to bond wafers from different manufacturers together. "Somebody's going to have to take these two disparate parts that were fabricated by different people and understand what's on each one and how to connect them together," Allen explains. The draft standard produced by a team led by Allen is designed to provide the tools for the people at each step of the chain to communicate exactly what is being delivered to the next step.

Guide for Terminology for Measured Geometrical Parameters of TSVs in 3DS-ICs. This standard presents the definitions of which measurements should be made on 3DS-ICs. This activity is being led by Dave Read of NIST's Material Measurement Laboratory.

Guide for Multi-Wafer Transport and Storage Containers for Thin Wafers. In the 3DS-IC processes discussed above, a device wafer is bonded to a carrier wafer, thinned to less than 100 µm, and de-bonded onto dicing tape. The resulting de-bonded wafer is very thin and fragile, but still needs to be packaged and shipped to the location where it will be stacked with other wafers. "We are doing the testing to figure out if the packaging techniques that are being proposed by the different suppliers will be the standards for impact," Allen explains.

Specification for Identification and Marking for Bonded Wafer Stacks. Every wafer has a unique, machine-readable mark on it for identification and automated handling. Over the past couple of decades, virtually all tools for fabricating devices have incorporated automation for the tracking and processing of wafers. But the software and hardware that implement this automation are not compatible with the techniques of stacking and thinning of wafers. This standard is examining how to handle these new issues.

To help summarize these and any other 3DS-IC standards being developed by different standard development organizations (SDOs), Allen designed and developed a comprehensive 3D standards wiki website.

"We're trying to identify what standards work is going on that is applicable to 3D stacked integrated circuits, put it into a public forum, and use this as a tool to market the standards development work to the wider industry," Allen says. "It gives people who are interested in finding out about the standards work for 3DS-IC one-stop shopping." A joint press release between SEMATECH and four other SDOs was issued in Nov. 2011 to promote the website.

As Richard Allen begins to enter the second and final year of his assignment at SEMATECH, he will continue his efforts on developing and publishing the five aforementioned standards and start additional ones. "You have to determine what are the standards and measurements that are necessary to help things happen," he explains. Being at SEMATECH affords Allen the unique opportunity to do this. "I have the opportunity to work directly with the manufacturing community as this new approach to miniaturization moves towards widespread production," he says. Allen's efforts on these measurement standards are a first, but critical step.