# **CHIPS** for AMERICA

# Manufacturing USA Semiconductor Institute(s)

Summary of Responses to Request for Information

June 1, 2023

Manufacturing

CHIPS for America includes the CHIPS Program Office, responsible for semiconductor incentives, and the CHIPS Research and Development Office, responsible for R&D programs. Both sit within the National Institute of Standards and Technology (NIST) at the Department of Commerce.

NIST promotes U.S. innovation and industrial competitiveness by advancing measurement science, standards, and technology in ways that enhance economic security and improve our quality of life. NIST is uniquely positioned to successfully administer the CHIPS for America program because of the bureau's strong relationships with U.S. industries, its deep understanding of the semiconductor ecosystem, and its reputation as fair and trusted.

Visit <u>https://www.chips.gov</u> to learn more.

NIST Special Publication NIST AMS 600-12

# Manufacturing USA Semiconductor Institute(s)

Summary of Responses to Request for Information

This publication is available free of charge from: https://doi.org/10.6028/NIST.AMS.600-12

### CONTENTS

| Org  | anization of the Report                                                              | 4  |

|------|--------------------------------------------------------------------------------------|----|

| I.   | Executive Summary                                                                    | 5  |

| 11.  | Introduction and Background                                                          | 6  |

| 111. | RFI Response Overview                                                                | 7  |

| Key  | themes across RFI topics                                                             | 8  |

|      | Institute Scope                                                                      | 8  |

|      | Institute Structure and Governance                                                   | 13 |

|      | Strategies for Driving Co-Investment and Engagement                                  | 14 |

|      | Education and Workforce Development                                                  | 14 |

|      | Metrics and Success                                                                  | 16 |

| IV.  | RFI Categorial Responses                                                             | 17 |

|      | Institute Scope                                                                      | 17 |

|      | 1. Coordination with other CHIPS-Act-funded R&D efforts                              | 17 |

|      | 2. Complementarity with and non-duplication of existing Manufacturing USA institutes | 18 |

|      | 3. Role for existing Manufacturing USA institutes in semiconductor R&D               | 19 |

|      | 4. Scale needed for impact on semiconductor manufacturing innovation                 | 25 |

|      | 5. Appropriate technical scope for impact without duplication                        | 26 |

|      | Institute Structure and Governance                                                   | 28 |

|      | 6. Unique considerations for semiconductor/microelectronics technology sector        | 28 |

|      | 7. Risks and benefits of "up to three" semiconductor institutes                      | 30 |

|      | 8. Ensuring stakeholder participation                                                | 31 |

|      | Strategies for Driving Co-Investment and Engagement                                  | 32 |

|      | 9. Investment Tax Credit for industry                                                | 32 |

|      | 10. Factors influencing non-federal co-investment                                    | 34 |

|      | 11. Sustaining institute operations in the absence of continued federal support        | 35 |

|------|----------------------------------------------------------------------------------------|----|

|      | 12. Foreign entities                                                                   | 36 |

|      | 13. Other federally funded programs                                                    | 37 |

|      | 14. Interaction with state and local economic development entities                     | 38 |

|      | 15. Standards development bodies                                                       | 38 |

|      | Education and Workforce Development                                                    | 39 |

|      | 16. Supporting workforce and awareness at all educational levels                       | 39 |

|      | 17. Engaging full diversity of education and vocational training organizations         | 39 |

|      | 18. Ensuring focus and industry priorities                                             | 40 |

|      | 19. Leveraging existing workforce programs                                             | 40 |

|      | 20. Success measures                                                                   | 41 |

|      | 21. Integration of R&D with workforce                                                  | 41 |

|      | 22. Building a steady pipeline of skilled workers                                      | 42 |

|      | 23. Broadening the talent base                                                         | 43 |

|      | 24. Education and workforce development mechanisms                                     | 43 |

|      | Metrics and Success                                                                    | 44 |

|      | 25. Sector-specific economic competitiveness, national security, technology innovation | 44 |

|      | 26. Semiconductor institute specific education and workforce development               | 45 |

|      | 27. Semiconductor manufacturing ecosystem development                                  | 46 |

|      | 28. First-year considerations                                                          | 47 |

| V.   | Appendix A - Acronyms                                                                  | 48 |

| Cita | ations                                                                                 | 49 |

### **ORGANIZATION OF THE REPORT**

This document provides an overview of the stakeholder responses, consensus, and an overarching summary of some of the thematic areas that emerged from the Manufacturing USA Request for Information (RFI).

NIST's approach to summarizing the comments received in the RFI was to capture the range and breadth of public input, including common themes and points of divergence. NIST appreciates the richness of the input received and recognizes that detailed specific comments may not be included in this summary. Readers who would like to see the comments in their entirety can find those at regulations.gov.<sup>1</sup>

The RFI analysis and high-level summary was performed by the NIST team (named below) by categorizing responses by the five RFI topic areas, individual questions and corresponding responses when applicable, and respondent and organization type. Where applicable, the NIST team also appropriately mapped comments from the text of the general responses to specific RFI questions. Where applicable, specific suggestions from the responses were reproduced as part of the high-level summary.

#### ACKNOWLEDGMENTS

| Mahesh Mani*       | Greta Babakhanova* | Kelley Rogers* |

|--------------------|--------------------|----------------|

| Frank Gayle        | Mike Molnar        | David Seiler   |

| Lisa Jean Fronczek | Erin Lavik         | Don Ufford     |

| Zara Brunner       | Clifton Ray        |                |

### I. EXECUTIVE SUMMARY

In a Request for Information (RFI) that was published in the Federal Register on October 13, 2022, the National Institute of Standards and Technology (NIST) Office of Advanced Manufacturing requested public input to inform the design of, and requirements for, potential Manufacturing USA institute(s) that would strengthen the semiconductor and microelectronics innovation ecosystem in such areas as design, fabrication, advanced test, assembly, and packaging capabilities.<sup>2</sup> The RFI was open from October 13, 2022 to December 12, 2022. Information was requested in five areas:

- 1. Institute scope

- 2. Institute structure and governance

- 3. Strategies for driving co-investment and engagement

- 4. Education and workforce development

- 5. Metrics and success

There were more than 90 responses<sup>3</sup> to the solicitation, with the majority of responses submitted by semiconductor-related industries.

**Institute Scope.** Responders suggested that the new institutes should be transformational, tackling challenging problems that bridge the gaps from research and development (R&D) to full-scale manufacturing. Several responders suggested focus areas or themes for the new institutes, such as smart manufacturing and packaging, advanced packaging substrate technology, substrate manufacturing, design for manufacturing, and infrastructure to support technology transition to commercial and defense applications. Responders did not reject any of the topics listed in the RFI questions as inappropriate, but also did not indicate a clear consensus for potential topics for a new Manufacturing USA institute or institutes. While no clear consensus emerged from responses with respect to the question of "one super-sized" institute versus two-three smaller institutes, responders agreed that the size of the institute(s) funded should flow from the footprint needed to achieve impact in the chosen technology space. There was an absolute consensus expressed for the need to carefully coordinate the activities and scopes for any new semiconductor Manufacturing USA institutes with those of semiconductor-related R&D investments, including the National Advanced Packaging Manufacturing Program (NAPMP), national semiconductor technology center (NSTC), and existing Manufacturing USA institutes in related spaces.

**Institute Structure and Governance.** Responders agreed that the original 2013 design framework<sup>4</sup> for Manufacturing USA may still be relevant for informing the design of new Manufacturing USA semiconductor institute(s). Responders also agreed that some of the existing institutes may present a good model for the new institutes. However, responders agreed that the typical scale of the existing institutes is insufficient to have a measurable impact on the capital-intensive semiconductor manufacturing ecosystem.

#### Strategies for Driving Co-Investment.

Responders generally agreed that co-investment<sup>5</sup> by all members in the Manufacturing USA semiconductor institute(s) is important in creating shared value and impact in each institute's mission space. Responders were also in agreement that the co-investment strategy for each institute should be structured to encourage and enable robust participation across the full diversity of stakeholders. Many responders pointed to the need for shared access to capital-intensive equipment, fabrication facilities, and novel materials as essential to success, although there were diverse opinions expressed on how to best achieve that goal. Estimates for the scale of the federal investment needed ranged from \$150 million over five years to \$1 billion over five years. Most responders noted that federal funding was likely to be needed beyond five years to secure a cohesive partnership, but that, ultimately, the institute(s) could be self-sustainable if properly focused on industry needs.

#### **Education and Workforce Development.**

Responders generally agreed that the Manufacturing USA semiconductor institute(s) could play a role in supporting experiential learning opportunities for all educational levels, including primary/secondary students through university and postgraduate students along with incumbent workers. The responders suggested that programming will need to include awareness-building, recruitment, training, and upskilling for both technician and engineering levels. Responders further agreed that the new institute(s) should leverage the existing Manufacturing USA education and workforce development (EWD) network other workforce programs, work closely with the existing

institutes in adjacent fields, establish connections with new networks anticipated under NSTC and NAPMP, and engage with universities, trade schools, and community colleges that have diverse education and vocational training. Responders stressed that having a strong partnership with industry members is imperative to ensure that advanced manufacturing workforce development activities effectively address industry priorities. Responders also suggested the institute(s) work closely with industry to ensure a broad talent base is captured, and all community groups, especially those that have been under represented, are given the opportunity for successful careers.

**Metrics and Success.** Responders agreed on the need to track measures to demonstrate the impact of the Manufacturing USA semiconductor institute(s) on U.S. semiconductor manufacturing ecosystems. Several responders suggested performance metrics aligned with institute objectives to measure both operational and technical progress that can be indicators for innovation and economic competitiveness of the domestic semiconductor industry. Responders also suggested leveraging the best practices of the existing Manufacturing USA institutes and their federal agency sponsors to develop and implement metrics.

# II. INTRODUCTION AND BACKGROUND

Semiconductors are fundamental to nearly all modern industrial and national security activities, and are essential building blocks of critical and emerging technologies, such as artificial intelligence (AI), autonomous systems, next-generation communications, and quantum computing.

The U.S. semiconductor industry has historically led in many parts of the semiconductor supply chain, such as R&D, chip design, and manufacturing. Over the past couple of decades, the U.S. position in the global semiconductor industry has dramatically declined. In 2019, the United States accounted for 11 percent of global semiconductor fabrication capacity, down from 13 percent in 2015 and continuing a long-term decline from around 37 percent in 1990.<sup>8</sup> Semiconductor packaging also presents a critical supply chain challenge since less than 3% of global packaging capacity is in North America.<sup>6</sup> Much of the overseas semiconductor manufacturing capacity today is in Taiwan, South Korea, and, increasingly, China.<sup>7</sup>

The fragility of the current global semiconductor supply chain was put squarely on display in 2020. The industry faced significant disruptions as a result of the coronavirus pandemic, a fire affecting a major supplier in Japan, and a severe winter storm that disabled production in facilities in Texas for several days. These events, together with other factors, including pandemic-induced shifts in consumer demand, contributed to a global semiconductor shortage that affected multiple manufacturing sectors that rely on semiconductors as critical components for their finished products. Especially severely hit was the automotive industry, which saw plants idled for months.<sup>9</sup>

The Department of Commerce published an RFI in September of 2021 on the semiconductor supply chain (86 FR 53031, September 24, 2021).<sup>10</sup> More than 150

# **CHIPS** for AMERICA

responses were received from commenters including from nearly every major semiconductor producer as well as representative companies that consume these products across multiple industry sectors. These responses provided new insights into the complex and global semiconductor supply chain.<sup>11</sup>

To strengthen the U.S. position in semiconductor R&D and manufacturing, Congress authorized a set of programs in Title XCIX of the William M. (Mac) Thornberry National Defense Authorization Act for Fiscal Year 2021, Public Law 116-283, as amended by sections 103 and 105 of the Creating Helpful Incentives to Produce Semiconductors for America Act (CHIPS Act) of 2022 (Pub. L. 117-167, Division A), codified at 15 U.S.C. 4651 et seq. (hereinafter, CHIPS for America Act).

CHIPS for America includes the CHIPS Program Office, responsible for semiconductor incentives, and the CHIPS Research and Development Office, responsible for R&D programs, that both sit within the National Institute of Standards and Technology (NIST) at the Department of Commerce. NIST promotes U.S. innovation and industrial competitiveness by advancing measurement science, standards, and technology in ways that enhance economic security and improve our quality of life. NIST is uniquely positioned to successfully administer the CHIPS for America program because of the bureau's strong relationships with U.S. industries, its deep understanding of the semiconductor ecosystem, and its reputation as fair and trusted.

In 2021, President Biden's American Jobs Plan<sup>12</sup> called for at least \$50 billion to fund this set of programs. As funded by Section 102 of the CHIPS Act of 2022:

• \$39 billion is available for a program to incentivize investment in facilities and equipment in the United States for the fabrication, assembly, testing, advanced packaging, production, or R&D of semiconductors, materials used to manufacture semiconductors, or semiconductor manufacturing equipment.

• \$11 billion is available to support several R&D and infrastructure investments including the establishment of an NSTC and NAPMP, the creation of up to three Manufacturing USA institutes targeting semiconductors, and expansion of NIST's metrology R&D in support of semiconductor and microelectronics R&D.

Under Section 9906(f) of the CHIPS for America Act, the Director of NIST may establish up to three

Manufacturing USA institutes<sup>13</sup> that are focused on semiconductor manufacturing. In addition, the Secretary of Commerce may award financial assistance or other transactions to any Manufacturing USA institute for work relating to semiconductor manufacturing. Such institutes may emphasize the following:<sup>14</sup>

• Research to support the virtualization and automation of maintenance of semiconductor machinery

• Development of new advanced test, assembly, and packaging capabilities

• Developing and deploying educational and skills training curricula needed to support the industry sector and ensure the United States can build and maintain a trusted and predictable talent pipeline.

#### **Request for Information**

The intent of this RFI was to inform the development of up to three Manufacturing USA semiconductor institutes that will strengthen leadership and national resilience of the U.S. semiconductor and microelectronics industry and other industries that rely on microelectronics, through R&D of manufacturing technology, and enhanced EWD.

RFI questions covered major areas about which NIST was seeking comments. They were not intended to limit the topics that may be addressed. Responders were allowed to include any topic believed to have implications for the development of Manufacturing USA semiconductor institute(s), regardless of whether the topic was included in the RFI. In addition, when addressing those topics, responders could choose to address the practices of their organization or a group of organizations with which they are familiar. As desired, responders could also choose to provide information about the type, size, and location of the organization(s). Provision of such information was completely optional and did not affect NIST's consideration.

#### III. RFI RESPONSE OVERVIEW

NIST requested public input to inform the design of, and requirements for, potential Manufacturing USA institutes to strengthen the semiconductor and microelectronics innovation ecosystem, including design, fabrication, advanced test, assembly, and packaging capability. These Manufacturing USA institutes are authorized in the CHIPS for America Act to support

efforts in R&D as well as EWD. That act also provides for the NSTC, the NAPMP, and NIST Metrology R&D supporting measurement science and standards, all of which are to work together in a complementary fashion. Responses to this RFI may inform NIST's development of funding opportunities for federal assistance or other transactions to establish Manufacturing USA semiconductor institute(s).

The RFI was open from October 13, 2022 to December 12, 2022.

#### **RFI Statistics**

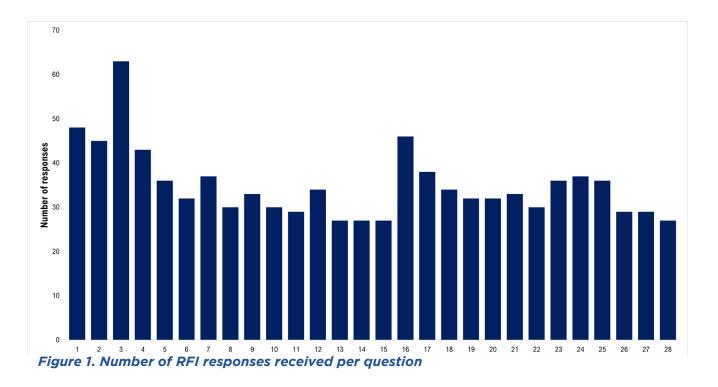

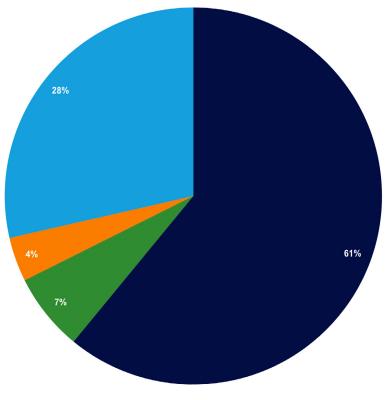

The 28 questions of the RFI addressed five areas: Institute scope; institute structure and governance; strategies for driving co-investment and engagement; education and workforce development; and metrics and success (See Table 1). Figures 1 and 2 provide a snapshot of the number of responses received per question and responses by organization type respectively.

### Key themes across RFI topics

#### Institute Scope

**Institute coordination:** Responders generally viewed the new Manufacturing USA semiconductor institute(s) as complementary to existing ones along with the new R&D investments, and remain aligned with the programmatic purposes of Manufacturing USA. Responders suggested that the new institutes should be transformational, tackling hard problems that bridge the gaps from R&D to full-scale manufacturing. Several responders suggested focus areas or

#### Table 1. RFI topic areas and focus

|                                                                                            |                                                                                              | RFI Areas                                                                                     |                                                                                                |                                                                                                        |

|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Institute Scope                                                                            | Institute Structure<br>and Governance                                                        | Strategies<br>for Driving<br>Co-Investment<br>and Engagement                                  | Education and<br>Workforce<br>Development                                                      | Metrics and<br>Success                                                                                 |

| 1. Coordination<br>with other CHIPS<br>Act-funded R&D<br>efforts                           | 6. Unique con-<br>siderations for<br>semiconductor/<br>microelectronics<br>technology sector | 9. Investment tax<br>credit (ITC) for<br>industry                                             | 16. Supporting<br>workforce and<br>awareness at all<br>educational levels                      | 25. Sector-specific<br>economic compet-<br>itiveness, national<br>security, technol-<br>ogy innovation |

| 2.<br>Complementarity<br>with and non-<br>duplication of<br>existing MFG USA<br>institutes | 7. Risks and ben-<br>efits of "up to<br>three" semicon-<br>ductor institutes                 | 10. Factors influ-<br>encing non-federal<br>co-investment                                     | 17. Engaging full<br>diversity of edu-<br>cation and voca-<br>tional training<br>organizations | 26. Semiconductor<br>institute-spe-<br>cific education<br>and workforce<br>development                 |

| 3. Role for existing<br>MFG USA insti-<br>tutes in semicon-<br>ductor R&D                  | 8. Ensuring<br>stakeholder<br>participation                                                  | 11. Sustaining insti-<br>tute operations<br>in the absence of<br>continued federal<br>support | 18. Ensuring focus<br>and industry<br>priorities                                               | 27. Semiconductor<br>manufactur-<br>ing ecosystem<br>development                                       |

| 4. Scale needed<br>for impact on<br>semiconductor<br>manufacturing<br>innovation           |                                                                                              | 12. Foreign entities                                                                          | 19. Leveraging<br>existing workforce<br>programs                                               | 28. First year considerations                                                                          |

| 5. Appropriate<br>technical scope<br>for impact without<br>duplication                     |                                                                                              | 13. Other federally funded programs                                                           | 20. Success<br>measures                                                                        |                                                                                                        |

|                                                                                            |                                                                                              | 14. Interaction<br>with state and<br>local economic<br>development<br>entities                | 21. Integration<br>of R&D with<br>workforce                                                    |                                                                                                        |

|                                                                                            |                                                                                              | 15. Standards<br>development<br>bodies                                                        | 22. Building a<br>steady pipeline of<br>skilled workers                                        |                                                                                                        |

|                                                                                            |                                                                                              |                                                                                               | 23. Broadening<br>talent base                                                                  |                                                                                                        |

|                                                                                            |                                                                                              |                                                                                               | 24. Education<br>and workforce<br>development<br>mechanisms                                    |                                                                                                        |

**RFI Responders**

■ Industry ■ Academia ■ Government ■ Other

Figure 2. RFI responders by organization type. The government responders included both state and federal. The "Other" category includes responders from Manufacturing USA institutes, non-profits, individuals and all responders who choose to remain anonymous.

themes for the new institutes, such as smart manufacturing and packaging, advanced packaging substrate technology and manufacturing, manufacturing design, and infrastructure to support technology transition to commercial and defense applications. In terms of R&D investments, responders emphasized the importance of non-duplication and complementing existing investments, especially when considering the needs and costs for building additional infrastructure for new semiconductor institutes. It should be noted that this input aligns with the Manufacturing USA authorizing statute,<sup>14</sup> which specifies that new institutes must not substantially duplicate the technology focus of any other Manufacturing USA institute. Responders also stressed relevant collaboration with existing institutes, especially institutes with infrastructure or experience in cross-cutting areas critical to semiconductor manufacturing such as power electronics, flexible electronics, integrated photonics, robotics, and smart manufacturing.

Scope considerations: Responders generally agreed that scoping was key to ensure the impact and success of each new institute and avoid duplication of efforts with existing programs. Responders noted the need for close collaboration and cooperation related to semiconductor R&D initiatives such as the NSTC, NAPMP, and the Department of Defense (DOD) Microelectronics Commons, as well as defining an institute-specific focus that supports the objectives of the CHIPS Act to create impactful ecosystems. In addition to scope-related suggestions, responders also suggested understanding and utilizing synergies with existing and relevant Manufacturing USA institutes and understanding the commonality that exists between defense and commercial industries. They also reiterated the importance of convening industry, small-to-medium enterprises (SMEs), government, and academia to collectively work on the needed innovation, competitiveness, and workforce strategies in the semiconductor and microelectronics space.

**Federal and non-federal investment:** Several responders suggested a range from \$150 million to \$250 million in federal funding for new semiconductor institutes over five years, with a few responders further suggesting federal operational funding should be sustained throughout the lifetime of the institute. A few responders noted, in alignment with requirements

in the Manufacturing USA authorizing statute,<sup>6</sup> that co-investment should be at least 1:1 for the federal dollar match. A few other responders suggested \$250 million per year, with \$125 million per year federal funding and \$125 million per year non-federal cost share and \$600 million over five-years at minimum, and funding levels approaching \$1 billion over fiveyears. Other responses suggested the creation of one large public-private partnership that integrates both microelectronics and advanced packaging technology at a much higher investment level as compared to typical Manufacturing USA institutes, with regional centers established under the Manufacturing USA semiconductor institute(s) in the west, midwest, south, and northeast.

Potential technology focus areas: Several responders favored the RFI-listed potential technology areas of focus and a few others suggested new or alternative topic areas in the scope of an institute. Responders suggested strong partnership and coordination between NSTC and NAPMP on the proposed RFI topic areas to avoid duplication. In terms of coordination with existing Manufacturing USA institutes, responders reiterated the need for relevant collaboration with existing institutes, especially those with infrastructure or experience in cross-cutting areas critical to semiconductor manufacturing. A few responders cautioned relevance of the suggested topic areas to pursue given that the technical objectives of the NSTC and NAPMP have not been established. Related suggestions were to pursue topics broad enough to provide flexibility to the institutes and allow them to align and complement the other Manufacturing USA institutes, NSTC, and NAPMP. Table 2 captures the feedback on the appropriateness of RFI listed scope of work.

#### Table 2. Feedback on the appropriateness of RFI listed scope of work

|                                                                                                                                                                            | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chip-package architectures and<br>co-design of integrated circuits<br>and advanced packaging. May<br>include AI, security, and test<br>methodologies                       | General agreement, additional sub-topics or emphasis suggested; strong<br>partnership and coordination between NSTC and NAPMP emphasized<br>for this topic and addressing co-design, for example an electronic design<br>automation (EDA) coalition of excellence partnering with device designers<br>and package designers                                                                                                                                       |

| Technologies to increase the<br>microelectronics manufacturing<br>productivity of American workers,<br>lower costs, and offset the drastic<br>shortfall of skilled workers | General agreement, additional sub-topics or emphasis suggested;<br>suggestion that this topic must be a part of any initiative whether it is part<br>of the NSTC, NAPMP, or a semiconductor institute and not necessarily<br>a standalone effort; suggestion to leverage workforce development<br>programs in NSTC and NAPMP, to modernize curricula and build<br>awareness of the semiconductor industry                                                         |

| Assembly and test metrologies to<br>develop new analytical equipment<br>and analysis capabilities based<br>upon standards                                                  | General agreement, additional sub-topics or emphasis suggested;<br>consensus to enable interoperability and traceability of fabrication,<br>packaging, and test data from development to manufacturing phases in<br>support of automation; suggestion for NIST metrology efforts to provide<br>advice, guidance, expertise, and coordination in this topic to enable<br>NSTC, NAPMP, and existing Manufacturing USA programs to achieve their<br>respective goals |

| Coding and system software<br>with novel computing paradigms<br>and architectures, including<br>chiplet compatibility with earlier<br>generations                          | Mixed responses, with some sub-topics or emphasis suggested;<br>suggestion that the topic was out-of-scope for semiconductor<br>Manufacturing USA institutes, but within the scope of the NSTC                                                                                                                                                                                                                                                                    |

| Integration of security into packaging, interposers, and/or substrates                                                                                                     | Mixed responses, with some sub-topics or emphasis suggested;<br>suggestion that this topic be an important component of the overall<br>advanced packaging initiatives or be within the scope of NAPMP<br>coalitions of excellence but not as a standalone topic for an institute                                                                                                                                                                                  |

| High density interposers and substrates, incorporating new materials and designs                                                                                           | General agreement, additional sub-topics or emphasis suggested;<br>suggestion that the topic should be an important part of the NSTC<br>and Advanced Packaging Institute that is partnered with relevant<br>Manufacturing USA institutes                                                                                                                                                                                                                          |

| Chiplet-enabled trusted<br>packaging facilities that obviate<br>the need for trusted foundries                                                                             | Mixed responses, with some sub-topics or emphasis suggested; responses<br>either suggesting out-of-scope or should collaborate with NAPMP and<br>NSTC; suggestions include lack of clarity that chiplet-enabled trusted<br>packaging can obviate the need for trusted foundries and more research<br>is warranted                                                                                                                                                 |

| New materials, such as glass<br>for substrates, or compound<br>semiconductors                                                                                              | General agreement, additional sub-topics or emphasis suggested. A few suggested that this topic be part of the scope of NSTC and NAPMP                                                                                                                                                                                                                                                                                                                            |

| Environmental sustainability for semiconductor manufacturing                                                                                                               | General agreement, additional sub-topics or emphasis suggested;<br>suggestions that this topic be part of an overall semiconductor<br>manufacturing mission, not necessarily for a specific institute directive                                                                                                                                                                                                                                                   |

| Analog and gigahertz technology<br>materials and metrology, enabling<br>beyond 5G, the Industrial Internet<br>of Things and Industry 4.0                                   | General agreement, additional sub-topics or emphasis suggested;<br>suggestion to include this topic in both the NSTC and NAPMP goals                                                                                                                                                                                                                                                                                                                              |

| Performance and process modeling and metrology                                                                                                                             | General agreement, additional sub-topics or emphasis suggested;<br>suggestion also included that this topic be part of the advanced<br>packaging ecosystem but not necessarily as a theme for a new institute                                                                                                                                                                                                                                                     |

Criteria for selection: Responders indicated that the impact on U.S. manufacturing was a key criterion in evaluating a chosen focus area, including how an institute in that focus area would address technology gaps, create a runway to launch novel "leapfrog" technologies and grow a domestic ecosystem and economy. There was broad emphasis on advanced packaging or assembly, test, and packaging as having the most disruptive potential and opportunity for renewed U.S technological leadership since integration of various types of chips has become so complex. Responders indicated that the new institutes focused on semiconductor manufacturing innovation should complement existing Manufacturing USA institutes and the NSTC and NAPMP, while cautioning about the lack of scope clarity of the NSTC and NAPMP. Responders also recommended a focus on productivity while reducing the cost of manufacturing semiconductors, with efforts on EWD and underrepresented minorities.

**Technical scope for impact:** Responders' interests fell into six categories, predominantly in advanced packaging and smart manufacturing enabled by AI and new materials. Cross-cutting issues of environmental impact, energy efficiency, and especially EWD were included in several categories, namely: advanced packaging, heterogeneous integration (HI), and substrates; design and simulation, often AIdriven; productivity enhancement and smart manufacturing via early design/digital twins and AI; advanced materials; and metrology and testing.

#### Institute Structure and Governance

Alignment with design principles: Responders agreed that the original national network for manufacturing innovation design principles are aligned with the needs of the semiconductor innovation ecosystems, including the appropriate role for government as a catalyst, not primary stakeholder, and the institutes as hubs connecting innovation ecosystems. However, the responders noted the complexity of the existing relationships and intensity of R&D investments in the mature global ecosystem as unique factors that must be considered in designing the new Manufacturing USA institutes focused on semiconductor manufacturing. Responders also highlighted the importance of plans for sustaining and upgrading any specialized equipment or pilot lines within institutes, given the high capital costs associated with these assets.

Scale of proposed institute(s): The responders had diverse perspectives on the question of how many semiconductor institutes should be established, given that legislation authorizes up to three institutes. However, responders agreed that the typical scale of the existing Manufacturing USA institutes is insufficient to have measurable impact on the capital-intensive semiconductor manufacturing ecosystem. Responders noted that there were benefits to increased geographic coverage with multiple institutes, but also that careful coordination and complementarity of scope was critical to achieving those benefits. Responders also noted that stakeholders may be challenged to navigate membership in multiple institutes and suggested that one "supersized" institute with multiple regional hubs is worth consideration.

#### Structures to secure stakeholder participation:

Most responders agreed that the governance and membership structures for new Manufacturing USA semiconductor institute(s) could largely be modeled on those for existing institutes. Responders agreed that the institute(s) must be industry-led and be inclusive of the broader ecosystem, with low barrier to entry for participation by organizations that serve underrepresented groups. Also noted was the need for easily navigable, multi-year membership agreements with balanced intellectual property (IP) rights consistent with a precompetitive R&D focus.

**Fostering technology transitions:** Responders pointed to the need for close collaboration

within the ecosystem, including with the NSTC, NAPMP, and existing Manufacturing USA institutes to access fabrication facilities, cross-cutting capabilities, and link access to commercialization partners across application areas. Responders also mentioned that the institutes will need to measure more than just advancement of technology readiness, but also the investment and adoption readiness to succeed in transitioning technology.

#### Strategies for Driving Co-Investment and Engagement

**Co-investment value:** Responders generally agree that co-investment by all members in the Manufacturing USA semiconductor institute(s) is important for creating shared value and impact. Responders agreed that cash was the most useful and flexible form of co-investment and should be encouraged. Many responders cited shared access to capital-intensive equipment, fabrication facilities, and novel materials as essential to success, although there were diverse opinions expressed on how to best establish that.

**Co-investment strategy:** Responders were also in agreement that the co-investment strategy for each institute should be structured to encourage and enable robust participation across all stakeholders. Many responders suggested scaling required co-investment based on member type and anticipated commercial benefit, through tiered membership models with different requirements for cash vs. in-kind commitments, as well as distinct IP rights.

**Sustainability:** Many responders noted that a thoughtful co-investment strategy coupled with a solid industry-focused business model should support sustainability. However, responders noted that the institute is likely to need federal support beyond five years, given the long timelines often needed before a return on investment (ROI) is tangible to industry.

**Investment tax credit impact:** Responders were in general agreement that the impact of the investment tax credit for driving industry co-investment in the Manufacturing USA semiconductor institute(s) was promising, yet uncertain at this early stage of enactment.

#### Education and Workforce Development

#### Advanced manufacturing workforce

**development:** Responders generally agreed that the Manufacturing USA semiconductor institute(s) should invest in and support experiential learning opportunities for all educational levels, from primary/ secondary students through university and postgraduate students, along with incumbent workers. The responders suggested that the programming will need to include awareness-building, recruitment, training, and upskilling for both technician and engineering levels. The majority of responses also stressed the importance of outreach at an early stage. The institute(s) must partner with academia and industry stakeholders to revise the curricula and provide hands-on training, build interest in job opportunities in the field, and recruit a pipeline of candidates.

Diversity of education and vocational training:

Responders were generally in agreement that the semiconductor institute(s) should forge a variety of relationships with educational and training organizations to ensure there are sufficient students in the talent pipeline to meet workforce demands. The consensus was that the institute(s) should leverage the existing Manufacturing USA EWD network and work closely with the existing institutes in adjacent fields, establish networks and partnerships via NSTC and NAPMP, and engage with universities, trade schools, and community colleges that have diverse education and vocational training. The responders also emphasized the importance of curriculum updates through co-op and intern programs to provide on-the-job

training that would meet the needs of the industry. Development of a toolkit that addresses educational, certification, and career pathways to close the skills gap in manufacturing was also suggested.

Addressing industry priorities: The responders stressed that strong partnerships with industry members are essential to ensure advanced manufacturing workforce development activities effectively address industry priorities. Suggestions included aligning regional workforce development programs with organizations that already have deep EWD penetration in industry, or rotating industry professionals into community colleges and universities to teach specific classes and courses. A few responses suggested that workforce development activities should correlate with industry roadmapping activities to address skill gaps and competencies needed for advanced manufacturing.

**Complementary partnerships:** Responders suggested institute(s) partner with organizations that have access to existing training facilities and resources as they customize EWD programs for optimal support of their membership and the nation at large. Collaboration with National Science Foundation (NSF) and regional/state programs to leverage existing programs was also suggested.

Measure of Success: Responders suggested that the determination of appropriate metrics will largely depend on the specific programs and projects that the institute chooses to implement. Generally, responders agreed that institutes and NIST as the sponsoring agency of the semiconductor manufacturing institute(s) could assess successful recruitment and retention of a well-trained, diverse workforce. Responders suggested quantitative metrics could capture elements such as diversity statistics on race and gender, number of internship/ apprenticeships, and enrollment in university science, technology, engineering and mathematics (STEM) majors, and

in vocational training. Many responders also suggested that quantitative metrics could be developed for the number of partnerships with universities, industry markets served by institute-developed programs, the number of relevant degrees and certificates awarded, workers placed in semiconductor manufacturing jobs, and the growth of regional job fairs.

**R&D integration with workforce:** Responders suggested strengthening industry and academic partnerships in part through demonstrations of state-of-the-art technology. Suggestions included addressing a need for increased R&D in STEM majors and careers, innovative new graduate curricula and team science training, work-based learning opportunities such as learn and earn programs, internships, and apprenticeships with R&D departments, and integration of R&D activities with education utilizing local leading Manufacturing Extension Partnership (MEP) centers.

Pipeline of skilled workers: Responders suggested several mechanisms to achieve a steady pipeline of skilled workers by assessing industry needs and growing the talent pipeline while also promoting diversity, equity, and inclusion. Suggestions included forming strong partnerships with government, industry, non-profits, and academic stakeholders to develop kindergarten to 12th grade (K-12) or postsecondary educational training programs. Responders also suggested crosspromoting professional and multidisciplinary technical knowledge, skills, and abilities that are needed to revitalize the nation's semiconductor manufacturing. It was noted that these skills are currently held by workers in several different manufacturing and STEM fields, including automotive, aerospace, and transportation. In addition, some responders listed specific job titles and occupations that could transition workers to semiconductor manufacturing.

Broadening the talent base: Responders suggested partnering and tailoring activities with community groups, professional associations, and affinity organizations that have been underrepresented in semiconductor manufacturing. Reaching women and minorities was reiterated as important for the current manufacturing culture. Responders also suggested the institute(s) work closely with industry to ensure a broad talent base is captured, and all community groups, especially those that have been under represented, are empowered and given the opportunity for successful careers. Lastly, outreach in coordination with NSTC and NAPMP was highlighted to effectively leverage federal resources to ensure greatest impact.

Education and workforce development activities: Responders proposed several types of EWD activities to target specific audiences for different training functions. Suggestions included hybrid curricula, hands-on engagement, experiential learning programs, mobile learning lab, accessible job outlook pathways, short courses and certifications, mentor training, and train-thetrainer programs. Most responders agreed that partnerships with other government, academic, and private organizations will help expand outreach, accessibility, and impact of EWD activities. Responders, once again, also mentioned the importance of diversity, equity, and inclusion in all education and workforce training activities.

#### Metrics and Success

**Performance metrics:** Responders agreed on the need to track measures to demonstrate impact of the Manufacturing USA semiconductor institute(s) on U.S. semiconductor manufacturing ecosystems. Several responders suggested aligning metrics with institute objectives, to measure both operational and technical progress and impact on innovation, economic competitiveness, and national security. There were also a few responses suggesting sector-specific metrics like decreased imports of foreign components, raw materials, and services.

Education and workforce development metrics: Responders suggested that impact should be measured across the entire supply chain from component production to finished products for manufacturers involved in the institute. Related metrics potentially include time needed to train workers to achieve proficiency, productivity, gauge training effectiveness, number of internships, technician/trade certificates awarded, degrees awarded, and number of hires by the semiconductor industry and its supporting ecosystem.

Metrics supporting U.S. semiconductor manufacturing ecosystem: Responders generally favored impact metrics measured by commercial activities such as number of startups in the institute field, jobs added per year in the related industrial sector. number of new products introduced with semiconductor technology, sales volume related to technology development facilitated by the institute, patents and patent-protected sales for technology generated by the institute, commercial viability and institute facilitated deployment of technologies, and expansion of domestic manufacturing capacity. Several responders also suggested technology-specific output metrics such as wafers per month or number of new chips built that use advanced substrates developed and used at the new institute. For broader impact, responders suggested surveying semiconductor companies and members of the institutes while simultaneously considering other global semiconductor institution metrics to best evaluate the performance and impact in establishing and expanding the ecosystem related to knowledge transfer, collaboration, pipeline and job creation, safety, quality, delivery, and growth.

**First-year success metrics:** Several responders suggested year-one success metrics such as institute bylaws established with initial member participation, paid company

membership dues that represent at least a 50% market share in the markets the institute aims to influence, second-year dues payments received from at least 90% of first-year members, committed state funding for over five years, and member input significantly guiding institute value proposition, technology roadmap, and business plan and budget. Responders also suggested key considerations while setting up the new institutes such as defining clear scope and mission, capitalizing on existing industry and public and private partnerships, and finalizing key institute operational documents.

**Forms of support:** Responders suggested establishing clear governance and interactions with NSTC and NAPMP and partnership with existing Manufacturing USA institutes. Support from NIST, the NAPMP and NSTC (including governance structures for those programs), and partnership with existing Manufacturing USA institutes are essential for early success. Other suggestions addressed developing a strategic plan and framework in alignment with Manufacturing USA and Department of Commerce strategic goals and leveraging other federal agencies and state and local government interests.

#### IV. RFI CATEGORIAL RESPONSES

#### **Institute Scope**

### 1. Coordination with other CHIPS-Act-funded R&D efforts

*RFI Question 1:* The Manufacturing USA semiconductor institute program is one component of an \$11 billion R&D effort that includes the National Advanced Packaging Manufacturing Program, the National Semiconductor Technology Center and the NIST Metrology R&D. The entire R&D program is intended to be interconnected and comprehensive, with no gaps and minimal redundancy, to position the United States for technology and workforce leadership in the semiconductor and

microelectronics sector for the long-term prosperity of the nation. Additionally, the Manufacturing USA authorizing statute specifies that new institutes must not substantially duplicate the technology focus of any other Manufacturing USA institute. From your perspective, what role do you envision for new Manufacturing USA semiconductor institutes that will best complement the other R&D investments and remain consistent with the programmatic purposes of Manufacturing USA? Since the Secretary of Commerce may award financial assistance to any existing Manufacturing USA institutes for work relating to semiconductor manufacturing, what role do you envision for existing, federally sponsored Manufacturing USA institutes with respect to semiconductor manufacturing?

#### RFI Question 1 Response Summary:

The majorityof the responders for this question viewed the new Manufacturing USA semiconductor institute(s) to complement existing and new R&D investments and remain aligned with the programmatic purposes of Manufacturing USA. Many responses specifically suggested potential focus areas and priorities for the new institutes, related R&D investments, and coordination aspects to consider alongside already-existing Manufacturing USA institutes.

In terms of priorities, multiple responses suggested that the new institutes should be transformational, tackling hard problems that bridge the gaps from R&D to fullscale manufacturing. The new institutes should grow domestic capabilities for semiconductors, thus reducing dependence on the global supply chain, and focus on next-generation manufacturing technology. Several responses reiterated the specific objectives of the CHIPS Act itself as central to the mission of the new institutes, such as reshoring semiconductor manufacturing, focusing on workforce development, and establishing leadership in the security of

the semiconductor supply chain. Several responses also suggested potential focus areas or themes for the new institutes such as advanced smart manufacturing and packaging, advanced packaging substrate technology and manufacturing, and infrastructure to support technology transition to commercial and defense applications. In addition, a few responses generally agreed to the possible themes as listed in the RFI as scope for each of the new Manufacturing USA institutes with a priority to improve domestic microelectronics manufacturing productivity and America's economic competitiveness overall. Several responses especially emphasized specific capabilities for the new institutes such as: wafer level HI, innovative interconnects, nanoscale metrology, intelligent design, assembly, packaging and test methodologies, standards, cyber security, certification, workforce development, networking and streamlined contracting, semiconductor chip manufacturing lifecycle, supply chain gaps, end-to-end digital thread across semiconductor and microelectronics design and AI-enabled advanced digital simulation.

In terms of semiconductor related R&D investments, several responses emphasized not duplicating but instead complementing existing investments and building additional infrastructure for the new semiconductor Institutes. There were suggestions that the new institute(s) should consider the activities of other existing Manufacturing USA institutes as well as other initiatives funded by DOD and other federal agencies. In relation to coordination with existing Manufacturing USA institutes, several responses repeated the need for meaningful collaboration with existing institutes, especially those with infrastructure or experience in cross-cutting areas in semiconductor manufacturing such as advanced packaging, power electronics, flexible electronics, integrated photonics, robotics, and smart manufacturing.

#### 2. Complementarity with and non-duplication of existing Manufacturing USA institutes

*RFI Question 2:* The technological breadth of innovation in semiconductors and microelectronics is likely larger than can be served by any single Manufacturing USA institute. Therefore, each Manufacturing USA semiconductor institute should have an appropriate scope to ensure that each institute is impactful and does not duplicate efforts of other programs. Historically, institutes in the current network of existing Manufacturing USA institutes have generally been funded for an initial 5 years at \$150 million to \$600 million, including federal funding and cost-sharing (co-investment) from non-federal partners. What would be the ideal scope and corresponding financial investment from federal and nonfederal partners, for a Manufacturing USA semiconductor institute to achieve the needed impact on competitiveness?

#### RFI Question 2 Response Summary:

The consensus from the responders to this guestion was that, given the technological breadth of innovation in semiconductors and microelectronics, appropriate scoping (and avoiding duplication of efforts with existing programs) was key to ensuring the impact and success of each new institute. Several responses suggested the ideal scope and focus for new semiconductor institutes. Suggestions included advanced packaging and smart manufacturing, substrate technology development, design virtualization and visualization, hardware design simplification, materials and wafer processing, three-dimensional heterogeneous integration (3DHI) analog semiconductors, wide and ultra-wide bandgap semiconductor fabrication, semiconductor workforce development, metrology focus, scalable assembly tools, etc. A few responses also noted the need for close collaboration and cooperation related to R&D initiatives such as the NSTC, NAPMP, and DOD Microelectronics Commons,

and defined an institute-specific focus to address the objectives of the CHIPS Act and create impactful ecosystems. Several responses also suggested understanding and utilizing synergies with existing and relevant Manufacturing USA institutes, understanding the commonality that exists between defense and commercial industries, and reiterated the importance to convene industry, SMEs, government, and academia to collectively work on the needed innovation, competitiveness, and workforce strategies in the semiconductor and microelectronics space.

Other relevant scope-related coordination comments included leveraging existing semiconductor facilities and equipment, generating open source technology within the industry, building prototype hardware or strongly support building hardware with cost-effective end-to-end prototyping to manufacturing, investigating new methods to form reliable interconnects, establishing an open/neutral semiconductor and microelectronics marketplace to expedite and reduce cost for hardware/ prototype production and services across the end-to-end digital thread to facilitate commercialization, emphasizing hands-on techniques and expertise for semiconductor workforce training and creating a national network of pilot line resources.

In terms of corresponding federal investments, several responses ranged from \$150 to \$250 million for new semiconductor institutes over five years, with a few responses suggesting federal operational funding should be sustained throughout the lifetime of the institute. A few responses noted that the federal cost share should be at least 1:1. Other responses suggested \$250 million annually, comprising half from federal funding and the other half from nonfederal cost share and \$600 million over five-years at minimum and funding levels approaching \$1 billion over five-years. There were also responses suggesting the creation of one large public-private partnership

that integrates both microelectronics and advanced packaging technology at a much higher investment level as compared to typical Manufacturing USA institutes, and establishing four regional centers under the Manufacturing USA semiconductor institute(s) in the west, midwest, south, and northeast of the country. Another suggestion proposed a \$250 million federal investment over five years to expand existing Manufacturing USA efforts in smart manufacturing, cybersecurity, robotics, and digital transformation within semiconductor manufacturing. There was a suggestion for institute cost to be one-third from federal funding, one-third from state funding and one-third from industrial and academic institutions

### **3.** Role for existing Manufacturing USA institutes in semiconductor R&D

*RFI Question 3:* Potential technology areas of focus that could be addressed by the Manufacturing USA semiconductor institutes to complement the National Advanced Packaging Manufacturing Program and the National Semiconductor Technology Center in Question 1 are listed below. What are your thoughts on the appropriateness of each for the scope of work for a Manufacturing USA semiconductor institute? What other topics should be included in the scope of an institute?

- Chip-package architectures and codesign of integrated circuits and advanced packaging. May include AI, security, test methodologies, etc.

- Technologies to increase the microelectronics manufacturing productivity of American workers, lower costs and offset the drastic shortfall of skilled workers

- Assembly and test metrologies to develop new analytical equipment and analysis capabilities based upon standards

- Coding and system software with novel computing paradigms and

architectures, including chiplet compatibility with earlier generations

- Integration of security into packaging, interposers and/or substrates

- High density interposers and substrates, incorporating new materials and designs

- Chiplet-enabled trusted packaging facilities that obviate the need for trusted foundries

- New materials, such as glass for substrates, or compound semiconductors

- Environmental sustainability for semiconductor manufacturing

- Analog and gigahertz technology materials and metrology, enabling beyond 5G, the Industrial Internet of Things and Industry 4.0

- Performance and process modeling and metrology

#### RFI Question 3 Response Summary:

The majority of the responders to this question were in favor of the potential technology areas of focus proposed in the RFI. Of those responses, more than 40 came from industry and included specific recommendations on the focus and scope of these technology areas. There were also several responses that suggested new or alternative topic areas.

a. Chip-package architectures and co-design of integrated circuits and advanced packaging. May include artificial intelligence, security, test methodologies, etc.

There was general agreement for an institute to support a diverse set of AI, communications, sensing, and networking applications. Suggested sub-topics included: architectures for security-confidential computing, data integrity, privacy, and data attestation; thermal management based on materials and electrical conductivity; package manufacturing including particle defect inspection and three-dimensional (3D) packaging; computational lithography and process-informed lithography; AI for lithography, tools for design productivity, virtual fabrication-tools for manufacturing productivity; architectures optimized for guantum materials and devices, photonic integrated circuits, and radio frequency (RF) and higher frequency applications; harsh environment hardening via novel packaging and hetero-integration driven by AI-enhanced system partitioning; advancing and coordinating hetrogenerous intergration capabilities in the areas of standards, verification, packaging, and validation capabilities; co-design coupled with accurate chip-package interactions through modeling and simulation of 3DHI architectures for harsh environments; codesigned integrated circuits for signal integrity, thermal, optical, and mechanical properties; post-assembly and postpackaging repair and reconfiguration to support defect and variation tolerance; heterogeneous processing near memory and storage architectures for data/media analytics applications; reconfigurable fabrics for hardware obfuscation and secure split manufacturing; carbon nanotubes; and highperformance computing.

A few comments suggested addressing co-design by an EDA coalition of excellence partnering with device designers and package designers alongside strong partnership and coordination between NSTC and NAPMP.

b. Technologies to increase the microelectronics manufacturing productivity of American workers, lower costs and offset the drastic shortfall of skilled workers

Several comments supported increasing American microelectronics manufacturing productivity, lowering costs, and addressing the drastic shortfall of skilled workers. Suggested sub-topics included: digital twins focusing on big data analytics for manufacturing; testing including virtualization and maintenance automation for productivity; multi-project wafers to

provide access to high-quality materials and devices; leveraging co-design of automated manufacturing equipment within the prototype; AI-enhanced co-design for microelectronics; front-end fabrication and back-end advanced packaging technology to develop tools and techniques that improve efficiency and maximize ROI, lower costs, and maximize American worker efficiency; online training classes and industry-supported certifications to include additive, digital twins, automation, cyber security, AI, augmented reality (AR), virtual reality (VR), advanced analytics, sensors, machine learning, robotics, computing, and communications; and automation of the entire end-to-end process including design, manufacturing, testing, and packaging.

A few responses suggested that while productivity, automation, and smart manufacturing methods must be a part of any initiative (whether part of NSTC, NAPMP or Manufacturing USA network), the topic addressing the shortfall of skilled workers should not be a standalone effort for a semiconductor institute. Leveraging workforce development programs in NSTC and NAPMP were also suggested to modernize curricula and build awareness of the semiconductor industry.

c. Assembly and test metrologies to develop new analytical equipment and analysis capabilities based upon standards

There was general agreement for this topic to enable interoperability and traceability of fabrication, packaging, and test data from development to manufacturing phases through automation. Suggested subtopics included: novel assembly and test metrologies, automated testing of advanced microelectronic packaging, infrastructure for flexible, comprehensive, automatic post-assembly and in-field testing and characterization, user-friendly interface, data analysis, and visualization tools; new advanced packaging technology approaches for wafer stacking and die-on-die or dieon-wafer assembly and new approaches to maintaining signal integrity while connecting heterogeneous devices; in-line and final test methodologies and equipment; new metrologies to maximize yield and binning; screening 3DHI analog semiconductors; non-contact and non-destructive test metrologies; advanced testing capability that matches feature scaling; and automated testing of advanced microelectronic packaging.

A few responses suggested the NIST metrology program provide advice, guidance, expertise, and coordination in this area to enable NSTC, NAPMP, and existing Manufacturing USA programs to achieve their respective goals.

d. Coding and system software with novel computing paradigms and architectures, including chiplet compatibility with earlier generations

This topic generated mixed responses. Responses in favor included the following: relevant significance in advancing 5G and successor wireless technologies; software and novel computing paradigms and architectures for 3DHI analog semiconductors; expand the availability of design and enablement tools; develop chiplet or 3DHI modeling methodology to optimize across electrical, thermal, electromagnetics, and related areas; development of prognostics and health management capabilities down to the chip level; and an open chiplet ecosystem to drive to a standardized open chiplet architecture and fabrication, etc.

A few responses suggested that the topic was out-of-scope for semiconductor Manufacturing USA institutes, but within the scope of the NSTC.

#### e. Integration of security into packaging, interposers and/or substrates

Several responses agreed with integration of security into packaging, interposers and/or substrates. Suggested sub-topics included: anti-tamper enclosures to secure multiplechip modules, modular and composable

security solutions; trusted anchors, novel chiplet design and partitioning, and novel packaging processes; embedded security features in 3DHI analog semiconductors; advancements in lithography capability critical for substrates to address next generation high-density and device integration requirements; and physical product protections, anti-tamper, secure packaging, anti-reverse engineering, hardware locking self-destruction, digital thread, cyber resiliency, in-field reconfigurability and edge processing.

A few responses noted that while this topic is an important component of overall advanced packaging initiatives and should be within the scope of NAPMP coalitions of excellence, it should not serve as a standalone topic for an institute.

#### f. High density interposers and substrates, incorporating new materials and designs

There were several responses in favor of this topic. Suggested sub-topics included: reconfigurable interposers for reusability, defect/variation tolerance, and isolation; monolithic 3D heterogeneous architectures; new rigid 3D substrate technologies to provide a significant edge in terms of reduced loss, improved performance, increased reliability, thermal management, and cost; new advanced test, assembly, and packaging capabilities for HI; interposer developments to leverage existing and future small pitch die with higher power requirements; reference design libraries for interposer design; development of novel interconnect methodologies that are equal to or better than bump technologies and wire bond capabilities; and manufacturingfocused hardware effort to support bringing substrates and laminates in domestic manufacturing.

A few responses suggested that the topic should be an important part of NAPMP as part of an Advanced Packaging Institute that would partner with any relevant

#### Manufacturing USA institutes.

g. Chiplet-enabled trusted packaging facilities that obviate the need for trusted foundries

This topic generated mixed responses. Suggested sub-topics included: a need to add and upgrade trusted power semiconductor packaging facilities for military applications; the value in embedding security features in 3DHI analog semiconductors which are tightly integrated with and supply communications and power to digital chiplets such that the digital chiplets do not need to be fabricated in trusted foundries; chiplet architectures can be more prone to security threats from side channel attacks due to signals exiting the chiplets; focus on establishing the facility first, then establish trusted accreditation; focus on non-silicon compound semiconductor materials; the importance of compound semiconductors critical for defense and commercial applications, including gallium nitride (GaN), gallium arsenide (GaAs), indium phosphide (InP), silicon-germanium (SiGe), and others emerging aluminum gallium nitride (AlGaN), scandium-doped aluminum nitride (ScAIN), indium gallium arsenide (InGaAs), and gallium oxide compounds; development of high thermal conductivity materials to be used internally and externally to the device; multi-material additive manufacturing envisioned to create all levels of packaging; new dielectric and thin film tools and processes; glass as a critical area for low-loss RF systems, and the desire for additional onshore manufacturing for glass substrates: investment in reliable and sustainable sourcing for critical materials; enabling low-cost equipment to meet environmental regulations for air, water, and solid waste treatment; and chiplet standards such as Universal Chiplet Interconnect Express (UCle) offer an opportunity for standardized packaging and trusted packaging facilities.

A few responses either suggested this topic was out of scope for Manufacturing USA institutes and they should, instead, collaborate with relevant centers of excellence in the NAPMP and NSTC. There was a suggestion that the chipletenabled trusted packaging facilities is best integrated into manufacturing lines but the associated costs with setting up and operating such a facility are beyond the budget for a Manufacturing USA institute. A few responses suggested that chipletenabled trusted packaging may not obviate the need for trusted foundries and more research is warranted.

#### h. New materials, such as glass for substrates, or compound semiconductors