## Microfabricated Surface Electrode Ion Traps

F. Benito, B. Tabakov<sup>†</sup>, M. G. Blain, R. Cook<sup>†</sup>, A. A. Cruz-Cabrera, M. Descour, A. R. Ellis, L. Fang, K. M. Fortier, W. L. Gordy, R. A. Haltli, C. Highstrete, J. J. Hudgens, S. A. Kemme, T. L. Lindgren, D. L. Moehring, C. Y. Nakakura, M. E. Smith, J. E. Stevens, D. L. Stick, C. P. Tigges

Sandia National Laboratories, PO Box 5800 MS 1082, Albuquerque, NM 87185-1082

<sup>†</sup> Center for Quantum Information and Control, University of New Mexico, MSC 07–4220, Albuquerque, NM 87131-0001

# Sandia National Laboratories is a multi-program laboratory managed and operated by Sandia Corporation, for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-AC04-94AL85000

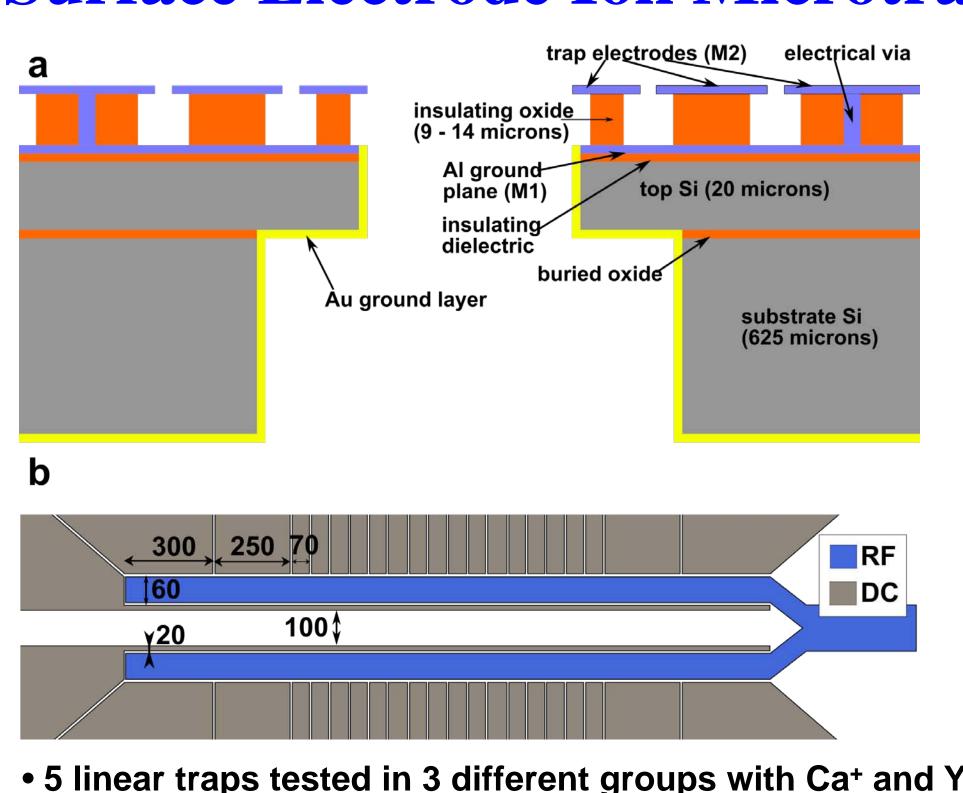

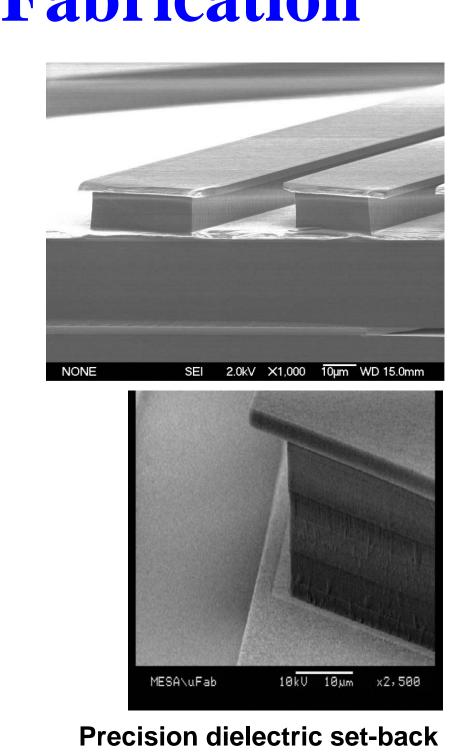

#### Surface Electrode Ion Microtrap Fabrication

routing will be invisible to ion.

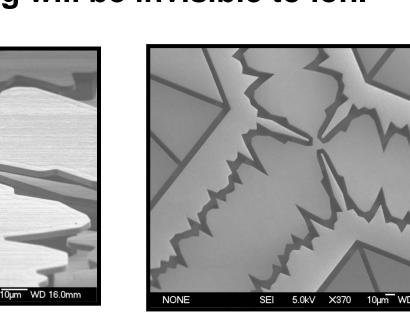

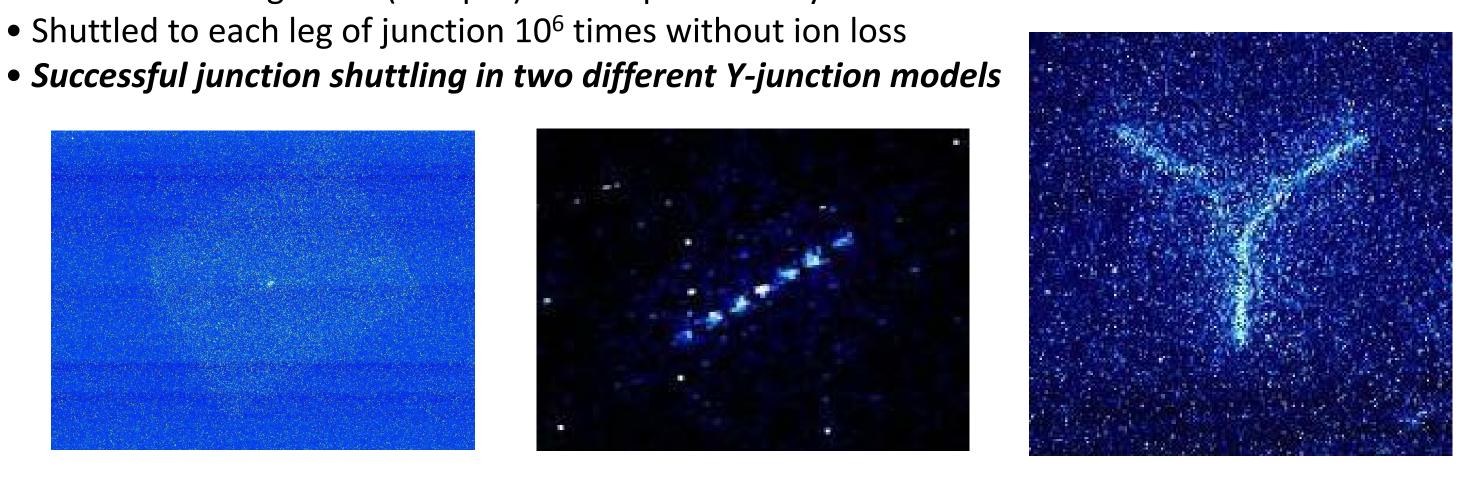

Image of a trapped ion -

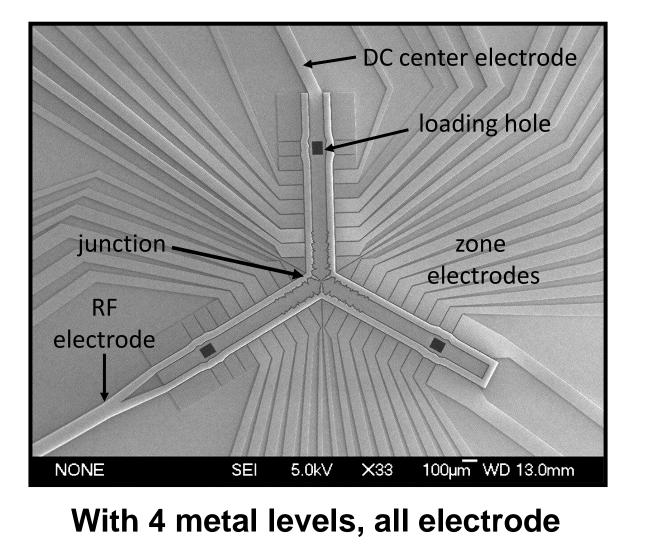

Junction trap

• Shuttled ion single axis (830 μm) - 10<sup>5</sup> repeat fidelity

• Shuttled to each leg of junction 10<sup>6</sup> times without ion loss

Trapped single and multiple ions

loading hole is

illuminated by the oven

Image of multiple ions trapped within the loading hole

Time lapse image in the junction - a single ion moving up each leg

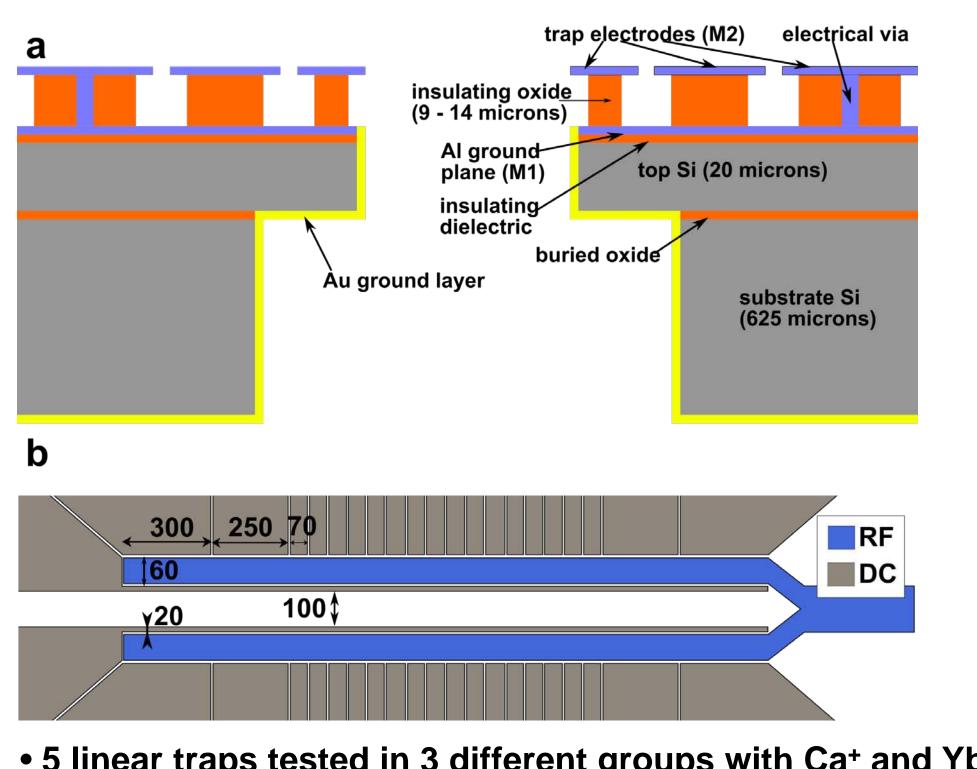

• 5 linear traps tested in 3 different groups with Ca+ and Yb+ [arXiv:1008.0990v1].

### 4 level metal

#### **Development - Four metal layer process:**

- Routing of RF and Crossing of DC electrodes is required away from trapping regions

- Allows for interior RF/DC electrodes to be wired (e.g. ring trap)

- Simplifies simulations by eliminated need to model effect of leads

- DC lead crossings below M4 electrode level and above M1 ground • RF routing in stripline configuration with RF, below trap electrode level

- GND W via

M1, GND

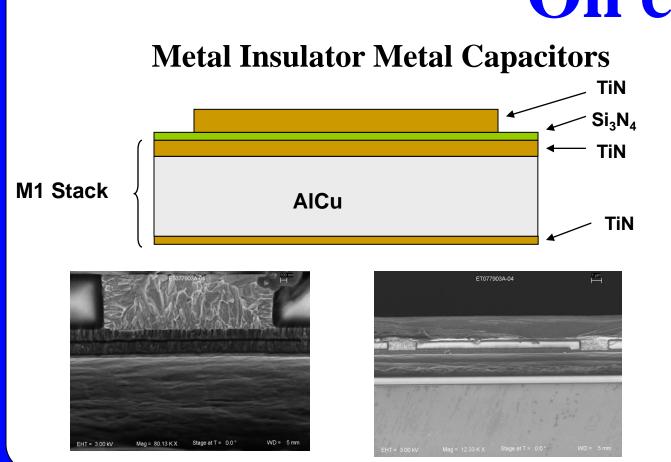

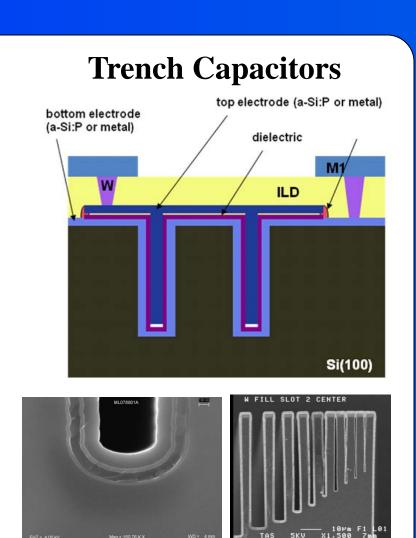

## On chip capacitors

- Higher capacitance density for trench capacitors (94.3 fF/µm<sup>2</sup> vs. 1.3 fF/ $\mu$ m<sup>2</sup>).

- Capacitors are located within microns of DC electrode.

- 1nF trench capacitor is about the size of an electrode

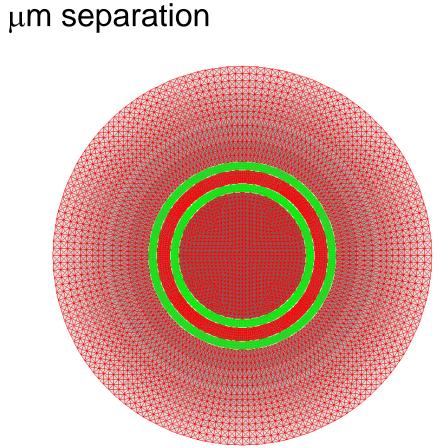

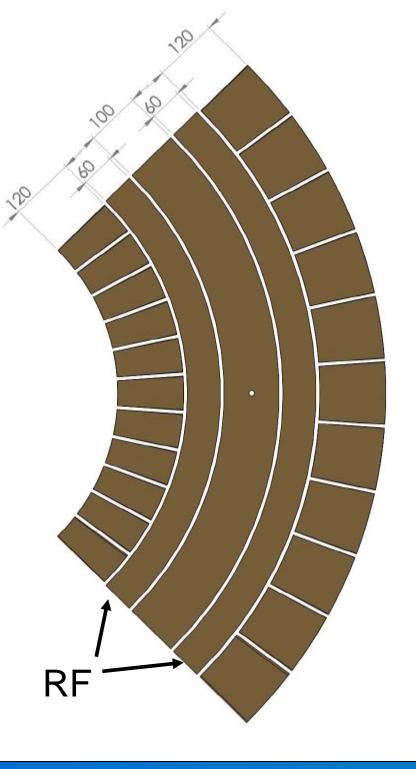

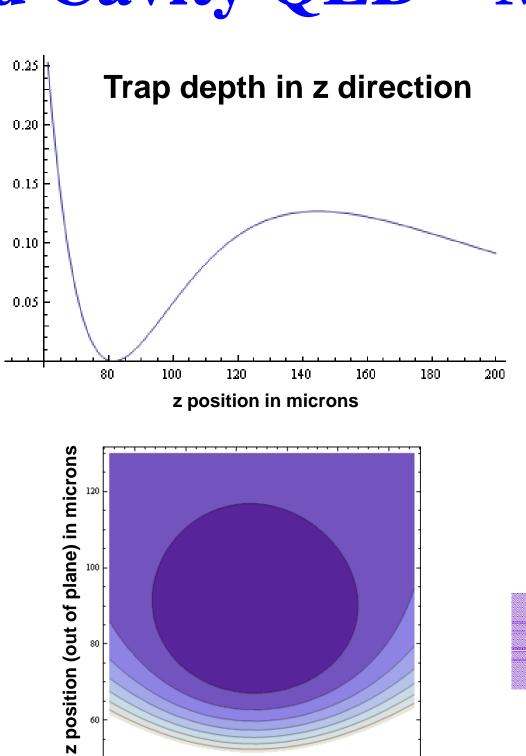

# Ring Traps and Cavity QED – MQCO collaboration

#### Ring Trap

Requires 4 metal level fabrication

axial variation

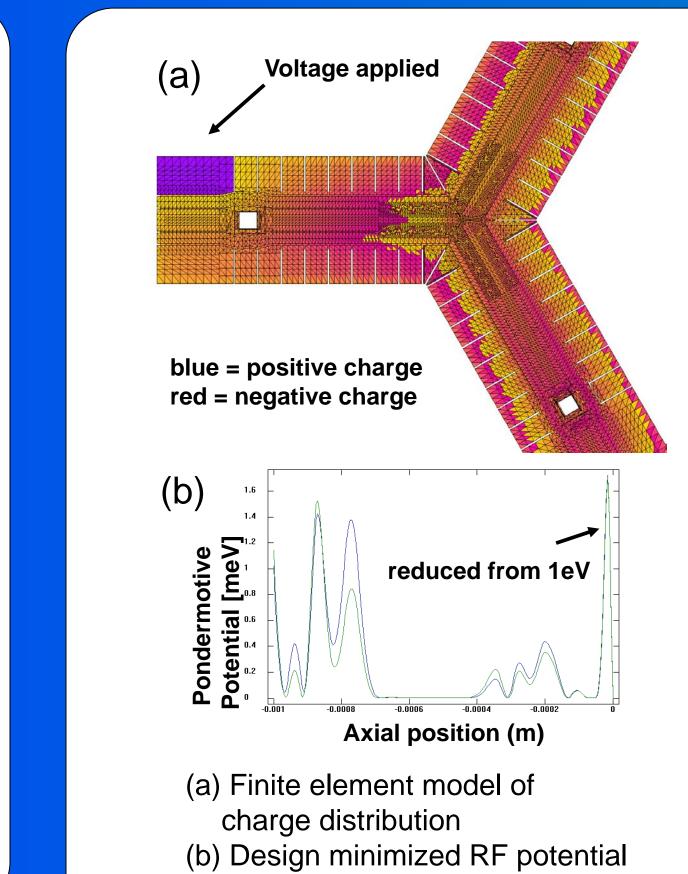

- CPO simulation for barium ions RF drive frequency of 40 MHz,

- 300 V amplitude

- 624 micron radius ring of ions • 60 μm wide RF electrodes, 100

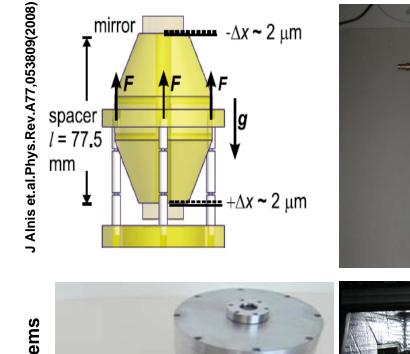

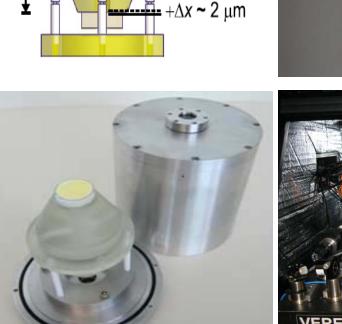

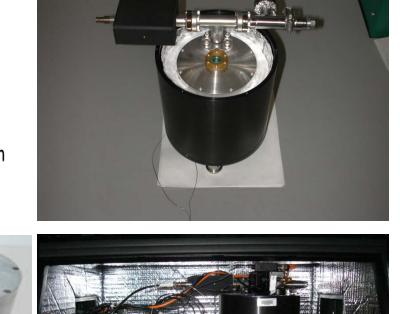

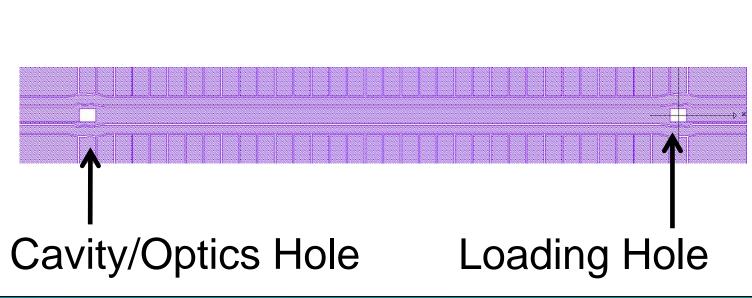

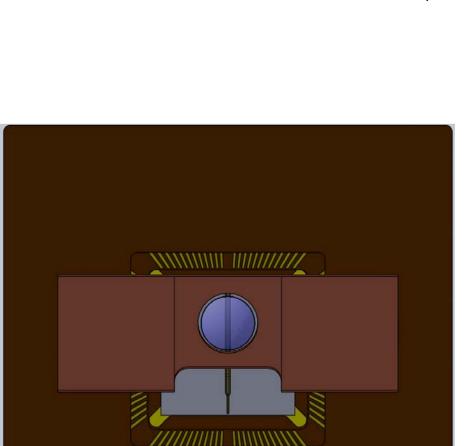

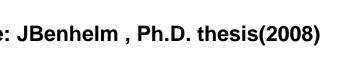

## **Cavity QED Trap**

- Integrate with linear trap

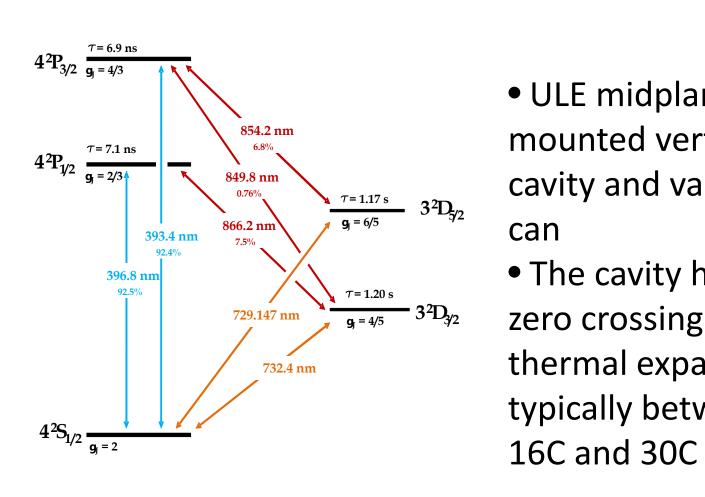

- Sandia will test with Yb+

- Mount registered to Si chip Initial cavity design for Yb+

- •Length = 1 mm

- •Finesse ≈ 4000

- $C_1 = 0.23$

- •% Light Collected = 13.73

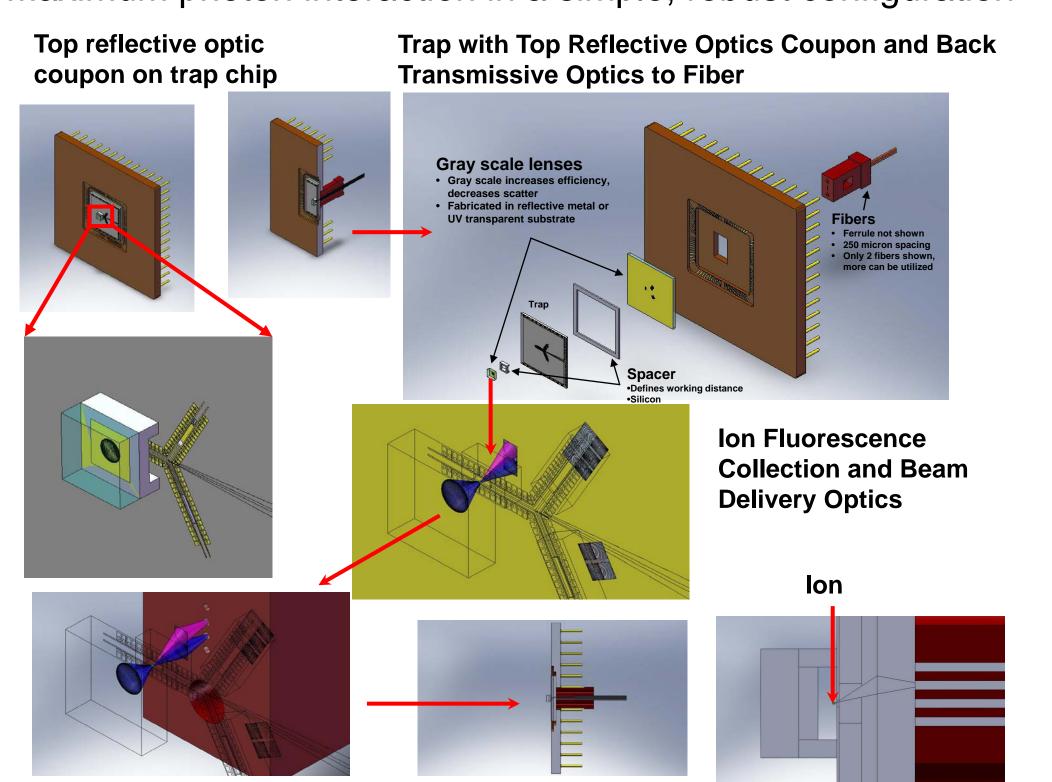

## **Integrated Diffractive and Micro Optics**

#### Can realize transmissive and/or reflective integrated optics

- Off-axis capability → dense optic arrays with 100% fill factor

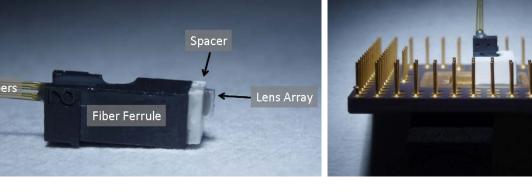

- Entire lens set is aligned to ions and in-vacuum fiber connector

- Maximum photon interaction in a simple, robust configuration

#### **Existing Sandia Capabilities**

- Diffractive Optical Element (DOE) arrays in fused silica with 100% fill factor

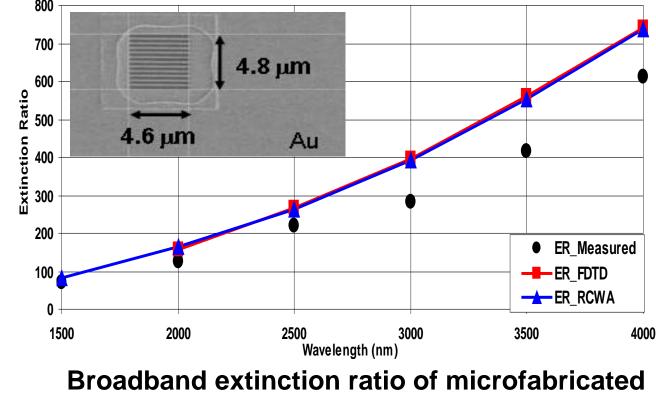

- Fused silica and lithium fluoride polarizers with extinction ratios > 100:1

- Microwaveplates with 9.4° rms variation across broad MWIR band

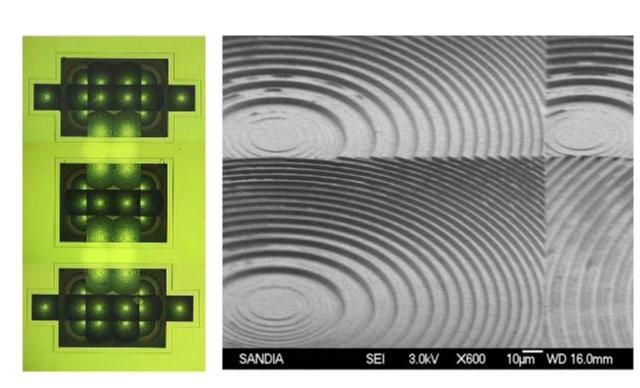

Sandia DOE array in fused silica with 100% fill-factor Optical microscope (L) and SEM (R) images

#### Milestones

- Fabricated 8-level F/1 lenses with focused spot diameters < 1micron at 397 nm

- Multi-fiber feed-throughs and in-vacuum connectors survive bake-out and maintain ultra-high vacuum

polarizer in fused silica

G.R. Brady et al. arXiv:1008.2977v1, accepted to Applied Physics B

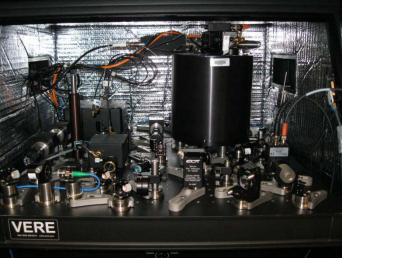

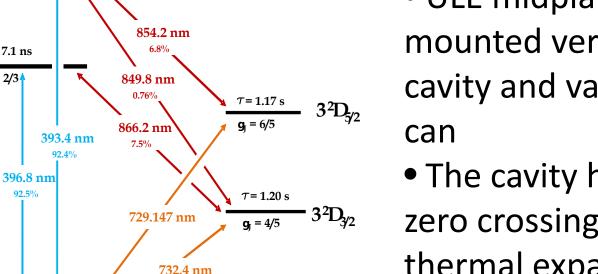

729nm ECDL with a narrow linewidth