# Silicon Nanowires for Non-Volatile Memory

**PROJECT LEADER:**

Curt A. Richter (NIST)

COLLABORATORS:

Xiaoxiao Zhu, Qiliang Li (George Mason University and NIST); Dimitris E. Ioannou (George Mason University); Diefeng Gu, Helmut Baumgart (Old Dominion College and Applied Research Center); John E. Bonevich, John S. Suehle (NIST)

## **G O A L**

To advance fabrication and measurement approaches for silicon nanowire non-volatile memory.

### **KEY ACCOMPLISHMENTS**

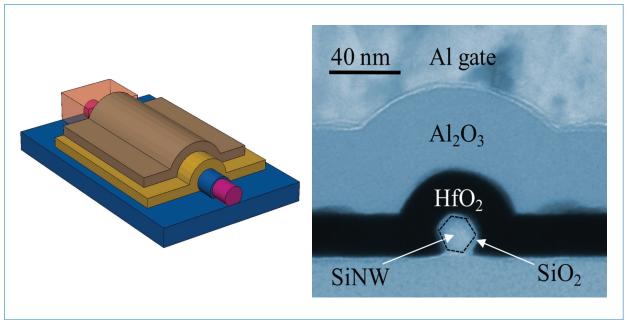

Fabricated novel non-volatile memory cells with silicon nanowire channels and  $Al_2O_3/HfO_2/SiO_2$  gate dielectric storage stacks.

Demonstrated that silicon nanowire transistors with charge trapping dielectric stacks show promise for high speed operation.

#### **KEY NANOFAB PROCESS**

Growth of silicon nanowires in predefined locations by low pressure chemical vapor deposition.

#### REFERENCE

Fabrication, characterization and simulation of high performance Si nanowire-based non-volatile memory cells, X. Zhu, Q. Li, D. Ioannou, D. Gu, J. E. Bonevich, H. Baumgart, J. Suehle, and C. A. Richter, *Nanotechnology* **22**, 254020 (2011).