US011557708B2

# (12) United States Patent

Rufenacht et al.

#### (54) JOSEPHSON VOLTAGE STANDARD

(71) Applicant: Government of the United States of America, as represented by the Secretary of Commerce, Gaithersburg, MD (US)

(72) Inventors: Alain Rufenacht, Longmont, CO (US);

Nathan Edward Flowers-Jacobs,

Boulder, CO (US); Anna Rose

Elizabeth Fox, Boulder, CO (US);

Samuel Paul Benz, Superior, CO (US);

Paul David Dresselhaus. Louisville.

CO (US)

(73) Assignee: GOVERNMENT OF THE UNITED STATES OF AMERICA, AS REPRESENTED BY THE SECRETARY OF COMMERCE,

Gaithersburg, MD (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 440 days.

(21) Appl. No.: 16/843,249

(22) Filed: Apr. 8, 2020

(65) Prior Publication Data

US 2020/0373475 A1 Nov. 26, 2020

#### Related U.S. Application Data

- (60) Provisional application No. 62/850,756, filed on May 21, 2019.

- (51) Int. Cl. H01L 39/06 (2006.01) H01L 39/02 (2006.01) (Continued)

- (52) U.S. CI. CPC .............. H01L 39/06 (2013.01); G01R 35/007 (2013.01); H01L 39/025 (2013.01); H01L 39/2493 (2013.01); H03K 17/92 (2013.01)

## (10) Patent No.: US 11,557,708 B2

(45) **Date of Patent: Jan. 17, 2023**

#### (58) Field of Classification Search

CPC ..... G01R 35/007; G01R 35/005; H01L 39/06; H01L 39/025; H01L 39/2493; H01L 39/223

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

5,565,866 A 5,812,078 A 10/1996 Hamilton et al. 9/1998 Przybysz et al. (Continued)

#### OTHER PUBLICATIONS

Hamilton, C.A., et al., "Josephson D/A Converter with Fundamental Accuracy", IEEE Transactions of Instrumentation and Measurement, 1995, p. 223-225, vol. 44 No. 2.

(Continued)

Primary Examiner — Lee E Rodak

Assistant Examiner — Brent J Andrews

(74) Attorney, Agent, or Firm — Office of Chief Counsel for National Institute of Standards and Technology

#### (57) ABSTRACT

A Josephson voltage standard includes: electrical conductors that receive bias currents and radiofrequency biases; a first Josephson junction array that: includes a first Josephson junction and produces a first voltage reference from the first bias current and the third bias current; a second Josephson junction array in electrical communication with the first Josephson junction array and that: includes a second Josephson junction; receives the second bias current; receives the third bias current; receives the second radiofrequency bias; and produces a second voltage reference from the second bias current and the third bias current; a first voltage reference output tap in electrical communication with the first Josephson junction array and that receives the first voltage reference from the first Josephson junction array such that the first voltage reference is electrically available at the first voltage reference output tap; and a second voltage reference output tap.

#### 18 Claims, 38 Drawing Sheets

| (51) | Int. Cl.   |           |

|------|------------|-----------|

|      | H01L 39/24 | (2006.01) |

|      | G01R 35/00 | (2006.01) |

|      | H03K 17/92 | (2006.01) |

#### (56)References Cited

#### U.S. PATENT DOCUMENTS

| 6,236,344    |     | 5/2001  | Benz et al. |             |

|--------------|-----|---------|-------------|-------------|

| 7,424,841    | B2  | 9/2008  | Liu         |             |

| 7,809,518    | B2  | 10/2010 | Zhu et al.  |             |

| 2003/0218164 | A1* | 11/2003 | Yamamori    | H01L 39/223 |

|              |     |         |             | 257/31      |

| 2010/0148757 | A1* | 6/2010  | Zhu         | G01R 35/005 |

|              |     |         |             | 324/130     |

|              |     |         |             |             |

### OTHER PUBLICATIONS

Dresselhaus, P.D., et al., "10 Volt Programmable Josephson Voltage Standard Circuits Using NbSi-Barrier Junctions", IEEE Transations of Applied Superconductivity, 2011, p. 693-696, vol. 21 No. 3.

Rufenacht, A., et al., "Impact of the Latest Generation of Josephson Voltage Standards in AC and DC electric Metrology", Metrologia, 2018, p. S152-S173, vol. 55.

Rufenacht, A., et al., "Automated Direct Comparison of Two Cryocooled 10 Volt Programmable Josephson Voltage Standards", Metrologia, 2018, p. 585-596, vol. 55.

Overney, R., et al., "Josephson-Based Full Digital Bridge for High-Accuracy Impedance Comparisons", Metrologia, 2016, p.

High-Accuracy Impedance Comparisons", Metrologia, 2016, p. 1045-1053, vol. 53.

Flowers-Jacobs, N.E., et al., "Two-Volt Josephson Arbitrary Wave-form Synthesizer Using Wilkinson Dividers" IEEE Transactions on Applied Superconductivity, 2016, p. 1400207, vol. 26 No. 6. Klushin, A.M., et al., "High-Temperature Superconductor Joseph-son Junctions for Voltage Standards", Physics of the Solid State,

2016, p. 2196-2202, vol. 58 No. 11.

Kvarz, "Measure Voltage H4-21 Based on Josephson Chip of High Temperature Superconductor" http://kvarz.com/general/n4-21.html, Accessed on Mar. 15, 2019.

Rufenacht, A., et al., "Simultaneous Double Waveform Synthesis with a Single Programmable Josephson Voltage Standard", 2016 Conference on Precision Electromagnetic Measurements, IEEE, 2016.

\* cited by examiner

FIG. 1

FIG. 2

FIG. 3

211

FIG. 5

FIG. 6

US 11,557,708 B2

Sheet 9 of 38

US 11,557,708 B2

FIG. 10

FIG. 11

Metrologia 55 (2018) 5152

| NMIJ/                                         |          |                 | *************************************** |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | *************************************** |                              |

|-----------------------------------------------|----------|-----------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------------------|

| Voltage 17.3 V                                |          | NIST [24]       | PTB/Supracon<br>[29]                    | P78 [36]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | INRIM/PTB [38] KVARZ [40]               | KVARZ [40]                   |

| # of 13s 524.28                               |          | 10 V<br>265 116 | 10 V<br>69 63 2                         | 201V<br>139264                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1.19 V<br>8.192                         | 25 m.V<br>161                |

| Bias Frequency 16 GHz<br>Junction SNS         |          | 18.3 GHz<br>SNS | SS SS                                   | SNS<br>SNS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         | 75 GHz<br>HTS grain boundary |

| Material NDN/<br>TIN,/)                       | Ž        |                 | NB/NB/Si/NB                             | NEW SECTION SE | 28/21-210/20                            | YBarcasOr bicrystal          |

| Temperature <11 K<br># of US/Stack 2          | <b>₩</b> | ×<br>V.         | ×<br>V_                                 | ×<br>×<br>×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ٧<br>٢                                  | 47 K                         |

| # of IJS in LSB 128<br>LSB resolution 4235 mV | 2        | \$<br>27.67     | 25.5                                    | 2<br>278.1V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                         |                              |

FIG. 19

|                                        | $PIVS(I): f_{CW} = 19$ | = 19,999913151365 GHz | 65 GHz         | PJVS(2)  | PJVS(2); fcw = 18.379 925 659 035 GHz | 659035 GHz     |

|----------------------------------------|------------------------|-----------------------|----------------|----------|---------------------------------------|----------------|

| Subarray #                             | # of BS                | Bias @ 10 V           | Node voltage/V | # of IJS | Bias @ 10 V                           | Node voltage/V |

| 23                                     | 16800                  | <del></del>           | 10,000         | 16800    | +                                     | 10.000         |

| 22                                     | 16800                  | <del></del>           | 9,305          | 16800    | <del></del>                           | 9,361          |

| ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | 16800                  | <del></del>           | 8.610          | 16800    | <del></del>                           | 8.723          |

| 20                                     | 8400                   |                       | 7,916          | 14958    |                                       | 8.084          |

| 6                                      | Ø                      | <del></del>           | 7.568          | 16800    | <del></del>                           | 7.516          |

| ∞                                      | <b>%</b>               |                       | 7.568          | 16800    |                                       | 6.877          |

| <u></u>                                | 54                     |                       | 7.569          | 16800    | <del></del>                           | 6.239          |

| 2                                      | 791                    | Φ                     | 7.567          | 16800    | +                                     | 5,600          |

| Y.                                     | 486                    | 0                     | 7.567          | 16800    | +                                     | 4,962          |

| 4                                      | 1458                   | <b>~</b>              | 7.567          | 16800    | +                                     | 4,323          |

| ~                                      | 4374                   | Φ                     | 7.567          | 90891    |                                       | 3,683          |

| 22                                     | 16797                  | <b>~</b>              | 7.567          | 90891    | -                                     | 3,046          |

| ,<br>,                                 | 16800                  | <br>-+-               | 7.567          | 16800    | +                                     | 2.408          |

| 9                                      | 16800                  |                       | 6.872          | 90891    | <br>- <del>-</del>                    | 1.769          |

| φ <b>,</b>                             | 16800                  | <br>-+-               | 6.177          | 90891    | <br>                                  | 1.131          |

| ∞c                                     | 16800                  |                       | 5.482          | 8400     |                                       | 0.492          |

| <i>L</i> ~                             | 16800                  | -\$-                  | 4.787          | Q        | 0                                     | 0.173          |

| 9                                      | 16800                  | ganani<br>            | 4.093          | 18       | garant<br>anglas                      | 0.173          |

| 800                                    | 16800                  |                       | 3.398          | 24       | <b>\$</b>                             | 0.172          |

| ~4                                     | 16800                  |                       | 2.703          | 162      |                                       | 0.172          |

| 545                                    | 16800                  |                       | 2.008          | 486      | Φ                                     | 0.166          |

| 73                                     | 16800                  |                       | 1313           | 1458     | 0                                     | 0.166          |

| <del>,</del> ;                         | 14958                  | annex<br>. anife.     | 0.619          | 4374     | -                                     | 0.166          |

|                                        |                        |                       |                |          |                                       |                |

| System                 | Grounded node              | Leakage current/pA | $R_{\rm L}/{ m G}\Omega$ |

|------------------------|----------------------------|--------------------|--------------------------|

| PIVS(1)                | Low of the array (DAC 0)   | 350 ± 15           | 28.7 ± 1.2               |

|                        | High of the array (DAC 23) | 390 ± 20           | 25.7 ± 1.3               |

| PJVS(2) Low of High of | Low of the array (DAC 0)   | 370 ± 20           | 26.8 ± 1.5               |

|                        | High of the array (DAC 23) | 550 ± 30           | 18.2 ± 1.0               |

FIG. 26

Waveform (Four steps)

| Switching mode | Start voltage  | # | 7# | #3  | <del>*</del> |

|----------------|----------------|---|----|-----|--------------|

| A (start)      | 20             |   | 20 | 201 | 201          |

|                | >              | > |    | 20  | 20           |

|                | > 9            |   |    | >   | >            |

|                | +10 V or -10 V |   | >  | 20  |              |

FIG. 28

| Dither current nominal | PJVS<br>polarity | Dither current applied to PJVS(1) | Dither current applied to PJVS(2) |

|------------------------|------------------|-----------------------------------|-----------------------------------|

| +di                    | +10 V            | +di                               | -di                               |

|                        | -10 V            | -di                               | +di                               |

|                        | +10 V            | +di                               | -di                               |

|                        | -10 V            | -di                               | +di                               |

| ()                     | +10 V            | 0                                 | 0                                 |

|                        | -10 V            | 0                                 | 0                                 |

|                        | +10 V            | 0                                 | 0                                 |

|                        | -10 V            | 0                                 | 0                                 |

| di                     | +10 V            | −di                               | +di                               |

|                        | -10 V            | +di                               | -di                               |

|                        | +10 V            | −di                               | +di                               |

|                        | -10 V            | +di                               | -di                               |

FIG. 30

FIG. 31

Vn \ noitsiveb nsllA

FIG. 35

PJVS(1)-PJVS(2) / nV

| Component/Type                                                                                                                                              | Distribution                                      | Uncertainty/nV                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------------------------------------------|

| Statistical/A Frequency accuracy/B Differential leakage current/B Leakage current between voltage leads/B NVM gain error/B NVM polarity reversal and CMRR/B | Normal Normal Rectangular Rectangular Rectangular | 0.00<br>0.00<br>0.00<br>0.00<br>0.00<br>0.00<br>0.00<br>0.0 |

| Combined uncertainty $(k = 1)$<br>Extended uncertainty $(k = 2)$                                                                                            |                                                   | 0.145                                                       |

FIG. 38

### JOSEPHSON VOLTAGE STANDARD

# CROSS REFERENCE TO RELATED APPLICATIONS

The application claims priority to U.S. Provisional Patent Application Ser. No. 62/850,756 filed May 21, 2019, the disclosure of which is incorporated herein by reference in its entirety.

# STATEMENT REGARDING FEDERALLY SPONSORED RESEARCH

This invention was made with United States Government support from the National Institute of Standards and Technology (NIST), an agency of the United States Department of Commerce. The Government has certain rights in the invention. Licensing inquiries may be directed to the Technology Partnerships Office, NIST, Gaithersburg, Md., 99; voice (301)-975-2573; email tpo@nist.gov; reference NIST. 20

### BRIEF DESCRIPTION

Disclosed is a Josephson voltage standard comprising: a first electrical conductor that receives a first bias current; a 25 second electrical conductor that receives a second bias current: a third electrical conductor that receives a third bias current; a fourth electrical conductor that receives a first radiofrequency bias; a fifth electrical conductor that receives a second radiofrequency bias; a first Josephson junction 30 array that: comprises a first Josephson junction; receives, from the first electrical conductor, the first bias current; receives, from the third electrical conductor, the third bias current; receives, from the fourth electrical conductor, the first radiofrequency bias; and produces a first voltage refer- 35 ence from the first bias current and the third bias current; a second Josephson junction array in electrical communication with the Josephson junction array and that: comprises a second Josephson junction; receives, from the second electrical conductor, the second bias current; receives, from the 40 third electrical conductor, the third bias current; receives, from the fifth electrical conductor, the second radiofrequency bias; and produces a second voltage reference from the second bias current and the third bias current; a first voltage reference output tap in electrical communication 45 with the first Josephson junction array and that receives the first voltage reference from the first Josephson junction array, such that the first voltage reference is electrically available at the first voltage reference output tap; and a second voltage reference output tap in electrical communi- 50 cation with the second Josephson junction array and that receives the second voltage reference from the second Josephson junction array, such that the second voltage reference is electrically available at the second voltage reference output tap.

Disclosed is a Josephson divider determiner for determining a resistance ratio of a voltage divider with a Josephson voltage standard, the Josephson divider determiner comprising: the Josephson voltage standard; a voltage divider in electrical communication with the Josephson voltage standard and that: comprises a first resistor in electrical communication with the first voltage reference output tap and that receives the first voltage reference from the first voltage reference output tap; and comprises a second resistor in electrical communication with the first resistor and the second voltage reference output tap and that receives the second voltage reference from the second voltage reference

2

output tap; and a polarity switch in electrical communication with the first voltage reference output tap.

Disclosed is a process for producing a voltage reference with a Josephson voltage standard, the process comprising: receiving, by the first Josephson junction array, the first bias current, the third bias current, and the first radiofrequency bias; producing, by the first Josephson junction array, the first voltage reference in response to receiving the first bias current, the third bias current, and the first radiofrequency bias; receiving, by the second Josephson junction array, the second bias current, the third bias current, and the second radiofrequency bias; producing, by the second Josephson junction array, the second voltage reference in response to receiving the second bias current, the third bias current, and the second radiofrequency bias; communicating the first voltage reference from the first Josephson junction array to the first voltage reference output tap; communicating the second voltage reference from the second Josephson junction array to the second voltage reference output tap; receiving the first voltage reference at the first voltage reference output tap; and receiving the second voltage reference at the second voltage reference output tap.

### BRIEF DESCRIPTION OF THE DRAWINGS

The following description cannot be considered limiting in any way. With reference to the accompanying drawings, like elements are numbered alike.

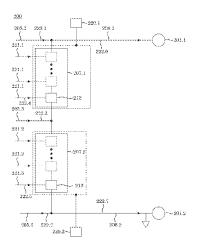

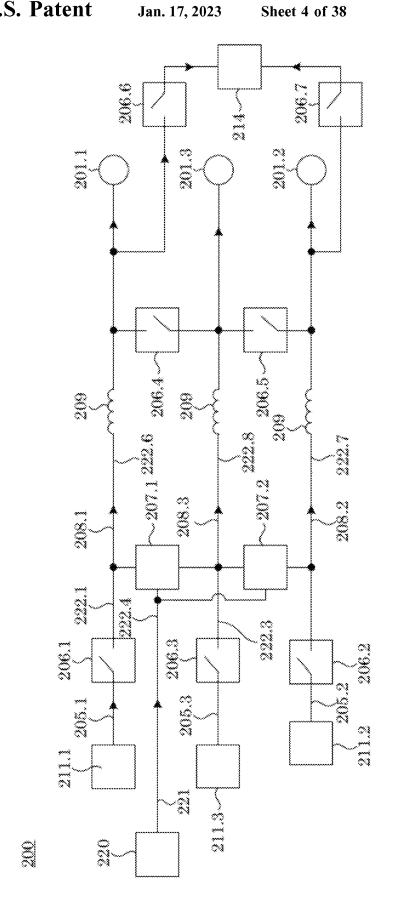

FIG. 1 shows a Josephson voltage standard;

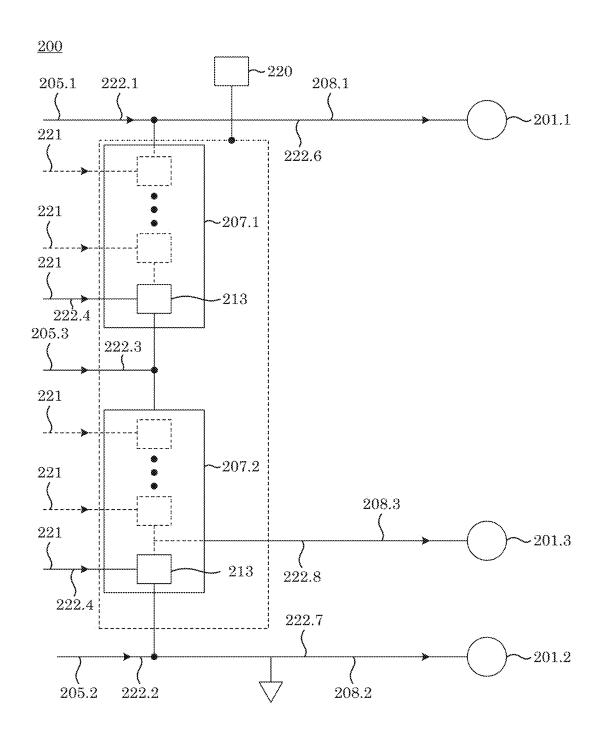

FIG. 2 shows a Josephson voltage standard;

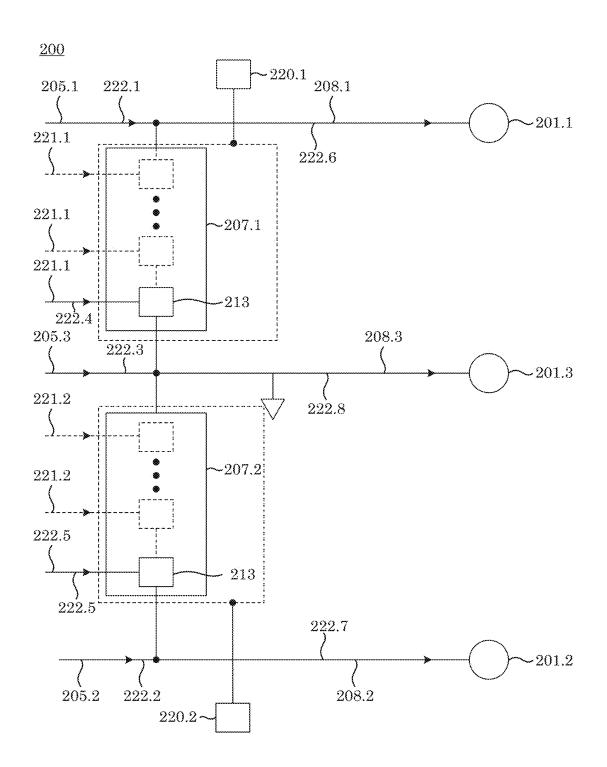

FIG. 3 shows a Josephson voltage standard;

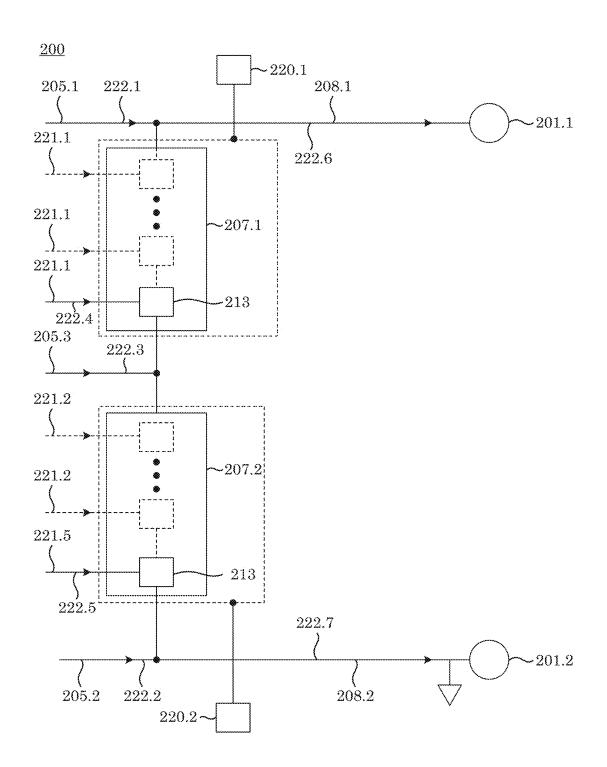

FIG. 4 shows a Josephson voltage standard;

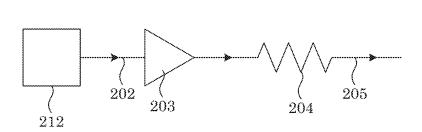

FIG. 5 shows a current source;

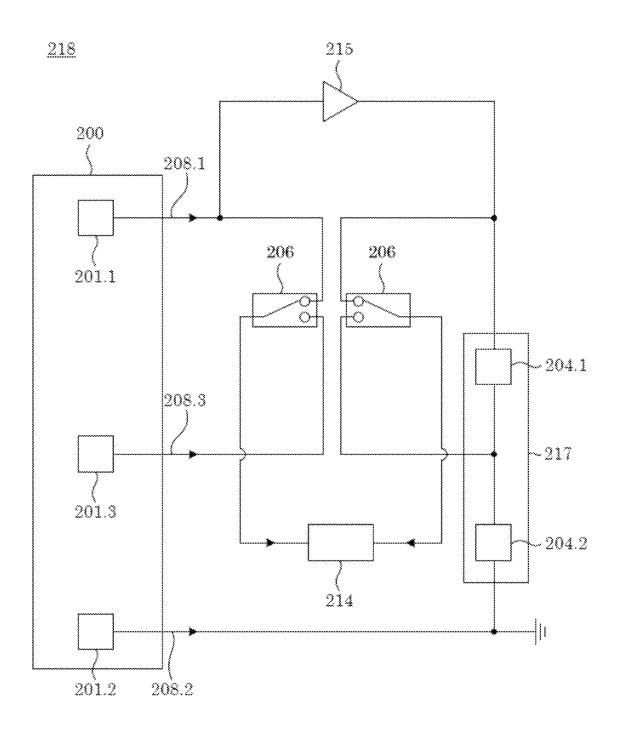

FIG. 6 shows a Josephson divider determiner;

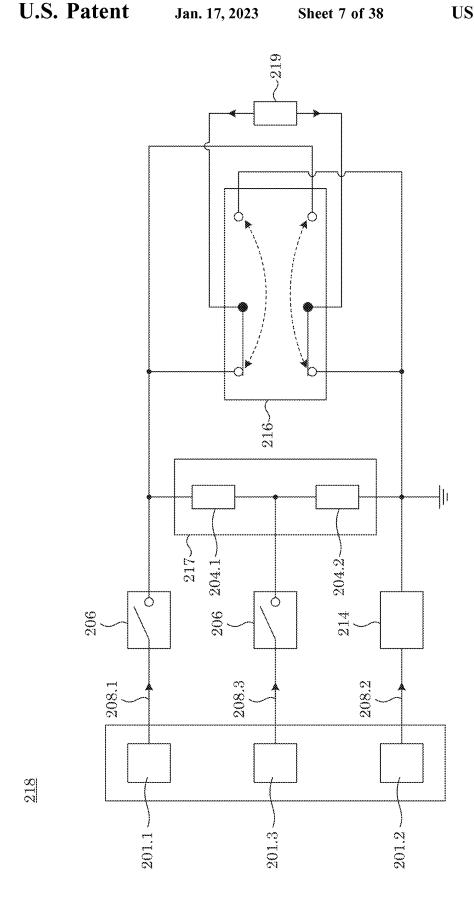

FIG. 7 shows a Josephson divider determiner;

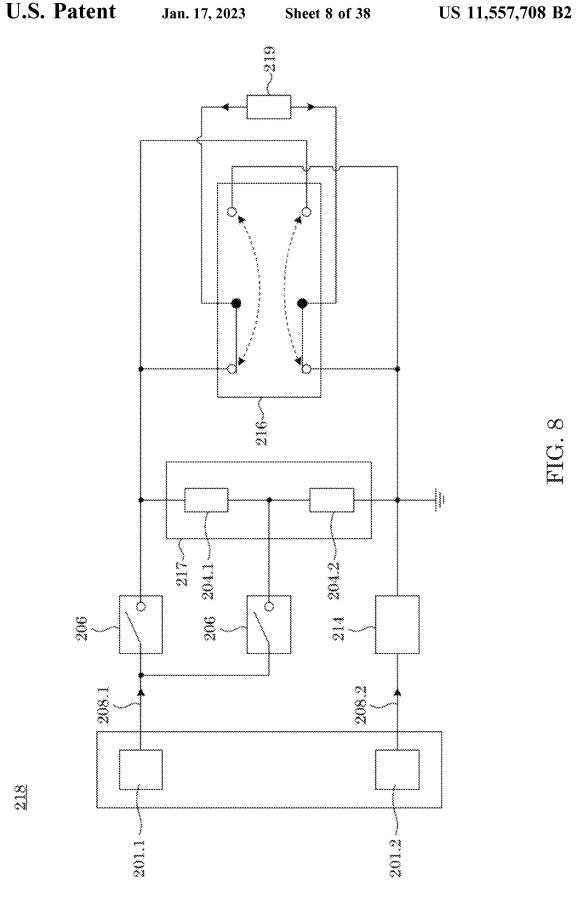

FIG. 8 shows a Josephson divider determiner;

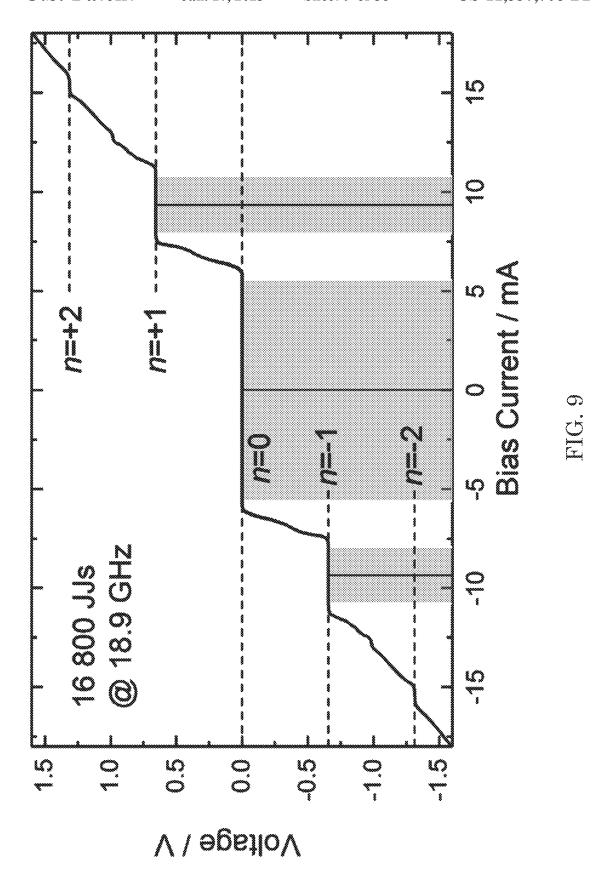

FIG. 9 shows a V-1 curve characteristic of a 16 800 JJ segment measured on a 10 V PJVS circuit. The voltage is accurately defined on the n=0, n=+1, and n=-1 constant voltage steps, but only over the bias current range shown in the grayed areas. The optimum bias value of each step (0 mA, +9.3 mA and -9.3 mA for n=0, +1, and -1, respectively) is indicated by a vertical line. The n=±2 constant voltage steps are visible;

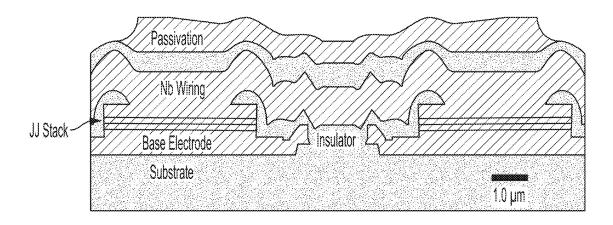

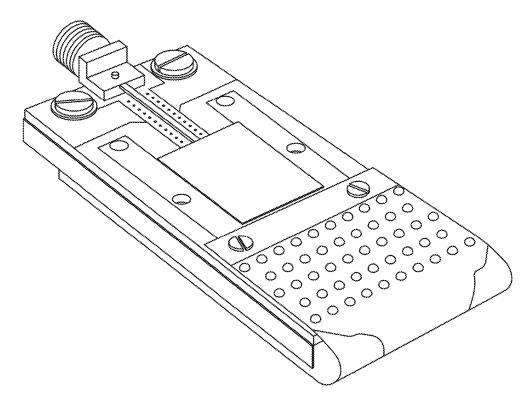

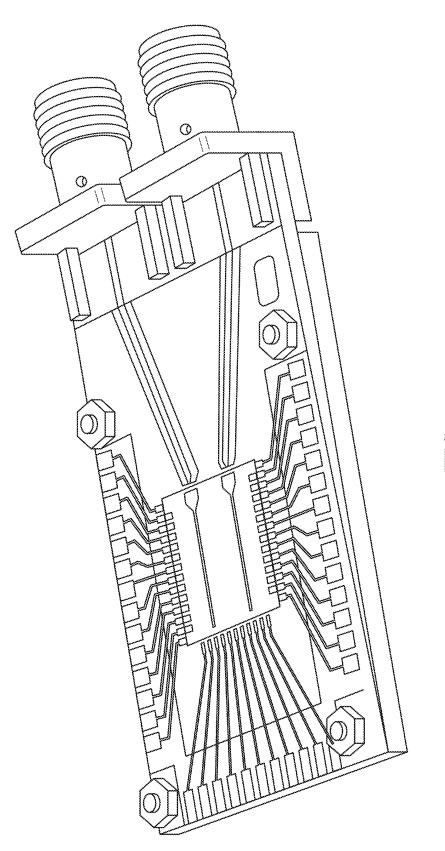

FIG. 10 shows (Left) SEM image of a 10 V PJVS circuit in cross section along propagation direction of the CPW center conductor. Two separate triple-JJ stacks can be seen. (Right) crypopackage for  $10~\rm V$  PJVS circuit. The chip size is  $12~\rm mm\times17~mm$ ;

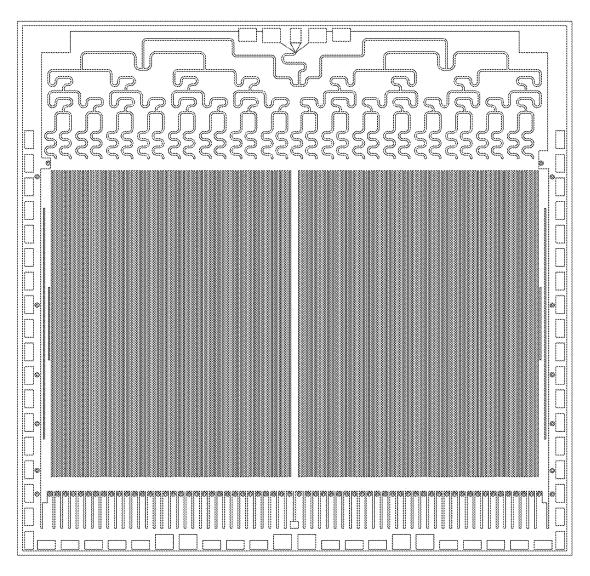

FIG. 11 shows a 17 V NMIJ/AIST PJVS circuit including 524 288 NbN/TiN/NbN JJs. The chip size is 15.28 mm×14.70 mm;

FIG. 12 shows a summary of PJVS circuits that, in columns, are sorted by bias frequency:

FIG. **13** shows a calculated spectrum from DC to 50 MHz of a 1 kHz sine wave with rms magnitude of 1 V, based on 12 810 JJs and a clock rate of 14.4×10° pulses s<sup>-1</sup>;

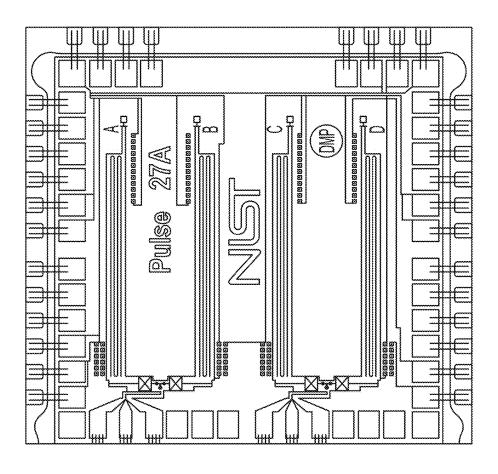

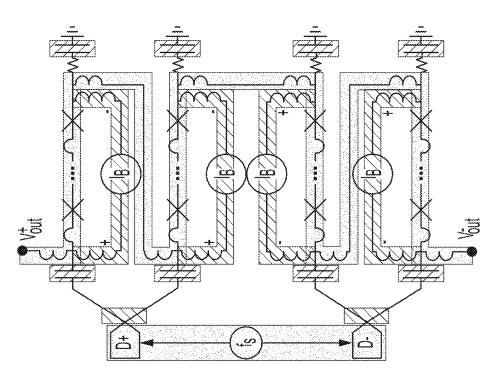

FIG. 14 shows (left) JAWS circuit diagram and (right) a cryopackaged JAWS chip. The circuit can generate an output voltage of 1 V rms. The circuit includes two pulse generator channels (labeled D+ and D-), a single layer of Wilkinson dividers, inside-outside DC blocks, and JJ arrays (Xs). The JJ arrays are connected in series through inductive taps, as is one floating low-frequency current compensation per JJ array (J<sub>B</sub>). The JAWS chip size is 10 mm×10 mm;

FIG. 15 shows a JAWS circuit with two arrays of 6000 JJs fabricated by PTB. The chip size is 10 mm×10 mm. Four sample holders and eight arrays are combined in series to reach 1 V rms:

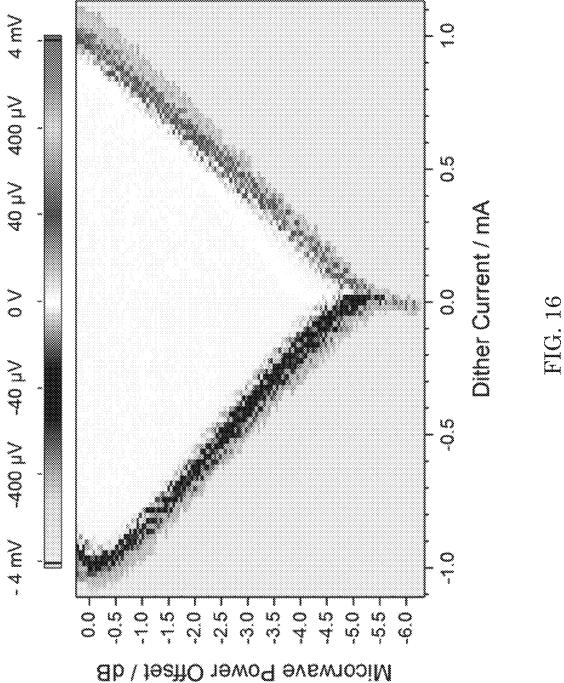

FIG. 16 shows a two-dimensional quantum-locking range of a 10 V PNS array with the subarrays biased such that exactly the same number of junctions are at +5 V and -5 V, producing a null voltage. The horizontal (x) axis is the dither current applied through all the subarrays, while the vertical (y) axis shows microwave power offset in dB relative to initial (optimum) power. The white area indicates QLR where the output voltage remains constant. The measurement was performed on the 1 mV range of the digital nanovoltmeter;

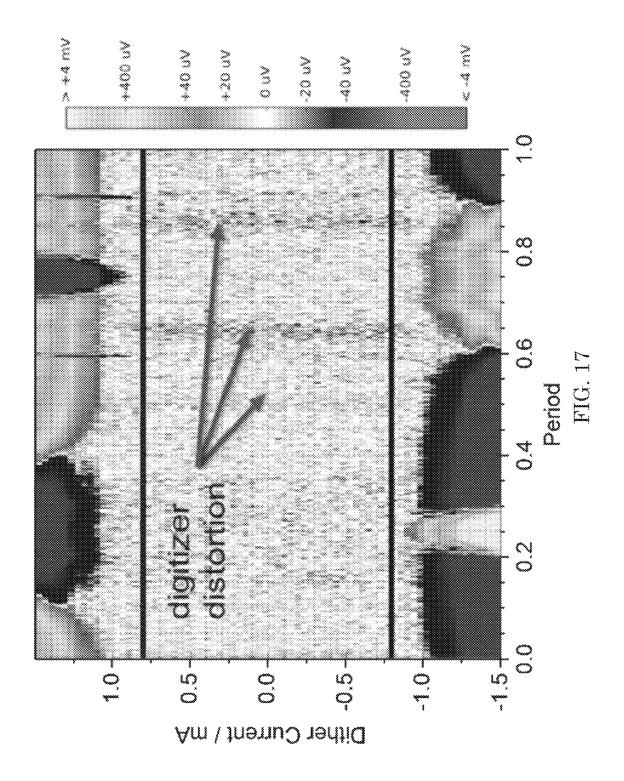

FIG. 17 shows a quantum locking range of a JAWS system generating a 1 kHz waveform with an rms magnitude of 2 V, wherein a voltage residual is indicated for a sine-wave fit as a function of dither offset current (y axis) and waveform period (x axis). The data was digitized over 80 ms with a digitizer (range 10 V, input impedance 1 M $\Omega$ , sampling rate 1 MHz). Lines show the 1.6 mA quantum locking range of this waveform and system, wherein residuals are limited by digitizer distortion and do not depend on offset current over the entire waveform period. Pulse 25 sequences (e.g. at 0.25, 0.6, and 0.9 parts of a period) are shown for OLR;

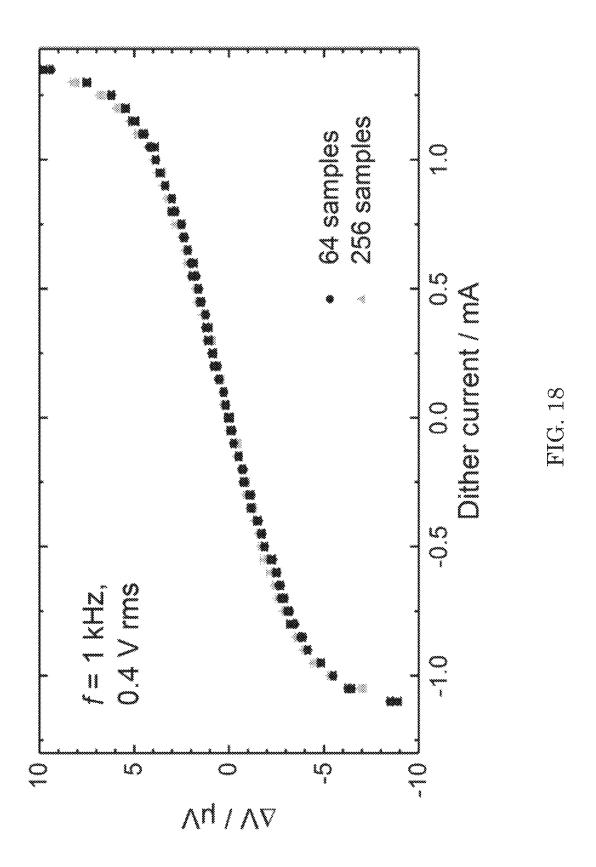

FIG. 18 shows a relative change of rms voltage measured with a thermal transfer standard for a 0.4 V stepwise-approximated sine wave versus applied dither current. The voltage value at 0 mA is used as the reference for the voltage difference  $\Delta V$ . The slope observed within the  $\pm 0.7$  mA dither range is due to transients present in the waveform; the QLR of the PJVS array when generating DC voltages is  $\pm 0.7$  mA;

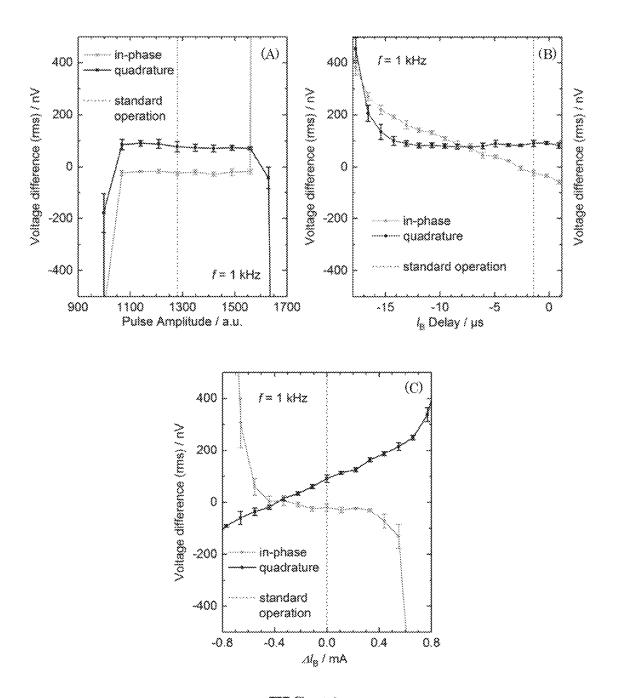

FIG. 19 shows in-phase and quadrature magnitudes of the residual difference between two JAWS systems, each generating a 1 kHz output with an rms magnitude of 1 V, versus different bias parameters. The standard operating point (vertical dotted line) is the bias setting that maximizes the QLR 40 for DC current offset. (A) The residual magnitude is independent of the pulse magnitude (within the QLR from about 1100 to 1550) but in depends strongly on (B) compensation phase and (C) compensation magnitude. The phase is expressed in terms of the time delay of the compensation 45 relative to the pulse generator output, while the compensation magnitude is expressed as a change MB from the standard operating point of about 10 mA;

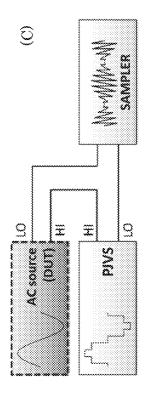

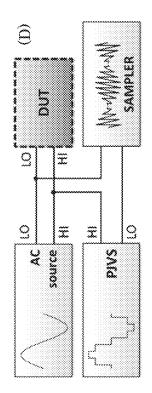

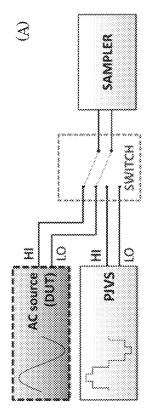

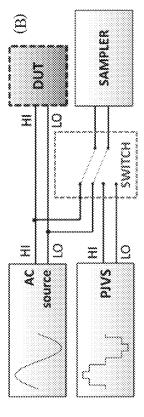

FIG. 20 shows various sampling methods: (a) and (b) sampling and switching and (c) and (d) differential sampling. The DUT can be an AC source, as shown in (a) and (c), or the source output can be connected to a DUT, as shown in (b) and (d). Synchronization signals to the various instruments are not shown;

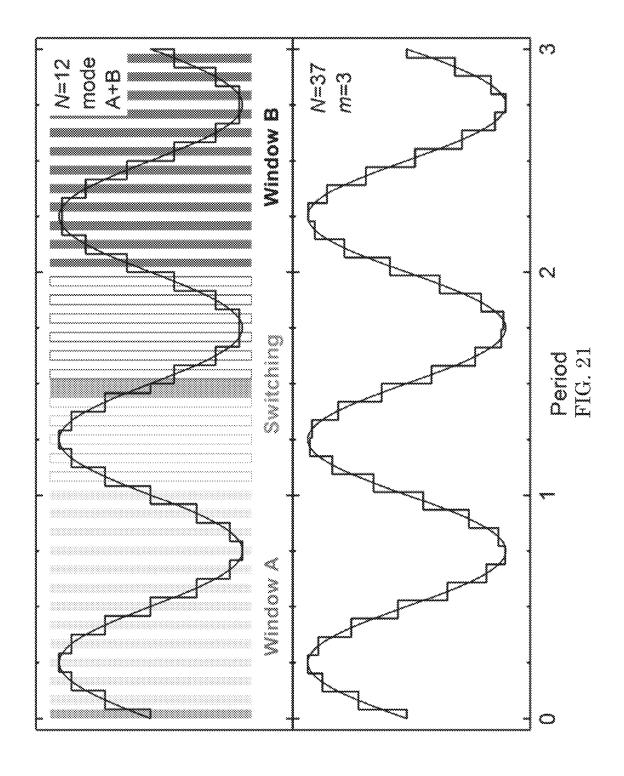

FIG. 21 shows types of PJVS reference waveforms to 55 track AC source over multiple periods. (Top) alternating sampling windows (A) and (B) are shifted by T/2N to cover the full range of the AC source period in the same measurement. (Bottom) the PJVS reference is adjusted to match the AC source over m=3 periods; 60

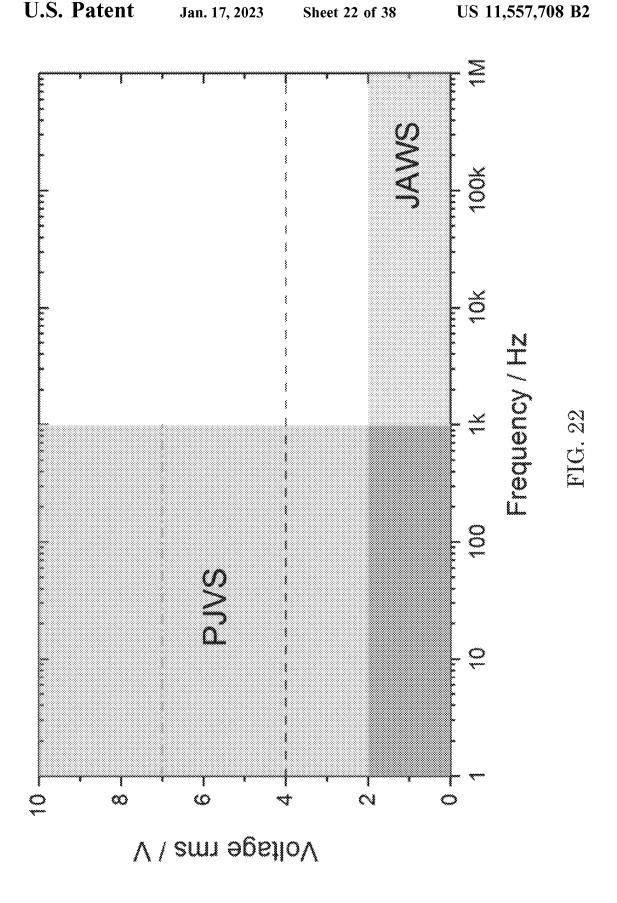

FIG. 22 shows a graph of voltage versus frequency diagram for an application range of sampling methods for PJVS and JAWS. The dashed line shows extension enabled by JAWS circuits with 4 V rms amplitude. The dash-dotted line represents rms amplitude limit of 10 V PJVS circuits;

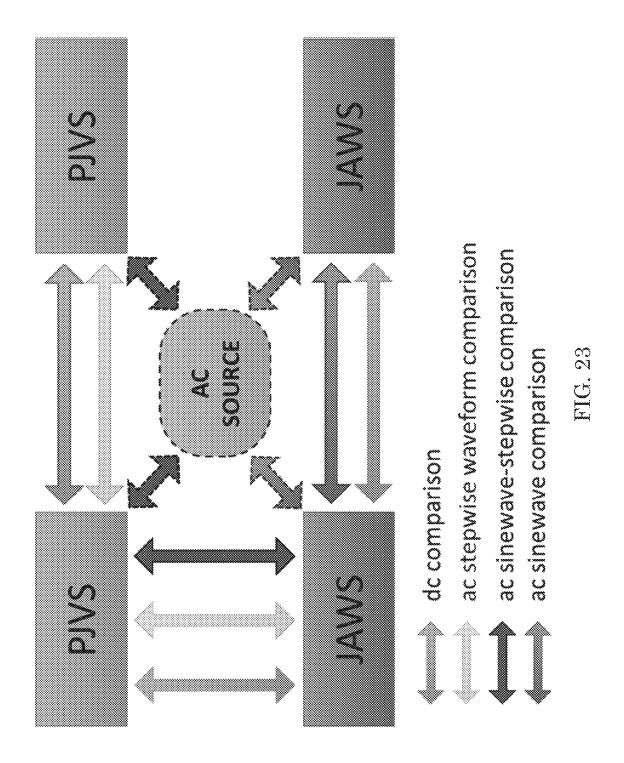

FIG. 23 shows direct and indirect comparison between two PJVS, two JAWS, or a JAWS and a PJVS voltage 4

standards. Diagonal arrows with dashed outlines show indirect comparison links with an AC source as a transfer standard:

FIG. 24 shows a 10 V junction and bias configuration for two PJVS arrays. The number of Josephson junctions (JJs) are distributed as shown for the two PJVS circuits operating at the microwave bias frequencies  $f_{CW}$  indicated. The two circuits produce 10 V using the different bias current polarities indicated in the Bias columns. Although there are different voltages at the various subarray nodes, both circuits have 0 V potential at the low side of their circuits. Least significant bit (LSB) subarrays are shown;

FIG. 25 shows measured LCG at 10 V and corresponding equivalent leakage resistance  $R_L$ ;

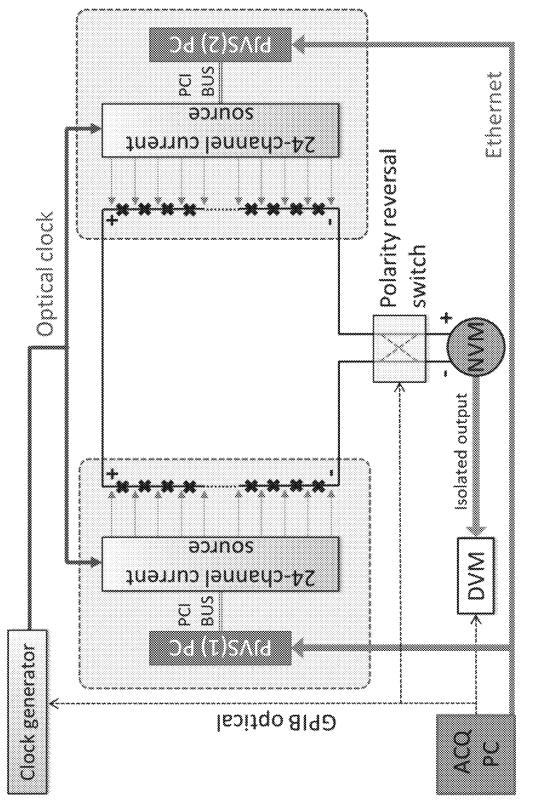

FIG. 26 shows an automated comparison measurement between two PJVS systems using an analog nanovoltmeter; FIG. 27 shows waveforms to synchronously switch voltage output polarity of both arrays;

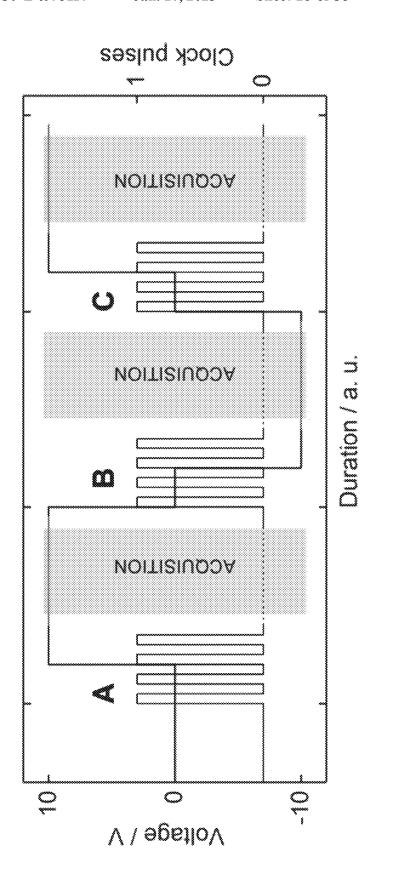

FIG. 28 shows a waveform for synchronous switching between voltages (A: start 0 V to +10 V, B: from +10 V to -10 V, and C: from -10 V to +10 V). The four clock pulses are shown. The data acquisition occurs once both PJVS output voltages are fully settled;

FIG. **29** shows measurement sequences and dither currents during direct comparison between two PJVS systems to check for proper quantization of both PJVS arrays;

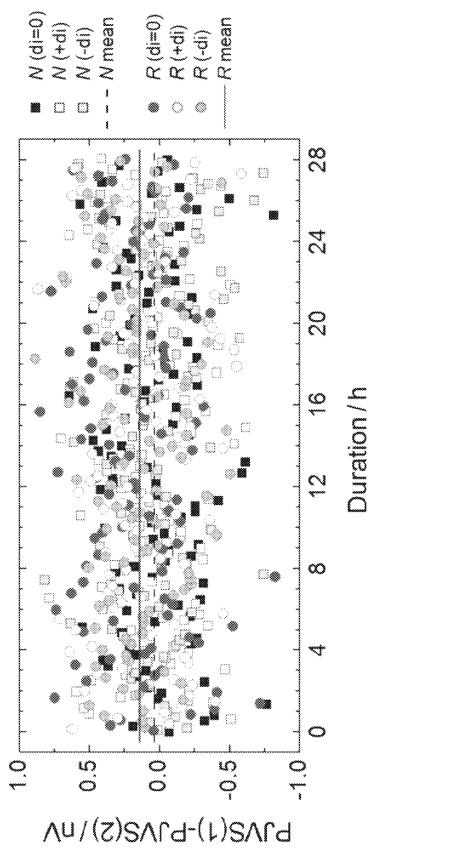

FIG. 30 shows voltage differences ΔV measured at 10 V alternately for the two input polarities of the NVM (N=normal, R=reverse). The dither current di=0.2 mA does not affect the measurement, confirming proper quantization of the voltages provided by both systems over the 28 h of the measurement sequence;

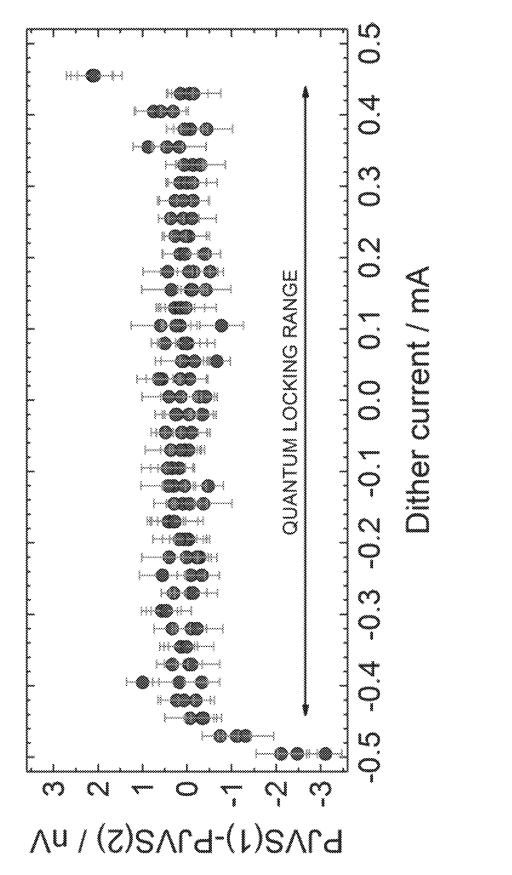

FIG. 31 shows results for automated comparison measurement at 10 V as a function of dither current applied to both PJVS arrays (N polarity only with NVM polarity reversal switch removed). The step width (0.9 mA) is comparable to the smallest quantum locking range measured independently for the two PJVS systems;

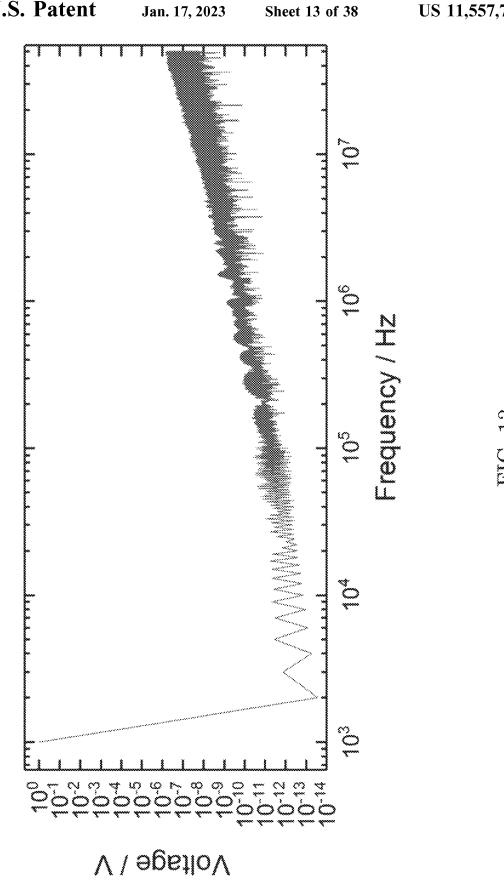

FIG. 32 shows Allan deviation extracted from 8192 readings with a short on the NVM input (NVM range:  $10 \mu V$ , DVM range: 1 V range with 10 PLC). The 1/f noise floor (0.1 nV) is reached after 1 min;

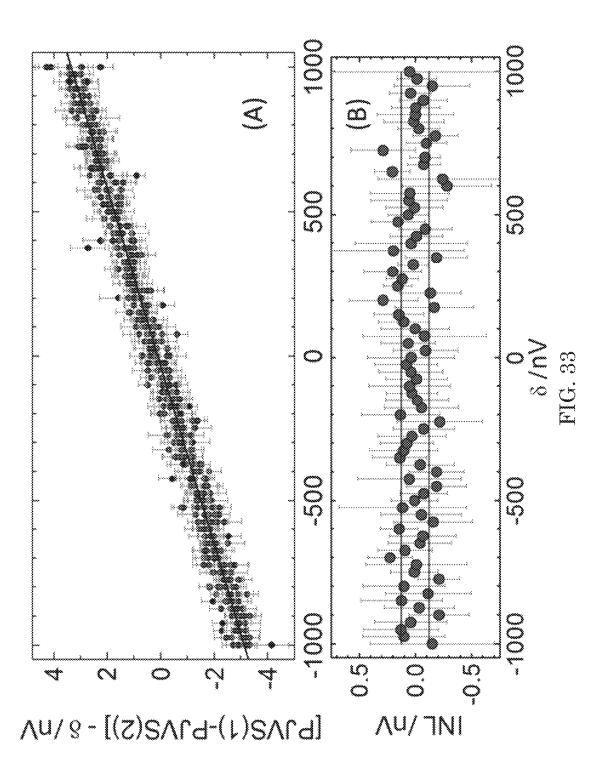

FIG. 33 shows a gain calibration and nonlinearity (INL) of the NVM. (A) Deviation of the measured difference PJVS(1)–PJVS(2) from the calculated voltage difference  $\delta$ . The output voltage of PJVS(1) is adjusted to  $10 \text{ V} + \delta$  by slightly detuning the microwave frequency, while the output voltage of PJVS(2) is kept at 10 V. Measurements were repeated six times for each  $\delta$ . The gain error (slope) of the NVM is  $3 \times 10^{-3} \text{ V} \text{ V}^{-1}$ . (B) Deviation from the fit (INL) in (A). The value and error reported for the INL are the mean value and standard deviation of the six readings displayed in (A), respectively. The two horizontal lines indicate the k=1 interval of confidence (standard deviation) calculated from all the INL data measured ( $\pm 0.12 \text{ nV}$ );

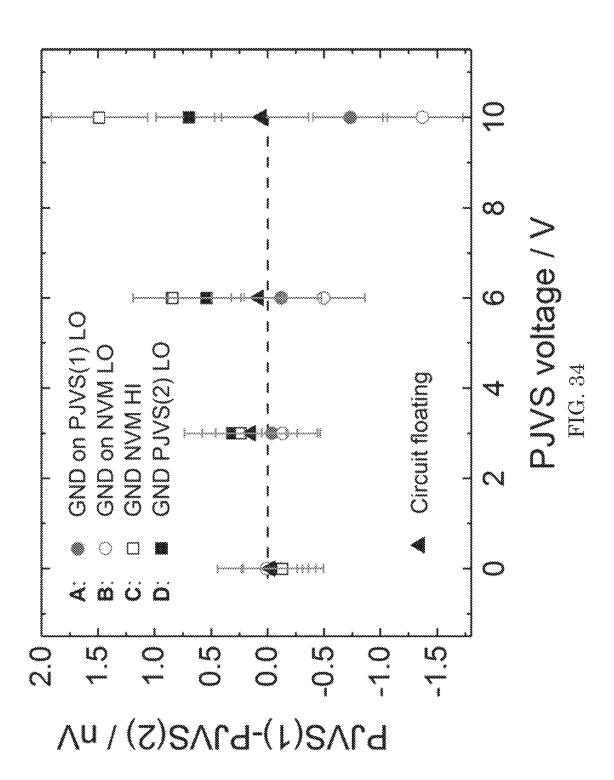

FIG. 34 shows a measured voltage difference PJVS(1)–PJVS(2) for different grounding locations. The error bars represent the standard deviation (k=1) obtained with a minimum of 30 individual readings for each voltage and grounding configuration;

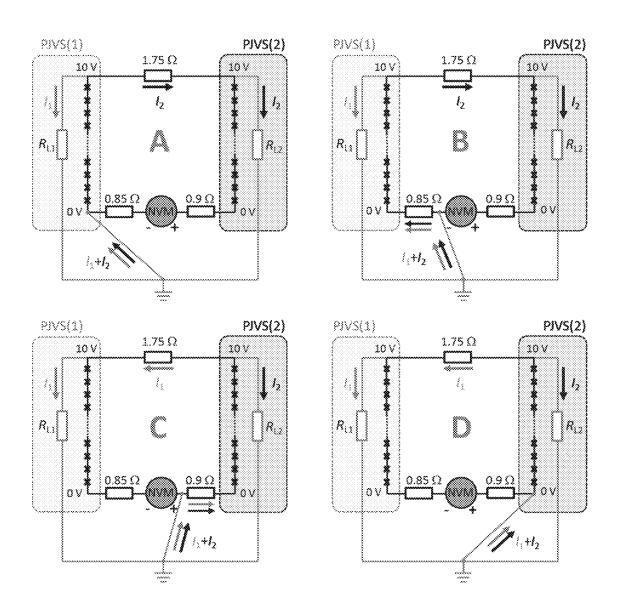

FIG. 35 shows a leakage current path  $I_1$  and  $I_2$  through the equivalent leakage resistances to ground  $R_{L1}$  and  $R_{L2}$  associated with PJVS(1) and PJVS(2), respectively. The leakage paths to ground of each system are much more complex than the simplified  $R_{L1}$  and  $R_{L2}$  representations shown here. In this model, the current distribution is shown for four different ground positions: (A) connected to the low side of the

PJVS(1) array, (B) connected to the low input terminal of the NVM, (C) connected to the high input terminal of the NVM, and (D) connected to the low side of the PJVS(2) array;

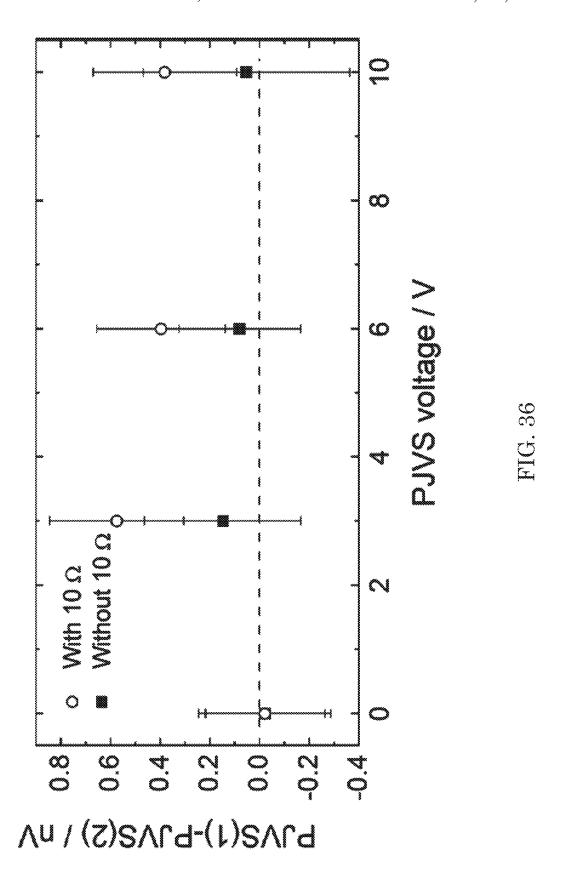

FIG. 36 shows measured voltage differences for the N polarity of the detector with and without a  $10\Omega$  resistance inserted between the two high sides of the PJVS systems;

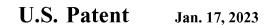

FIG. 37 shows a measured voltage difference for both N and R polarities of the detector as a function of the PJVS voltage when the circuit is floating from ground potential; and

FIG. 38 shows components of uncertainty budget for the difference voltage measured between the two cryocooled PJVS systems at 10 V when both arrays are floating from ground.

#### DETAILED DESCRIPTION

A detailed description of one or more embodiments is presented herein by way of exemplification and not limitation.

It has been discovered that a Josephson voltage standard advantageously provides independent simultaneous voltage references as voltage outputs that can be produced in an absence of multiple systems. The Josephson voltage standard can be integrated into an article for a fixed voltage ratio, 25 variable voltage ratio, dual signals (e.g., square waves or sine waves of similar root mean square (rms) voltage), and the like. Beneficially, the Josephson voltage standard can be widely disseminated in a compact dual voltage references that can be, e.g., 1 V and 100 mV, that can be used to 30 calibrate a secondary voltage standard at 10 V using a 10:1 self-calibrated resistive voltage divider. It is contemplated that the Josephson voltage standard can be implemented in AC power metrology, e.g., to calibrate a power meter with two reference signals and impedance ratio measurements 35 that involve amplitude and phase programmability.

Josephson voltage standard 200 produces a plurality of voltage reference 208. In an embodiment, with reference to FIG. 1, FIG. 2, FIG. 3, and FIG. 4, Josephson voltage standard 200 includes first electrical conductor 222.1 that 40 receives first bias current 205.1; second electrical conductor 222.2 that receives second bias current 205.2; third electrical conductor 222.3 that receives third bias current 205.3; fourth electrical conductor 222.4 that receives first radiofrequency bias 221.1; fifth electrical conductor 222.5 that receives 45 second radiofrequency bias 221.2; and first Josephson junction array 207.1 in electrical communication with first electrical conductor 222.1 and third electrical conductor 222.3. First Josephson junction array 207.1 includes first Josephson junction 213 and receives, from first electrical 50 conductor 222.1, first bias current 205.1; receives, from third electrical conductor 222.1, third bias current 205.3; receives, from fourth electrical conductor 222.4, first radiofrequency bias 221.1; and produces first voltage reference 208.1 from first bias current 205.1 and third bias current 205.3. Second 55 Josephson junction array 207.2 is in electrical communication with first Josephson junction array 207.1 and includes second Josephson junction 213; receives, from second electrical conductor 222.2, second bias current 205.2; receives, from third electrical conductor 222.3, third bias current 60 205.3; receives, from fifth electrical conductor 222.5, second radiofrequency bias 221.2; and produces second voltage reference 208.2 from second bias current 205.2 and third bias current 205.3. First voltage reference output tap 201.1 receives, from sixth electrical conductor 222.6, first voltage 65 reference 208.1 from first Josephson junction array 207.1 such that first voltage reference 208.1 is electrically avail-

able at first voltage reference output tap 201.1 Second voltage reference output tap 201.2 receives, from seventh electrical conductor 222.7, second voltage reference 208.2

from second Josephson junction array 207.2 such that first voltage reference 208.2 is electrically available at first voltage reference output tap 201.2.

According to an embodiment, Josephson voltage standard 200 includes third voltage reference output tap 201.3 in electrical communication with second Josephson junction array 207.2. Third voltage reference output tap 201.3 receives, from eighth electrical conductor 222.8, third voltage reference 208.3 from second Josephson junction array 207.2 such that third voltage reference 208.3 is electrically

available at third voltage reference output tap 201.3.

With reference to FIG. 1, the first Josephson junction array 207.1, the second Josephson junction array 207.2, and the third voltage reference output tap 201.3 can be in electrical series with respect to each other. With reference to FIG. 2, the first Josephson junction array 207.1, it is contemplated that third voltage reference output tap 201.3 can be in electrical communication with first Josephson junction array 207.1, such that first Josephson junction array 207.1 and second Josephson junction array 207.2 are connected in parallel with respect to third voltage reference output tap 201.3 and in electrical series with respect to each other. Moreover, a selected electrical conductor 222 can be electrically connected to ground. In an embodiment, second voltage reference 208.2 is connected to ground as shown in FIG. 1 and FIG. 3. In an embodiment, third voltage reference 208.3 is connected to ground as shown in FIG. 2.

In an embodiment, with reference to FIG. 4, Josephson voltage standard 200 includes first current source 211.1 in electrical communication with first Josephson junction array 207.1 and that produces first bias current 205.1 and communicates first bias current 205.1 to first Josephson junction array 207.1. First relay 206.1 is electrically interposed between first current source 211.1 and each of first Josephson junction array 207.1 and first voltage reference output tap 201.1. Here, first relay 206.1 receives, from first current source 211.1, first bias current 205.1; and selectively switches between communicating first bias current 205.1 to first Josephson junction array 207.1 and not communicating first bias current 205.1 to first Josephson junction array 207.1. First inductor 209.1 is electrically interposed between first Josephson junction array 207.1 and first voltage reference output tap 201.1; receives, from first Josephson junction array 207.1, first voltage reference 208.1; and isolates first voltage reference output tap 201.1 from first Josephson junction array 207.1.

First relay 206.4 can be electrically interposed between first voltage reference output tap 201.1 and each of third voltage reference output tap 201.3 and second voltage reference output tap 201.2, wherein first relay 206.4 selectively switches between: electrically connecting first voltage reference output tap 201.1 to third voltage reference output tap 201.3 and second voltage reference output tap 201.2 and electrically disconnecting first voltage reference output tap 201.1 from third voltage reference output tap 201.3 and second voltage reference output tap 201.3 and second voltage reference output tap 201.3.

Second relay 206.5 can be electrically interposed between second voltage reference output tap 201.2 and each of first voltage reference output tap 201.1 and third voltage reference output tap 201.3, wherein second relay 206.5 selectively switches between: electrically connecting second voltage reference output tap 201.2 to third voltage reference output tap 201.3 and electrically disconnecting second voltage reference output tap 201.2 from first voltage reference

output tap 201.1 and second voltage reference output tap 201.2. Third current source 211.3 is in electrical communication with first Josephson junction array 207.1 and second Josephson junction array 207.2; produces third bias current 205.3; and communicates third bias current 205.3 to first Josephson junction array 207.1 and second Josephson junction array 207.2. Second current source 211.2 is in electrical communication with second Josephson junction array 207.2; produces second bias current 205.2; and communicates second bias current 205.2 to second Josephson junction 10 array 207.2.

In an embodiment, voltmeter 214 is in electrical communication with first voltage reference output tap 201.1 and second voltage reference output tap 201.2; receives first voltage reference 208.1; receives second voltage reference 15 208.2; and determines voltage difference between first voltage reference 208.1 and second voltage reference 208.2.

Josephson voltage standard 200 provides a plurality of voltage reference 208 that can be used to determine a resistance ratio of voltage divider 217. In an embodiment, 20 with reference to FIG. 6, FIG. 7 and FIG. 8, Josephson divider determiner 218 includes voltage divider 217 in electrical communication with Josephson voltage standard 200. Voltage divider 217 includes first resistor 204.1 in electrical communication with first voltage reference output 25 tap 201.1 and that receives first voltage reference 208.1 from first voltage reference output tap 201.1; and second resistor 204.2 in electrical communication with first resistor 204.1 and second voltage reference output tap 201.2 such that second resistor 204.2 receives second voltage reference 30 208.2 from second voltage reference output tap 201.2; and first Relay 206 in electrical communication with first voltage reference output tap 201.1. Second relay 206 is in electrical communication with third voltage reference output tap 201.3 and includes a voltmeter 214 in electrical communication 35 with the two relays 206, wherein the two relays 206 selectively switches simultaneously between: electrically connecting voltmeter 214 to first voltage reference output tap 201.1, electrically disconnecting voltmeter 214 from third voltage reference output tap 201.3, and electrically discon- 40 necting third voltage reference output tap 201.3 from voltage divider 217; and electrically connecting voltmeter 214 to third voltage reference output tap 201.3, electrically disconnecting voltmeter 214 from first voltage reference output tap 201.1, and electrically connecting third voltage reference 45 output tap 201.3 to voltage divider 217 so that first resistor 204.1 and second resistor 204.2 receive third voltage reference 208.3 from third voltage reference output tap 201.3. In an embodiment with reference to FIG. 6, a buffer amplifier in electrical communication between Josephson voltage 50 standard 200 and voltage divider 217 provides the bias current to the voltage divider 217. In some embodiments, with reference to FIG. 7 and FIG. 8, polarity switch 216 is in electrical communication with second voltage reference output tap 201.2, and includes: voltmeter 214 in electrical 55 communication with second voltage reference output tap 201.2 and polarity switch 216; and Zener voltage standard 219 in electrical communication with polarity switch 216, wherein polarity switch 216 selectively swaps electrical connectivity of Zener voltage standard 219 between first 60 voltage reference output tap 201.1 and second voltage reference output tap 201.2. In embodiment, with reference FIG. 8, only the Josephson voltage tap 201.1 is connected to first and second relays 206. Based on the Relay 206 configuration the voltage reference 208.1, on Josephson voltage 65 tap 201.1 is adjusted to match successively the voltage at the top of Resistance 204.1 and Resistance 204.2.

8

Josephson voltage standard 200 include a substrate on elements of Josephson voltage standard 200 are formed or disposed. The substrate can be, e.g., an insulating material so that electrical current does not flow therethrough and to electrically insulate individual elements from one another. Exemplary substrate include intrinsic silicon, oxidized silicon, sapphire and the like.

Current source 211 provides bias current 205 to Josephson junctions 213 to select the positive voltage states, negative voltage states, or zero state based on the value and sign of the current. Exemplary current sources 211 include semiconductor-based current sources and the like. In an embodiment, with reference to FIG. 5, current source 211 includes voltage source 212 that produces bias voltage 202 that is received by amplifier 203 and communicated to resistor 204 that produces bias current 205. Exemplary voltage sources 212 include digital-to-analog converters and the like. Bias voltage 202 produced by voltage source 212 can be from -16 V to +16 V specifically from -10 V to +10 V, and more specifically from -3 V to +3 V. A current of bias current 205 (e.g., 205.1, 205.2, 205.3) independently can be from -30 mA to +30 mA, specifically from -20 mA to +20 mA, and more specifically from -15 mA= to +15 mA. Bias currents 205 (e.g., 205.1, 205.2, 205.3) can be AC, or DC. Moreover, bias current 205 can have an amplitude adjustment. In an embodiment, bias current 205 includes a software application to select a current value to operate the Josephson junction array and verify the range over which the selected voltages remain constant and quantized, which is referred to as quantum locking range.

Relay 206 receives bias current 205 to connect and disconnect the bias current line 205 from the Josephson junction array 207 and Relay 206 receives voltage reference 208 to connect a voltmeter across the Josephson junction array 207 or short all the voltage reference output taps together. Exemplary relays 206 include electromagnetic relays, semiconductor relays, and the like. Moreover, relay 206 is implemented to facilitate automation. In an embodiment, relay 206 includes an operation sequence to connect the Josephson junction array when the temperature is below a normal to superconducting transition temperature of the junction and disconnection of the Josephson junction array when the system is not operated or is above the operating temperature. Relay 206 provides a shorting function to protect the Josephson junction array from inadvertent electrical currents during the connection and disconnection of the external wring to the voltage reference output taps. All relays are controlled by the automation software running the Josephson voltage standard 200 system.

Electrical conductor 222 communicates bias current 205, voltage reference 208, and radiofrequency source 220. Here, electrical conductor 222 can include low resistance metallic wires to physically connect the bias current source with the Josephson junction array and low-loss microwave co-axial cables. Exemplary electrical conductors 222 include copper wires, phosphor-bronze wires, or silver coated cupronickel coaxial cables and the like. Moreover, electrical conductor 222 must have a thermal dissipation that is compatible with the cooling capacity of the cryogenic system used to cool the Josephson junction array 207. In an embodiment, electrical conductor 222 includes a combination of detachable cables at room temperature and fixed cables designed to minimize thermal conduction from room temperature to cryogenic temperature.

Josephson junction array 207 receives bias current 205 and radiofrequency bias 221 and produces voltage reference 208. Here, Josephson junction array 207 can include mul-

tiple Josephson junction 213 that are connected electrically in series to increase the voltage and can be embedded in a coplanar waveguide structure, a microstrip structure and the like. Exemplary Josephson junction arrays 207 include a Josephson junction array circuit design with the radiofrequency bias distributed in parallel to multiple Josephson junction arrays that are electrically connected in series with superconductors. Moreover, Josephson junction array 207 can include junctions that are vertically stacked to increase the density of Josephson junctions in the circuit without compromising the performance of the device. In an embodiment, Josephson junction array 207 includes the design and the microfabrication of integrated circuits including a combination of multiple photolithographic, layer deposition and etching processes to fabricate an ensemble of Josephson junctions having electrical characteristics with appropriate response to the applied radiofrequency bias.

Josephson junction 213 is a weak link between two superconductors. Exemplary Josephson junctions 213 20 include a superconductor-normal metal-superconductor junction, superconductor-insulator-superconductor junction, and the like. A number of Josephson junctions 213 in Josephson junction array 207 can be, e.g., from 1 to 1 000 000, specifically from 1 to 265 116, and more specifically 25 from 1 to 34 320. It is contemplated that each Josephson junction array 207 in Josephson junction array 207 receives radiofrequency bias 221 and bias current 205 to produce voltage reference 208. According to an embodiment, with reference to FIG. 1, the Josephson junction array 207 is 30 capable of generating simultaneously two voltage outputs biased with a single radiofrequency source 220. The three current bias lines 205.1, 205.2 and 205.3 allows to bias the Josephson junction array 207.1 and 207.2 in series and opposition to generate a null or near null voltage to adjust 33 and verify a current bias range of the Josephson junction array 207.1 and 207.2, and to optimize the bias conditions for quantum locking ranges. In an embodiment, there is simultaneous generation of a 1 V and 100 mV voltage, with a total of 34 320 Josephson junction 213 biased with a 40 radiofrequency signal of ~14.1 GHz for application requiring the calibration of a 10:1 ratio. According to an embodiment, with reference to FIG. 2, Josephson voltage standard 220 is capable of generating two independent voltages, by adjusting the two independent radiofrequency biases 220.1 45 and 220.2 connected respectively to the Josephson junction arrays 207.1 and 207.2. Three current bias lines 205.1, 205.2 and 205.3 provide biasing Josephson junction arrays 207.1 and 207.2 in series and opposition to generate a null or near null voltage in order to better enable adjustment and veri- 50 fication of the current bias range of the Josephson junction array 207.1 and 207.2, and to optimize the bias conditions for quantum locking ranges. Applications of for this device include dual dc voltage generation or dual ac waveform generation with programmable relative phase of the two 55 voltages for calibration voltage ratios, impedance ratios, and ac power. According to an embodiment, with reference to FIG. 3, Josephson junction array 207 generates a single dc voltage or ac voltage waveform with amplitude resolution limited only by the frequency resolution of the two radiof- 60 requency sources 220.1 and 220.2. In this configuration, voltage reference output tap 201.3 has been removed. The grounding reference is attached to conductor 208.2. The three current bias lines 205.1, 205.2 and 205.3 provide biasing of Josephson junction array 207.1 and 207.2 in series 65 and opposition to generate a null or near null voltage in order for adjustment and verification of the current bias range of

Josephson junction array 207.1 and 207.2, and to optimize the bias conditions for quantum locking ranges.

Radiofrequency source 220 produces radiofrequency bias 221 to drive the Josephson junctions and generate the  $2\pi$ phase shift in each Josephson junction responsible for generating a voltage of h/2e per second. Exemplary radiofrequency sources 220 include continuous wave frequency generators, pulse pattern generators, arbitrary waveform generators and the like. A power of radiofrequency bias 221 (e.g., 221.1, 221.2, 221.3) independently can be from -110 dBm to +30 dBm, specifically from -20 dBm to +28 dBm, and more specifically from -20 dBm to +20 dBm. A frequency of radiofrequency bias 221 independently can be from 1 GHz to 2 THz, specifically from 1 GHz to 100 GHz, and more specifically from 1 GHz to 22 GHz. Moreover, radiofrequency bias 221 is locked and referenced to a frequency reference with intrinsic or calibrated accuracy. In an embodiment, radiofrequency bias 221 includes a combination of radiofrequency source, microwave cable and dcblocks, microwave amplifier, and on-chip microwave coplanar waveguide splitter and circuits and components to distribute the radiofrequency signal to the all of the Josephson junctions in the array.

Voltage reference 208 (e.g., 208.1, 208.2, 208.3) is produced by Josephson junction array 207 from bias current 205 and radiofrequency bias 221. A voltage of voltage reference 208 (208.1, 208.2, 208.3) independently can be from -15 V to +15 V, specifically from -10 V to +10 V, and more specifically from -1.2 V to +1.2 V. Voltage references 208 independently can be AC, DC, or pulsed independently. A frequency of voltage references 208 can be from dc to 1 GHz, specifically from 1 Hz to 1 MHz, and more specifically from 1 Hz to 100 kHz. When pulsed, voltage references 208 independently can have a duty cycle from 1 GHz to 200 GHz, specifically from 1 GHz to 90 GHz, and more specifically from 1 GHz to 28.8 GHz. Moreover, voltage reference 208 provides an accurate voltage reference, if the Josephson junction array 207 is biased on its quantum locking range and the radiofrequency source 220 is referred to an accurate frequency standard. In an embodiment, voltage reference 208 includes a twisted copper pair to limit the electromotive force and minimize the output resistance in series with the Josephson junction array 207.

Inductor 209 receives voltage reference 208 and electrically isolates voltage reference output tap 201 Exemplary inductors 209 include coils, ferrite core wrapped wires, and the like. An inductance of inductor 209 can be from 1 nH to 100 mH, specifically from 1 nH to 1 mH, and more specifically from 1 nH to 100  $\mu$ H. Moreover, inductor 209 is present to limit a rapid current surge on conductors 208 in order to protect the Josephson junctions from damage due to an electrostatic discharge. In an embodiment, inductor 209 includes a copper wire wrapped around a ferrite core.

Voltage reference output tap 201 receives voltage reference 208 to allow the reference voltage to be accessible for precision calibration and measurement applications. Exemplary voltage reference output tap 201 include Copper blocks, low-thermal binding posts, low-thermal multiconductor connectors, and the like. Moreover, voltage reference output tap 201 must be made of material terminals with low-thermal electromotive force and is implemented such that it is protected from air flow by use of a cover to minimize temperature fluctuation at the connector. In an embodiment, voltage reference output tap 201 includes the protective circuit made of inductor 209 and relay short 206.4 and 206.5 controlled by the automation software.

Voltmeter 214 receives voltages (e.g., voltage reference 208.1, voltage reference 208.3, and the like) and determines a potential difference therefrom to verify that the Josephson junction array is biased on its quantum locking range. Exemplary voltmeters 214 include digital voltmeter, digital nanovoltmeter, voltage digitizer, spectrum analyzer and the like. Moreover, voltmeter 214 must have a dynamic range, resolution and sampling frequency compatible with measuring the voltage amplitude and frequency of the synthesized ac waveform. In an embodiment, voltmeter 214 includes 10 automation software to connect the voltmeter with relays 206.6 and 206.7 and to automatically run the bias parameters to an optimum bias value and evaluate the quantum locking ranges of the bias parameters. External calibration of the voltmeter is not required to perform this task, since the 15 voltmeter is mainly operated as a null detector when the multiple segments of the Josephson circuit are biased in series opposition to obtain a null or near null voltage across the Josephson junction array 207.

With reference to FIG. 6 and FIG. 7, Josephson divider 20 determiner 218 includes Josephson voltage standard 200 that produces provides voltage reference 208.1, voltage reference 208.2, and voltage reference 208.3 to voltage divider 217, relay 206, polarity switch 216 and from which voltmeter 214 determines a resistance ratio of resistors 204 in 25 voltage divider 217. With reference to FIG. 8, Josephson voltage standard 200 that produces provides voltage reference 208.1, and voltage reference 208.2 to voltage divider 217, relay 206, polarity switch 216 and from which voltmeter 214 determines a resistance ratio of resistors 204 in 30 voltage divider 217. In an embodiment, with reference to FIG. 6, two relay 206 connect simultaneously the measurement circuit to successively the input and the divided output of the voltage of the voltage divider 217. Combining the results of these two measurements allows the determination 3: of the voltage ratio. As a result, voltmeter 214 successively measures the voltage difference between the two voltage references provided by Josephson Voltage standard 200 and the voltage at the input and divided output of the voltage divider 217. In FIG. 6. voltage divider 217 is biased in 40 current by a low noise buffer amplifier 215. The stability and the polarity selection at the input of the buffer amplifier is provided by the Josephson voltage standard 200. Bias polarity inversion allows to remove the parasitic thermal electromotive force present in the measurement circuit. In this 45 embodiment, no current is drawn from the Josephson junction array that could cause a systematic error in the measurement. Polarity switch 216 is implemented to reverse the polarity of the generated signal voltages biasing the resistive voltage divider. Exemplary polarity switch 216 include 50 electromagnetic relays, semiconductor relays, and the like. Moreover, polarity switch 216 has double poles with low thermal electromotive force contacts and connections. According to an embodiment, with reference to FIG. 7, polarity switch 216 provides an automated operation to 55 reverse the bias current polarity to the resistive voltage divider. In this embodiment the stable bias current source is provided by Zener voltage standard 219. The Zener voltage standard does not need to be calibrated for this measurement. As a result, voltmeter 214 successively measure the 60 voltage difference between the two voltage outputs of and respectively input and the divided output of the voltage of the voltage divider 217. Relay 206 connect successively either the measurement circuit to the input and the divided output of the Resistive voltage divider. Combining the 65 results of these two measurements allows the determination of the voltage ratio Bias current polarity inversion allows to

12

remove the parasitic thermal electromotive force present in the measurement circuit. In this embodiment, no current is dawn from the Josephson junction array that could cause a systematic error in the measurement. FIG. 8 shows two output voltage taps from Josephson voltage standard 200. To match successively the voltage at either the top of resistor 204.1 and a top of resistor 204.2, the voltage output reference 208.1 is adjusted. The same method as used for that for FIG. 7 can be to determine the voltage ratio of voltage divider 217.

Voltage divider 217 is precision measurement instrument capable to scale up or down the accuracy from a voltage standard reference. A number of resistors 204 in voltage divider 217 can be, e.g., from 1 k $\Omega$  to 10 M $\Omega$ , specifically from 1 k $\Omega$  to 40 k $\Omega$ , and more specifically from 1 k $\Omega$  to 10 k $\Omega$ . A resistance of resistors 204 independently can be from 1 $\Omega$  to 10 M $\Omega$ , specifically from 10 $\Omega$  to 40 k $\Omega$ ), and more specifically from 10 $\Omega$  to 10 k $\Omega$ . Moreover, voltage divider 217 is thermally stabilized to minimize the temperature drift. In an embodiment, voltage divider 217 includes devices with low power coefficient, high divider ratio stability and possibly various selectable ratios.

Zener voltage standard 219 is semiconductor based stable voltage reference. Moreover, Zener voltage standard 219 has a low voltage drift and low noise. In an embodiment, Zener voltage standard 219 includes a buffer output amplifier to provide the necessary current to drive the resistive voltage divider.

Josephson voltage standard 200 can be made in various ways. In an embodiment, a process for making Josephson voltage standard 200 includes microfabrication of the various element and interconnecting them together. Fabrication of quantum circuit elements and classical circuit elements described herein can entail deposition of materials, such as superconductors, dielectrics, or metals. Depending on the selected material, these materials can be deposited using deposition processes such as chemical vapor deposition, physical vapor deposition (e.g., evaporation or sputtering), or epitaxial techniques, among other deposition processes. Processes for fabricating circuit elements described herein can entail the removal of one or more materials from a device during fabrication. Depending on the material to be removed, the removal process can include, e.g., wet etching techniques, dry etching techniques, or lift-off processes. The materials forming the circuit elements described herein can be patterned using lithographic techniques (e.g., photolithography or e-beam lithography).

Josephson voltage standard 200 has numerous advantageous and unexpected benefits and uses. In an embodiment, a process for producing voltage reference 208 with Josephson voltage standard 200 includes receiving, by first Josephson junction array 207.1, first bias current 205.1, third bias current 205.3, and first radiofrequency bias 221.1; producing, by first Josephson junction array 207.1, first voltage reference 208.1 in response to receiving first bias current 205.1, third bias current 205.3, and first radiofrequency bias 221.1; receiving, by second Josephson junction array 207.2, second bias current 205.2, third bias current 205.3, and second radiofrequency bias 221.2; producing, by second Josephson junction array 207.2, second voltage reference 208.2 in response to receiving second bias current 205.2, third bias current 205.3, and second radiofrequency bias 221.2; communicating first voltage reference 208.1 from first Josephson junction array 207.1 to first voltage reference output tap 201.1; communicating second voltage reference 208.2 from second Josephson junction array 207.1 to second voltage reference output tap 201.2; receiving first voltage

reference 208.1 at first voltage reference output tap 201.1; and receiving second voltage reference 208.2 at second voltage reference output tap 201.2.

The process for producing voltage reference 208 with Josephson voltage standard 200 also can include producing, 5 by first Josephson junction array 207.1 and second Josephson junction array 207.2, third voltage reference 208.3 in response to: receiving, by first Josephson junction array 207.1, first bias current 205.1, third bias current 205.3, and first radiofrequency bias 221.1; receiving, by second Josephson junction array 207.2, second bias current 205.2, third bias current 205.3, and second radiofrequency bias 221.2; communicating third voltage reference 208.3 to third voltage reference output tap 201.3; and receiving third voltage reference output tap 201.3.

The process for producing voltage reference 208 with Josephson voltage standard 200 also can include producing, by second Josephson junction array 207.2, third voltage reference 208.3 in response to: receiving, by second Josephson junction array 207.2, second bias current 205.2, third 20 bias current 205.3, and second radiofrequency bias 221.2; communicating third voltage reference 208.3 to third voltage reference output tap 201.3; and receiving third voltage reference 208.3 at third voltage reference 208.3 at third voltage reference output tap 201.3.

Josephson voltage standard 200 and processes disclosed 25 herein have numerous beneficial uses, including providing a primary voltage realization in a compact form format with reduced cost and hardware complexity. Advantageously, Josephson voltage standard 200 overcomes limitations of technical deficiencies of conventional compositions such as 30 the use of multiple Josephson voltage standard systems for the calibration of voltage ratios, impedance ratio calibration, power applications or arbitrary low amplitude voltage generation. Further, reduced complexity in the bias design compared to tradition Josephson voltage standards simplifies the automation of the system and enables dissemination application.

Josephson voltage standard 200 and processes herein unexpectedly reduce the complexity for the generation of simultaneous multiple voltage reference outputs. Moreover, 40 Josephson voltage standard 200 provides of a primary realization of the unit Volt.

It will be appreciated that Josephson voltage standard 200 provides producing a plurality of voltage references 208 simultaneously with single or multiple Josephson junction 45 arrays 207 that can be disposed in a single cryogenic system. Voltage references 208 can be of fixed ratio, independently programmable, frequency locked, or phase locked for AC, power, or impedance applications. Josephson voltage standard 200 can be applied to a Josephson voltage standard 50 (JVS); DC voltages or stepwise approximated waveforms, e.g., generated by a programmable Josephson voltage standards (PJVS), arbitrary waveforms generated by the Josephson arbitrary waveform synthesizer (JAWS), dual RF signals for communications, and the like. Josephson voltage stan- 55 dard 200 provides simultaneous generation of fixed or variable voltage ratios based on a selected configuration of elements of Josephson voltage standard 200 or bias configuration to operate Josephson junction array 207. Josephson voltage standard 200 can provide independent voltage 60 references 208 that can include an arbitrary (e.g., integer) number of voltage references 208. Josephson voltage standard 200 can be implemented in a single chip design with multipole voltage reference output taps 201 or a plurality of independent circuits/devices located within a single cryo- 65 genic vessel (e.g., a Dewar or cryostat). In addition, Josephson voltage standard 200 can include wiring to communicate

14