2000 International Conference on Characterization and Metrology for ULSI Technology

# The Coming & Ongoing Changes in IC Interconnect Fabrication

&

What This Has to do With Metrology

Kenneth A. Monnig Phd Associate Director, Interconnect

(06/27/00)

### OUTLINE -

Why Are We Changing

What is Changing

**Problems Encountered**

Brief Discussion on Some 'Counter' Forces (Money Basically)

Where We Are Now

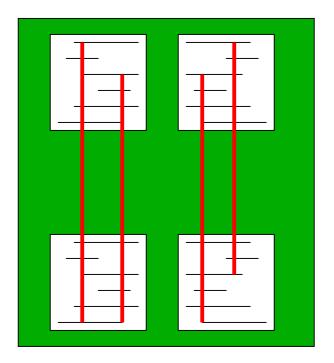

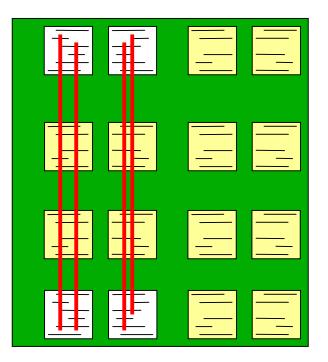

## Global Wires Can't Be Scaled In Length

A Chip

| A | More | Advanced | Chip |

|---|------|----------|------|

|---|------|----------|------|

| <u> </u> |

|----------|

|          |

|          |

|          |

Module on a chip

Local wire in a module

Global wire between modules

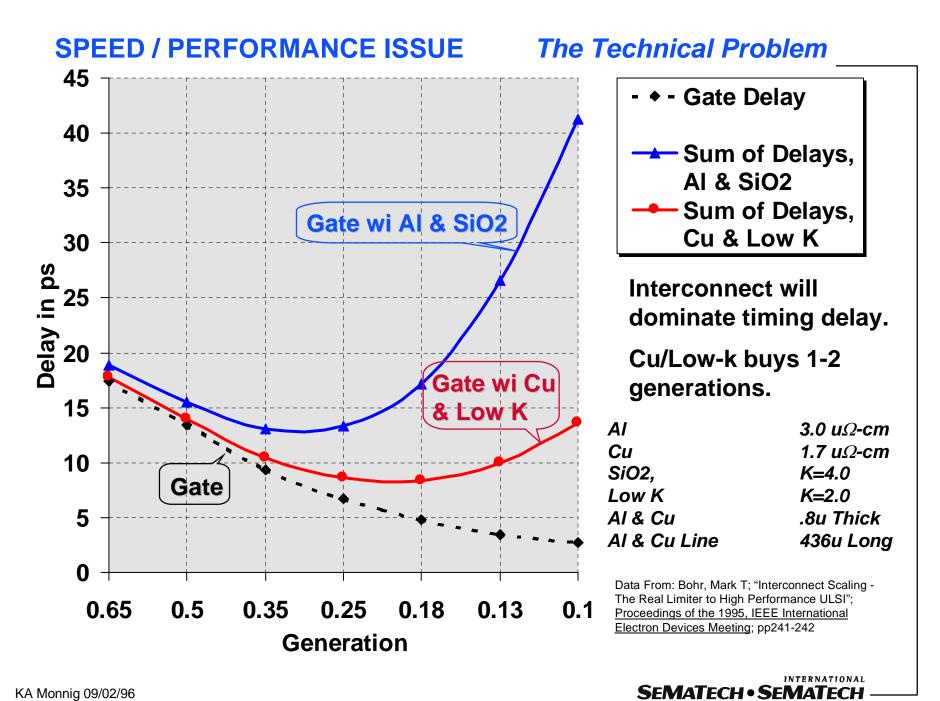

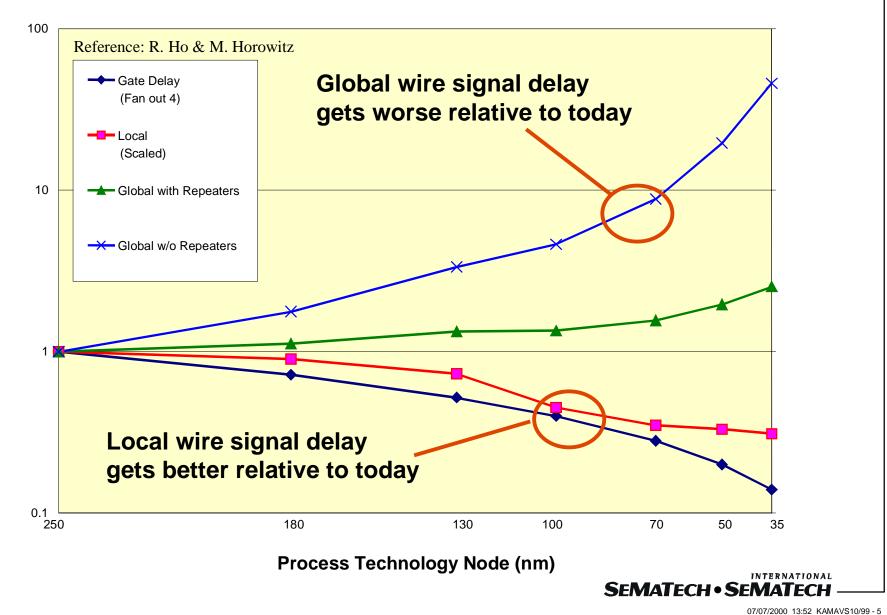

## **Interconnect Delay vs. Design Rule**

**Relative Delay**

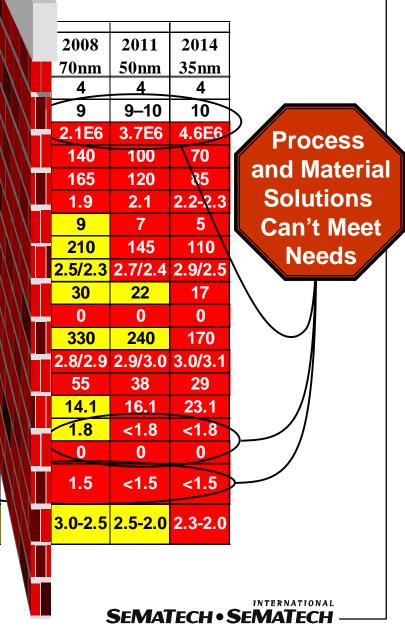

# **1999** Condensed ITRS

| Year of First Product Shipment                                    | 1999    | 2002    | 2005           |

|-------------------------------------------------------------------|---------|---------|----------------|

| Technology Generation                                             | 180nm   | 130nm   | 100nm          |

| Number of metal levels—DRAM                                       |         | 3–4     | 4              |

| Number of metal levels—logic                                      |         | 7–8     | 8–9            |

| Jmax (A/cm²)-wire (at 105°C)                                      |         | 9.6E5   | 1.4E6          |

| Local wiring pitch—DRAM (nm) non-contacted                        |         | 260     | 200            |

| Local wiring pitch—logic (nm)                                     | 450     | 325     | 230            |

| Local wiring AR—logic (Cu)                                        |         | 1.5     | 1.7            |

| Cu local wiring dishing (nm)                                      | 18      | 14      | 11             |

| Intermediate wiring pitch—logic (nm)                              | 560     | 405     | 285            |

| Intrmdt wiring h/w AR-logic (Cu DD via/line)                      | 2.0/2.1 | 2.2/2.1 | 2.4/2.2        |

| Cu intrmdt wiring dishing (nm) 15µ wide wire                      | 64      | 51      | 41             |

| Dielctrc erosion (nm), intrmdt wrng 50% dnsty                     |         | 51      | 41             |

| Global wiring pitch—logic (nm)                                    |         | 650     | 460            |

| Global wiring h/w AR-logic (Cu DD via/line)                       | 2.2/2.4 | 2.5/2.7 | <b>2.7/2.8</b> |

| Cu global wiring dishing (nm) 15µ wide wire                       | 116     | 95      | 76             |

| Contact aspect ratio-DRAM, stacked cap                            |         | 11.4    | 13             |

| Conductor effective resistivity (µ $_{\Omega}$ -cm) Cu *          | 2.2     | 2.2     | 2.2            |

| Barrier/cladding thickness (nm)***                                | 17      | 13      | 10             |

| Interlevel metal insulator effective dielectric                   |         | 3.5-2.7 | 2 2-1 6        |

| constant (k) logic                                                |         | 0.0-2.1 | E.2 1.0        |

| Interlevel metal insulator effective dielectric constant (k) DRAM | 4.1     | 4.1-3.0 | <b>3.0-2.5</b> |

|                                                                   |         |         |                |

\* Assumes a conformal barrier/nucleation layer

\*\*\* Calculated for a conformal layer in local wiring to meet effective conductor resistivity

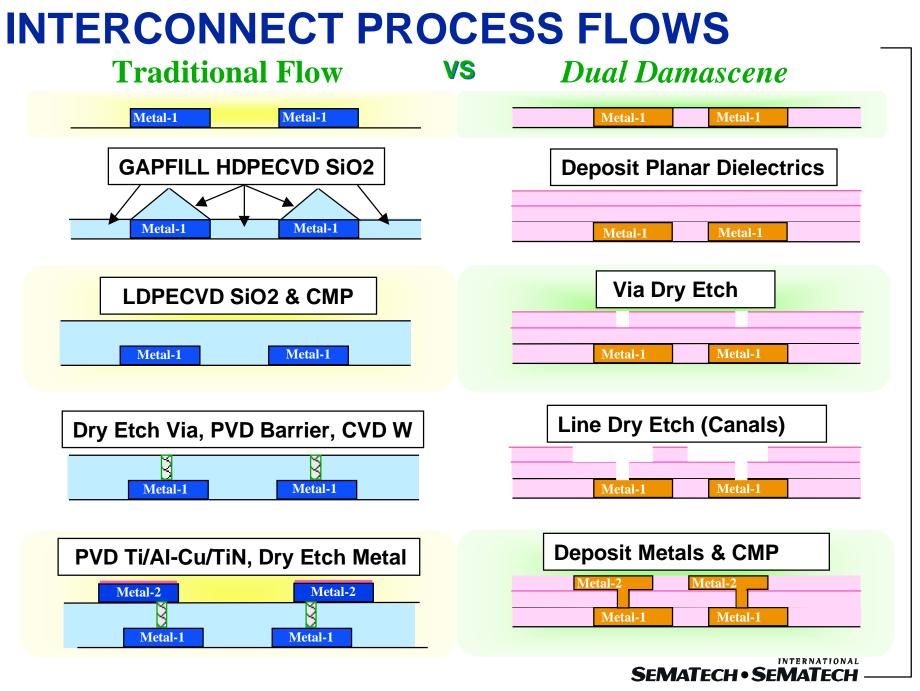

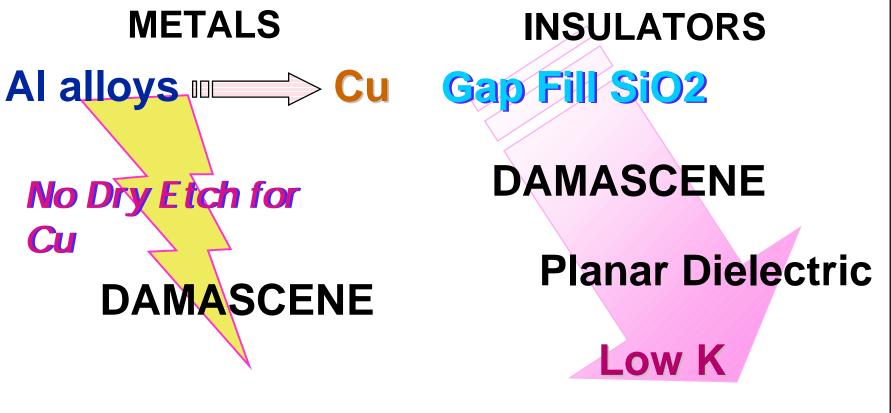

## THE PROCESS FLOW CHANGES RESULT FROM MATERIAL CHANGES

### The Material Changes are Catalyzed by 'New' IC Performance Needs

SEMATECH • SEMATECH —

KAMonnig

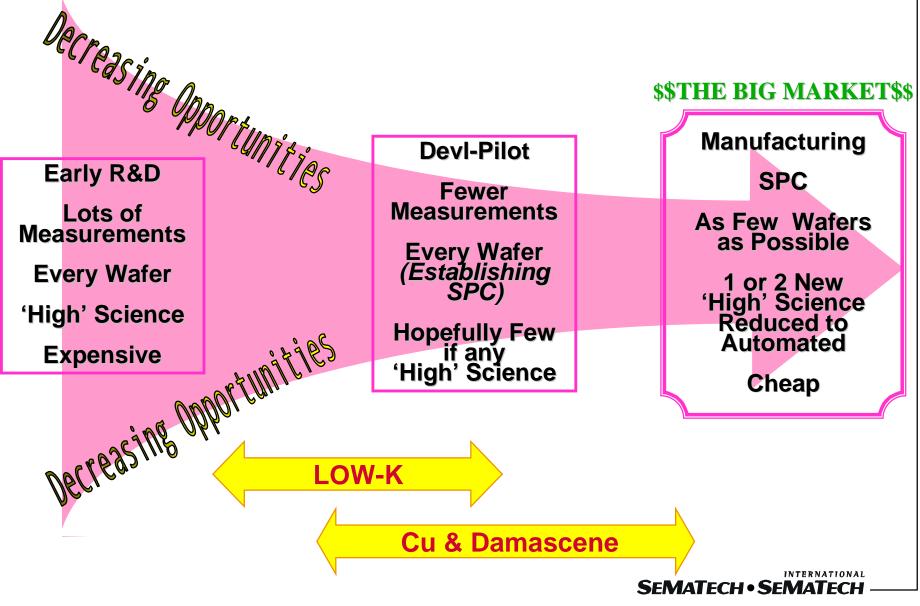

#### IMPACT OF CU, LOW-K, DAMASCENE ON CAPITAL EQT AND MATERIALS SUPPLIERS

• All of the Interconnect Materials Are Being Changed

•Many of the Process Techniques Are Being Changed, Therefore Most of the Equipment Set Is Impacted

> BUT There Are Market and Financial Forces Against All of This Change

•Interconnects Comprise 1/2 the Cost of Building an IC, There Is a Large Investment in Money, Knowledge and Experience by Both the Customers and Suppliers in the Current Equipment and Methods

•Suppliers of the Current Interconnect Equipment Set Are Among the Biggest and Most Successful

## A WORD ABOUT METROLOGY

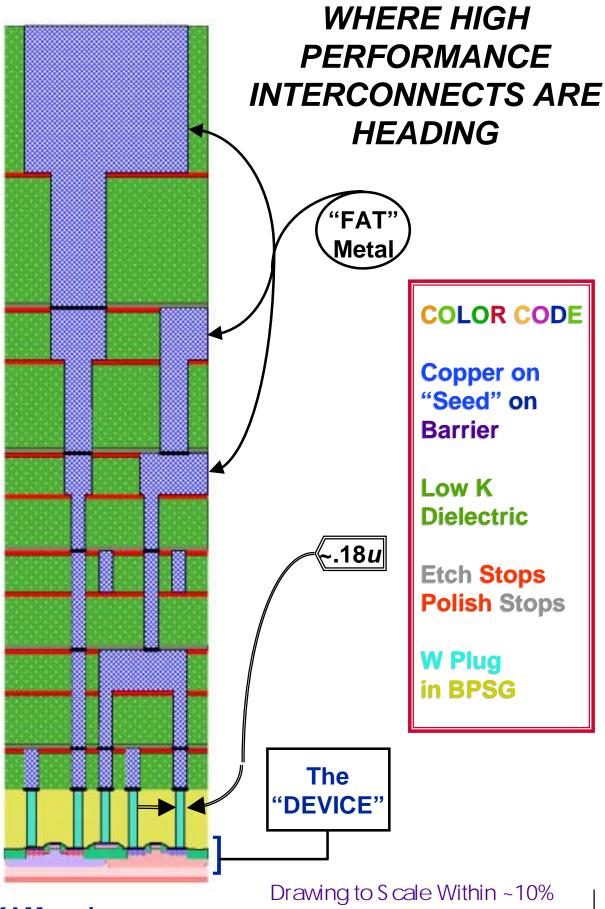

## **INTERCONNECT TOOL CHANGES;** *Metal*

VS

**Traditional Flow**

Metal-2 Metal-1 Metal-1

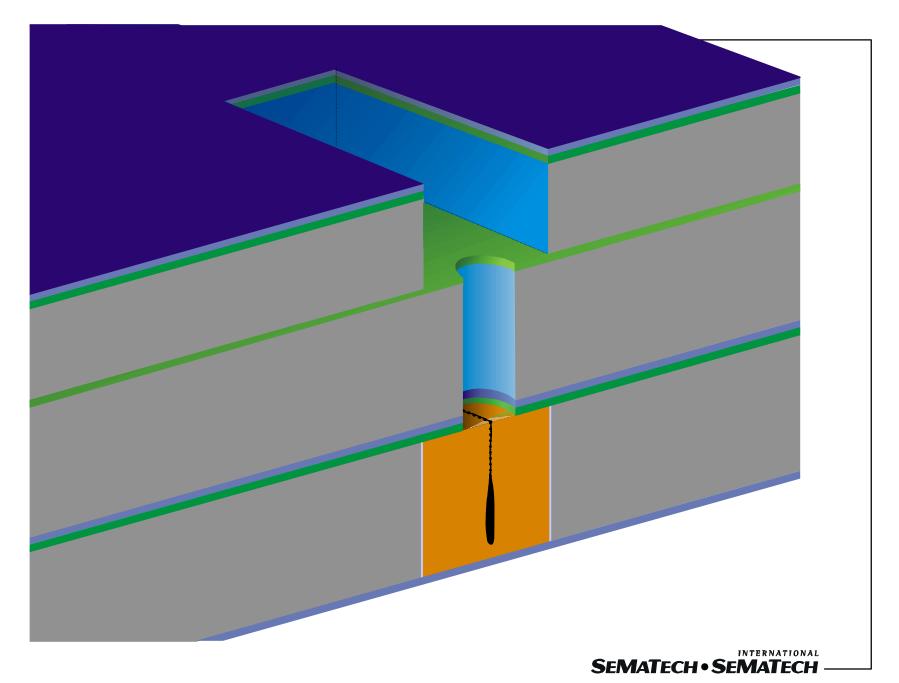

**Dual Damascene**

•PVD Ti Based Barrier wi PVD Al/Cu Line

•PVD TiN Barrier CVD-W Via Plug

•PVD TaN wi PVD Cu 'Seed' ElectroPlated Cu

•Via Plug and Line Metal merged into 1 operation

**Projected Toward**

CVD Barrier and/or CVD Cu Seed, maybe CVD Cu Fill

Precursors Likely to be Organo- Metallics wi maybe FI, CI, Br, I

SEMATECH • SEMATECH

INTERNATIONAL

#### **TECHNOLOGY** IMPACTS ON TOOL MARKET

**TOOL/TECHNOLOGY**

PVD (\$890M, 1998)\* (\$1.24B, 1999)\*\* **PLAYERS**

AMAT / Anlv / Nvls TEL / ULVAC

#### **TRENDs: Down**

•PVD 'Slab AI" Supplanted by Cu Plate &/or CVD (ECD; 1998@ \$61M, 1999@ \$76M)\*\*

•W Plug CVD Supplanted by Cu Plate &/or CVD

•PVD TiN Supplanted by PVD Cu, Ta-TaN then by CVD

•PVD Barrier and Seed wi Cu Plate will continue at upper-coarser levels

\*"Semiconductor Equipment, Manufacturing, and Materials Worldwide"; Dataquest; June, 7, 1999

\*\* "Semiconductor Equipment, Manufacturing, and Materials Worldwide"; Dataquest; June, 26, 2000

07/07/2000 13:52 KAMAVS10/99-15

INTERNATIONAL

SFMATECH • S

#### **TECHNOLOGY IMPACTS ON TOOL MARKET**

TOOL/TECHNOLOGY

PLAYERS

CVD (\$??M, 1998) Metals AMAT / Nvis / TEL

**TRENDs: What People Think They Want**

• CVD Barriers

•CVD Cu Seed

#### **Metrology Needs**

#### **Metal Deposition**

## FA#99083107 W#9061606-19E .170um Trenches. FA#99083107 W#9061606-19E .170um Trenches. 1111 4.0mm ×10.0k SE( MH-S4700 5.0kV 3.8mm x40.0k SE(U) 9/1/99 750nm FA#99083107 W#9061606-19E .190um Trenches. FA#99083107 W#9061606-19E .190um Trenches. 1111111111 \$4700 5.0kV 40mm x10.0k 9 MH-S4700 5.0kV 3.8mm x40.0k SE(U) 9/1/99 750nm INTERNATIONAL

#### Depletion Study: 4378 Amp-min, after 750 ml Bleed/Feed

07/07/2000 13:52 KAMAVS10/99 - 18

SEMATECH • SEMATECH

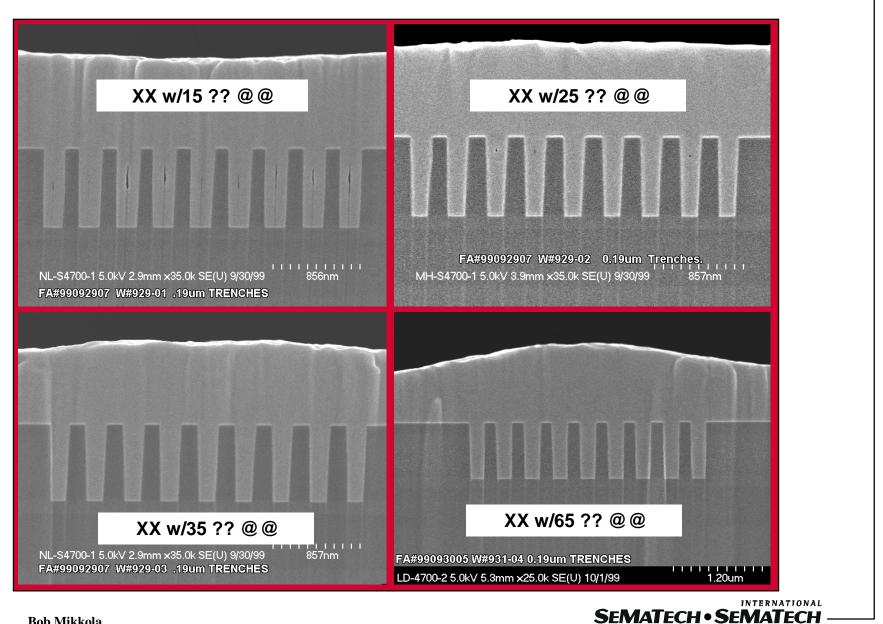

#### Effects of @ @ Levels on Fill

**Bob Mikkola**

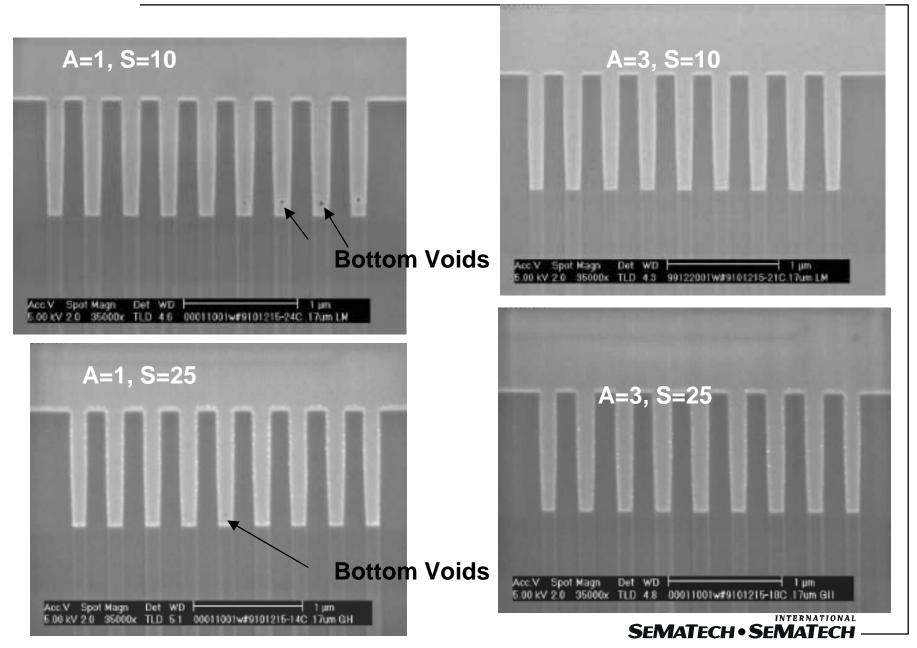

#### Additive Experiment (25 ?? @ @)

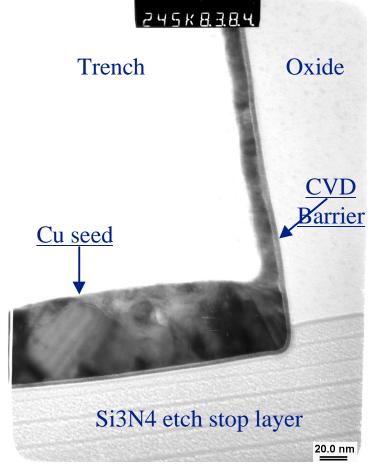

## **TEM Image Of CVD CVD Barrier** (100Å CVD Barrier + 1000Å 'Enhanced PVD' Cu seed)

$0.25\mu m$  AR ~ 3.0:1 Right edge

- Image shows good conformality of barrier (step coverage is ~69.4% on sidewall & 59.2% at bottom).

- Cu seed should be sufficient for plating (step coverage is ~ 11.0% on sidewall & 55.9% at bottom).

- Issues with sample prep at SEMATECH and Accurel.

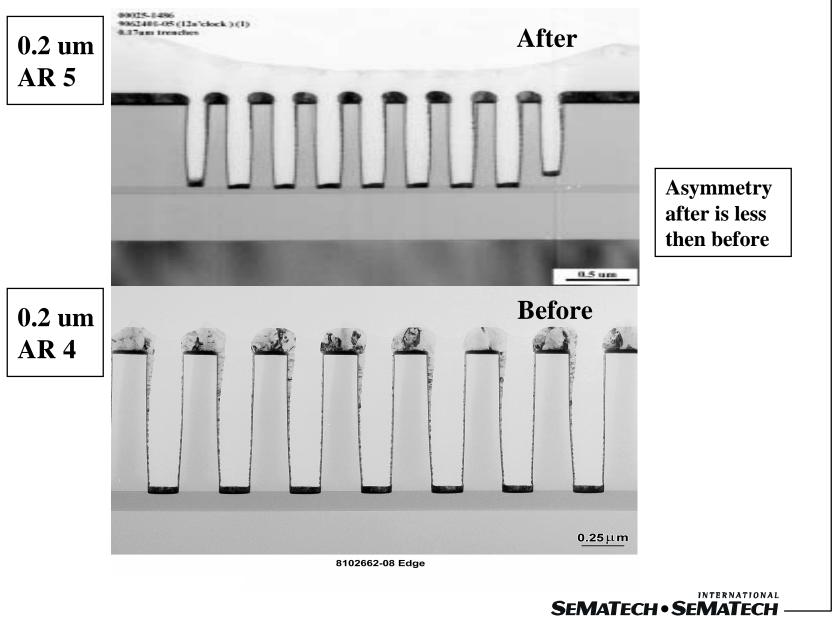

#### **Comparison stepcoverage "Before" & "After"**

## **Cu Diffusion**

#### Cu diffuses into Low K through sidewall

Metrology Things We Can't Do -

**Metal Deposition**

## •Barrierness

# •Reliability

Have to Build a Complete Device and Life Test

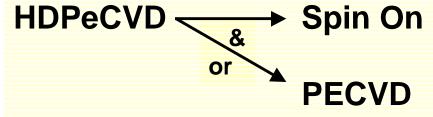

# INTERCONNECT TOOL CHANGES; Dielectrics Traditional Flow VS Dual Damascene Metal-1 Metal-1

High Density Plasma CVD SiO2 wi strong 'resputter' component for Gap Fill

Metal-1

Metal-1

Capped with Low Density PECVD SiO2

**Planarized with CMP**

Planar CVD SiO2, wi (usually PE)CVD Stop/Mask/Arc Layers Ideally CMP not Needed

**Projected Toward**

Low-K Dielectrics, Either CVD or Spin On, wi (usually PE)CVD Stop/Mask/Arc Layers Ideally CMP not Needed

At Least 2 Cycles

### **<u>TECHNOLOGY</u>** IMPACTS ON TOOL MARKET

TOOL/TECHNOLOGYPLAYERSCVD(\$886M, 1998)\*AMAT / ASM / NvIs

#### **TRENDs: 'Neutral' to Down but 'Easier'**

•Reduced Need for High Density Plasma

(\$1.34B, 1999)\*\*

Dielectric

•CVD Could be Supplanted in Whole or in Part by Spin on Technology (SOD; 1997@ \$116M, 98@ \$60M, 99@ \$68M)\*\*

\*"Semiconductor Equipment, Manufacturing, and Materials Worldwide"; Dataquest; June, 7, 1999 \*\*"Semiconductor Equipment, Manufacturing, and Materials Worldwide"; Dataquest; June, 26, 2000 **SEMATECH**•

07/07/2000 13:52 KAMAVS10/99 - 26

INTERNATIONAL

#### **Metrology Needs**

#### **Dielectric Deposition**

We Can Measure Some Things Pretty Well in Multiple Layers:

Planar Film:

•Thickness (Uniformity) •Refractive Index Now Measure; <u>A Whole Host of Things:</u> •Dielectric Constant •CTE •Modulus •Adhesion •Fracture Toughnesss •Thermal "Stability" •Moisture Uptake •Morphology •Composition •etc. etc.

Don't Know How Many Will Be Carried into Production

#### **Thermal Annealing and Cu Diffusion**

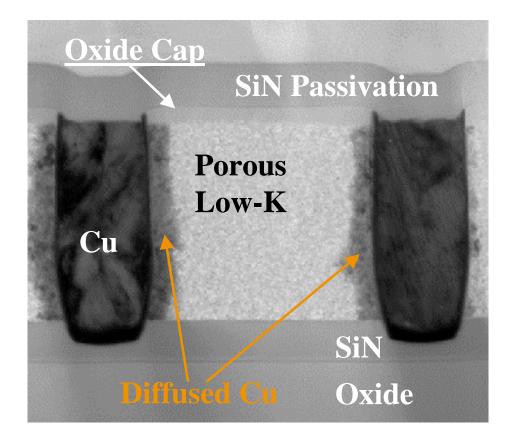

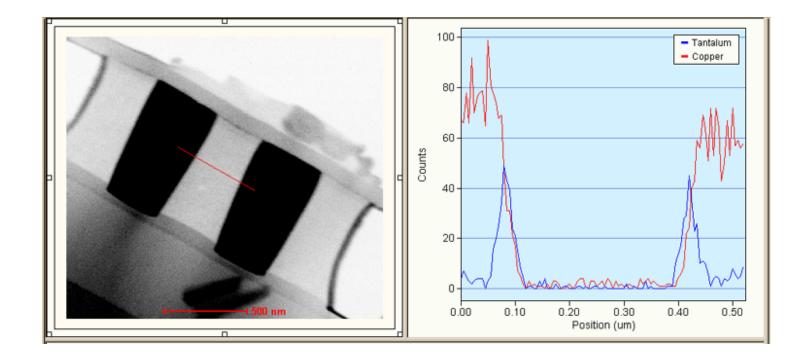

Bright-field TEM image of 0.35  $\mu$ mL/0.40  $\mu$ mS VHORG. Cu diffusion into the porous low-k was confirmed by EDX line profiles. The wafer was annealed 4 times at 400°C for 1 hour.

#### **P 3: M1 Module Screening:**

• **BF-STEM Image and EDS profile of Porous OSG**

- No Cu diffusion into low-k dielectric was detected.

Metrology Things We Can't Do

### **Dielectric Deposition**

## **Porosity**

•Only Measure Open Cell •Can't Measure Distribution The Search for the "Killer Pore" There are ~10<sup>13</sup> Pores/die (and rising)

## Adhesion

•A Generic Problem in Semiconductor Manufacturing •More Problematic (now) For Dielectrics

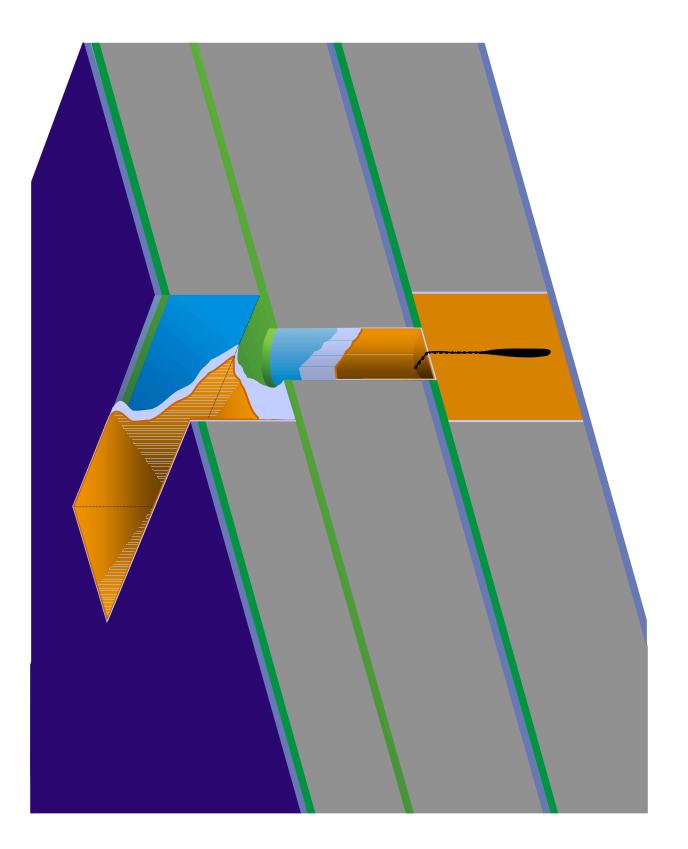

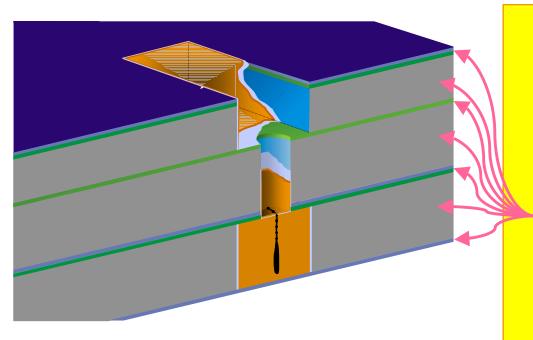

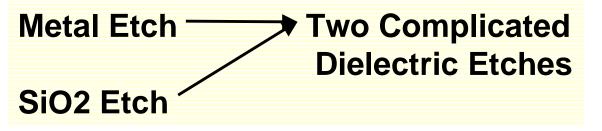

# INTERCONNECT TOOL CHANGES; Etch & Strip Traditional Flow VS Dual Damascene Metal-1 Metal-1 Metal-1 Metal-1 Metal-1 Metal-1

Metal Plasma Etch Passivation (Dry and/or Wet) Strip (Dry and/or Wet)

Dielectric Plasma Etch Strip (Dry and/or Wet)

- No Cu Plasma Etch Metal CMP

- 2 Dielectric Plasma Etchs Tools Don't Change Much Selectivity Rqmnts Tougher Flourocarbons, O2, Ar, N2

- Strip (Dry and/or Wet) Tough Chemistry Rqmnts May see Reducing Chemistry

07/07/2000 13:52 KAMAVS10/99 - 31

INTERNATIONAL

SFMATECH • SEMATECH

#### **<u>TECHNOLOGY</u>** IMPACTS TOOL ON MARKET

TOOL/TECHNOLOGY PLAYERS

Dry Etch (\$1.88B, 1998)\* (\$2.4B, 1999)\* AMAT / Hitachi LAM / TEL

#### TRENDs: 'Neutral' to a 1st Approximation and 'Easier'

•Metal Etch Eliminated but

•Two Complicated Dielectric Etches per Metal Layer

•Still Medium to High Density Plasma

\*"Semiconductor Equipment, Manufacturing, and Materials Worldwide"; Dataquest; June, 7, 1999 \*\*"Semiconductor Equipment, Manufacturing, and Materials Worldwide"; Dataquest; June, 26, 2000 **SEMATECH**•

INTERNATIONAL

### **<u>TECHNOLOGY</u>** IMPACTS ON TOOL MARKET

#### TOOL/TECHNOLOGY

Dry Strip (\$324M, 1997)\* Strip (\$162M, 1998)\*\* (\$227M, 1999)\*\* **PLAYERS**

Alcn / Gsnc / Etn Mttsn / KEM

#### **TRENDs: "Insufficient Data Captain Kirk"**

Process (Particularly wi Low K) Not Yet Well Enough Defined

\*"Semiconductor Equipment, Manufacturing, and Materials Worldwide"; Dataquest; June, 7, 1999

\*\* "Semiconductor Equipment, Manufacturing, and Materials Worldwide"; Dataquest; June, 26, 2000

SEMATECH • SEMATECH -

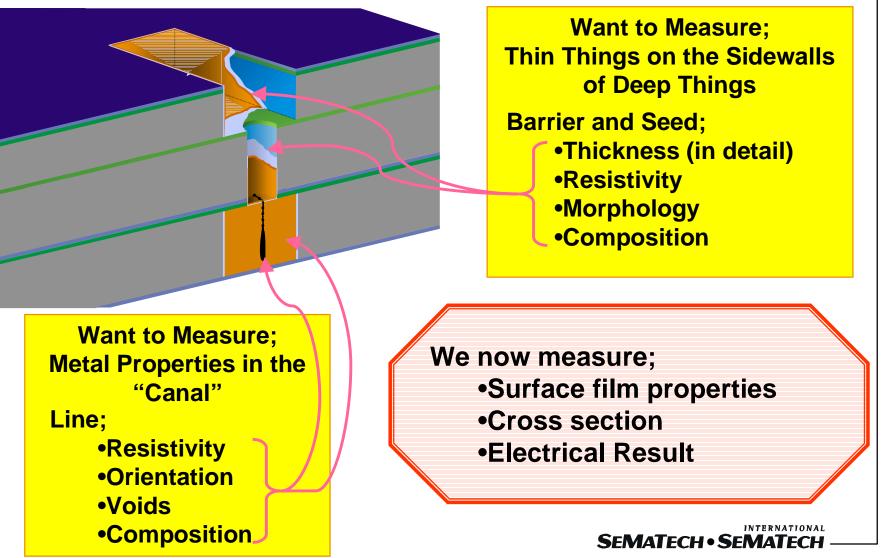

## Metrology Needs

#### **Etch & Strip**

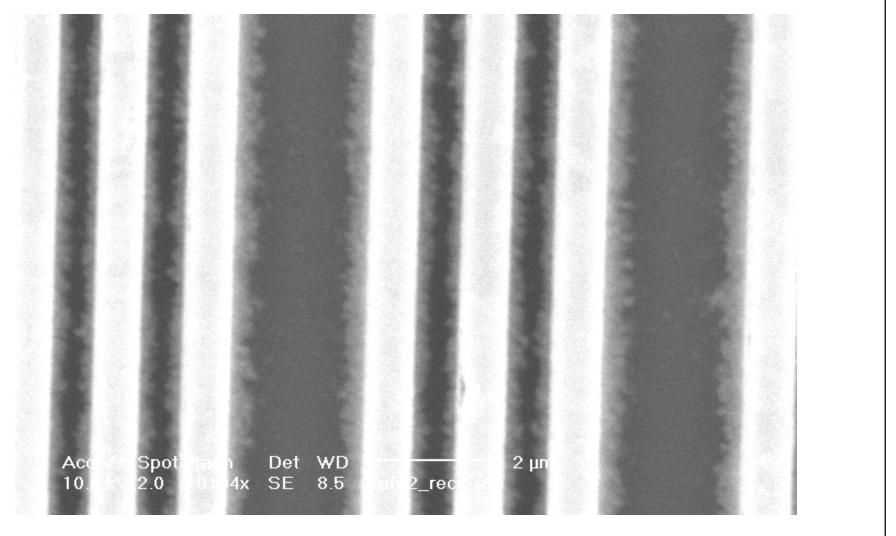

Want to Measure; Thin Things on the Sidewalls and Bottoms of Deep Things •Feature Size (in detail) •Profile •Residues •Low-K 'Attack' •Alignment •"Depth" •Faceting

We now measure; •Cross section •Electrical Result

Etch Development is Paced by SEM/TEM Time

SEMATECH • SEMATECH —

INTERNATIONAL

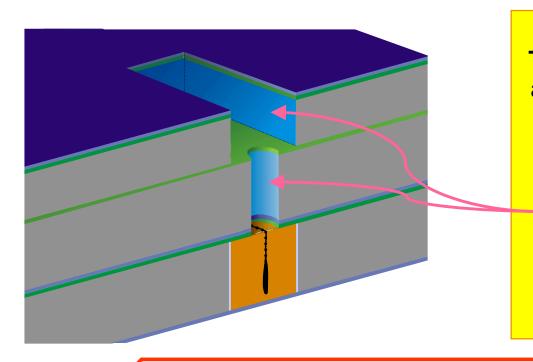

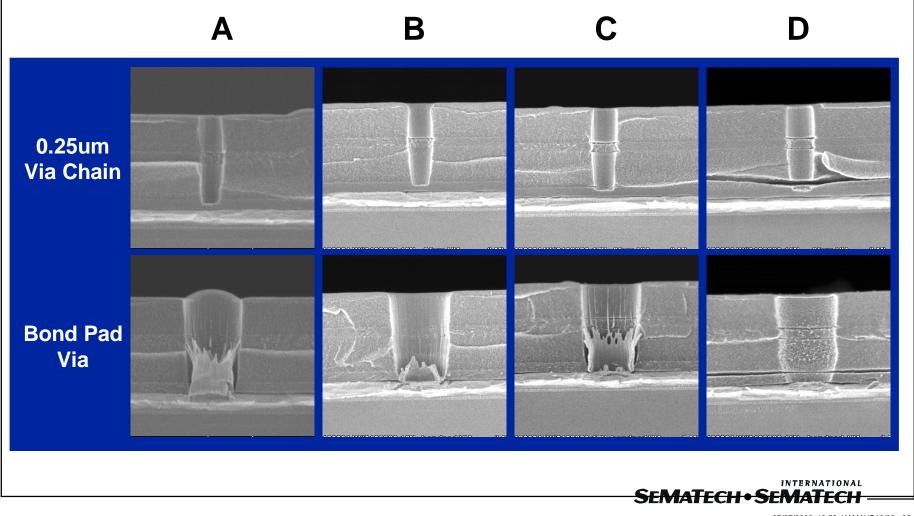

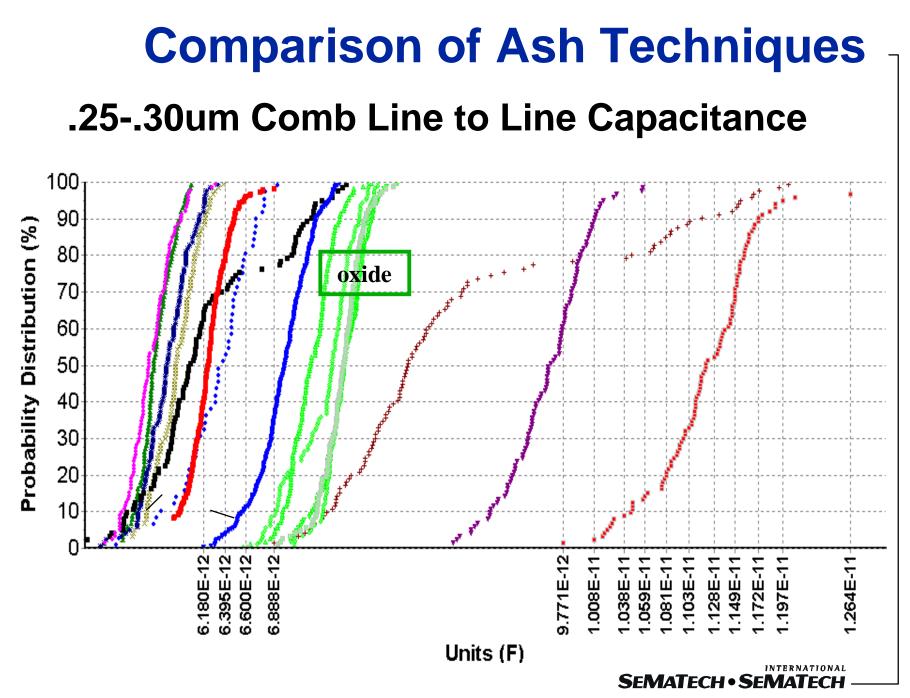

# Ash of %%%% Dual Damascene Via

• Exposed Cu presents an additional challenge for ash

## Low-K Damage

Note areas at sidewall with appearance of higher density (perhaps due to etch/ash damage).

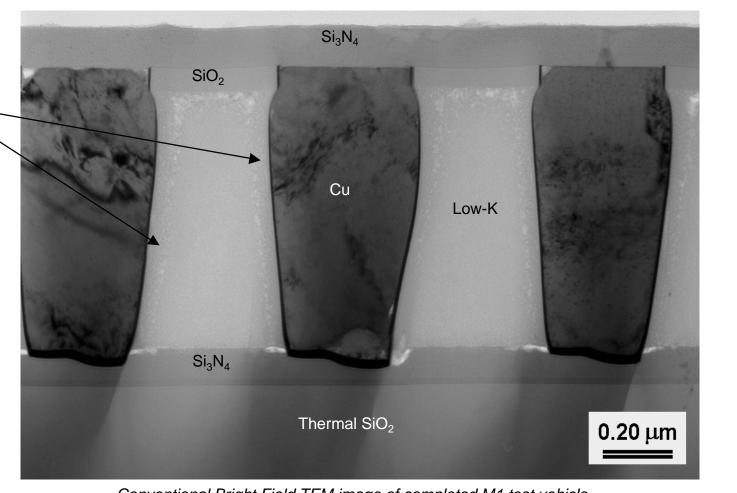

Conventional Bright Field TEM image of completed M1 test vehicle incorporating Low-K **after TC1** (400°C, 1 hr.) anneal.

Acknowledgement: B. Foran, D. Brazeau (SEMATECH)

SEMATECH • SEMATECH

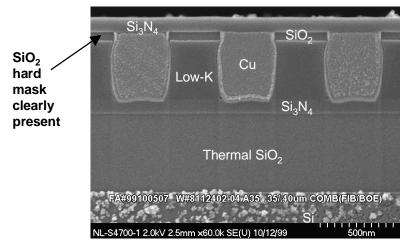

## **Another Low-K wi Damage**

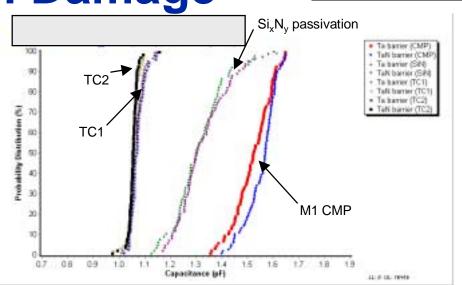

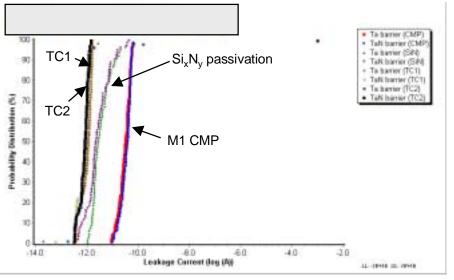

#### • Electrical data

- Capacitance and leakage current decrease (shown in probability plots at right for 4 sequential electrical test steps) upon passivation and continued thermal cycling

- Consistent with moisture desorption, at least through Si<sub>x</sub>N<sub>y</sub> passivation

- Mechanism for capacitance decrease upon TC1, TC2 unknown

XSEM image (FIB/BOE) of completed 0.35µmL/0.40µmS COMB structure **after TC2**.

Capacitance probability plot for 4 sequential etest steps.

Leakage current probability plot for 4 sequential etest steps.

07/07/2000 13:52 KAMAVS10/99 - 37

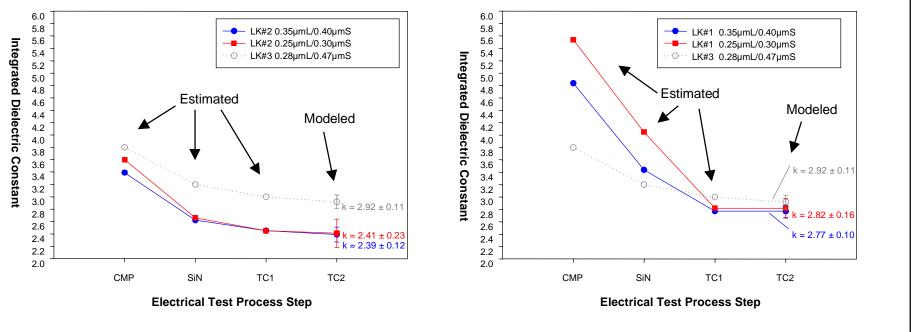

## **Integrated Dielectric Constants**

#### LK#2 (Rev. 8/98)

Blanket film (1 MHz) k = 2.09 ± 0.26 15% Si. 28% O. 16% C. 41% H Moisture uptake (wt.%, NIST) = 12.0 Average mass density  $(q/cm^3) = 1.087$ NIST measured "wall" density  $(q/cm^3) = 1.250$ Porosity (vol.%, assuming measured wall density) = 13.0 Average pore size (Å) = 3.2 - 11.0Pore connectivity (%) = 100Further comments / issues: Thickness cracking threshold, "stress-corrosion" cracking

Integrated Dielectric Constant by Process Step

#### LK#1

Blanket film (1 MHz) k = 2.201 ± 0.014 20% Si, 35% O, **11% C**, 34% H Moisture uptake (wt.%, NIST) = 65.0Average mass density  $(q/cm^3) = 0.886$ NIST measured "wall" density (g/cm<sup>3</sup>) = 2.103 Porosity (vol.%, assuming measured wall density) = 57.9 Average pore size (Å) = 11.9Pore connectivity (%) = 100Further comments / issues: Si-OH in blanket film FT-IR. trace metals

#### Integrated Dielectric Constant by Process Step

#### **TECHNOLOGY** IMPACTS ON TOOL MARKET

TOOL/TECHNOLOGY

CMP (\$632M, 1998)\* (\$1.02B, 1999)\*\* **PLAYERS**

AMAT / Ebara-Cybeq Speedfam-IPEC

SFMATECH • 9

#### TRENDs: 'Neutral' but Application Changing and 'Harder'

•Dielectric CMP Substituted by Cu CMP

•W Plug CMP Eliminated Except @ Contact Level

•May Still Need a 'Minor' Dielectric Planarization

\*"Semiconductor Equipment, Manufacturing, and Materials Worldwide"; Dataquest; June, 7, 1999

\*\* "Semiconductor Equipment, Manufacturing, and Materials Worldwide"; Dataquest; June, 26, 2000

#### SIMPLIFIED SUMMARY; Everything Could Change -

•For Circuit Performance Reasons the Materials Used to Fabricate IC Interconnects Need to Be Changed

•The Change to Copper Forces a Change to Damascene

•Damascene Fosters a Change Away From PVD Metal Toward Electroplate and or CVD

•Damascene and the Move Toward Lower Dielectric Materials Is Creating Changes in Dielectric Deposition

•As a Result of the Material and Process Technique Changes, All of the Manufacturing Tools Will Change in Some Fashion

•Given a Choice Anybody Who Manufacturers Anything (Successfully) Would Rather Not Do This.

#### 1999 SEMI "Copper-Critical" Survey, Results

265 industry respondents; 32% semiconductor manufacturers (merchant, captive, fabless and foundries) and consortia, majority in process development, R&D, or process engineering, 38% equipment, 11% material suppliers, 16% other.

#### SOME KEY FINDINGS

•Over 40% of IC manufacturers say that volume production of Cu-based semiconductors will reach 10% of total dollar shipments by 2001.

•Equipment suppliers' more enthusiastic on the readiness of the copper tool set are often inconsistent with IC manufacturers' views.

•Equipment suppliers' more conservative on the speed of copper adoption are often inconsistent with IC manufacturers' views.

•Logic devices will lead the way, with the majority of respondents indicating first Cu shipments by 2000. ASIC follows in 2001; memory and system-on-a-chip are viewed as lagging beyond 2003.

•Over 70% of respondents still depend on tungsten as the preferred contact plug (or via) material.