# The Interconnect Era of Gigascale Integration

International Conference on Characterization and Metrology for ULSI Technology Dallas, Texas March 16, 2005

# **ITRS Objectives**

| <u>Calendar Year</u>                    | <u>2012</u>     | <u>2018</u>            |

|-----------------------------------------|-----------------|------------------------|

| Interconnect One Half Pitch             | 35 nm           | <b>18 nm</b>           |

| <b>MOSFET Physical Gate Length</b>      | 14 nm           | 7 nm                   |

| Hi Perf. MPU Transistors/Chip           | 3.5 billion     | 14 billion             |

| <b>DRAM</b> Bits/Chip (at introduction) | <b>32 Gb</b>    | 128 Gb                 |

| Number of Interconnect Levels           | 12-16           | 14-18                  |

| <b>On-Chip Local Clock</b>              | <b>20 GHz</b>   | <b>53 GHz</b>          |

| Chip-to-Board Clock                     | 15 GHz          | <b>56 GHz</b>          |

| # of Hi Perf. ASIC Signal I/O Pads      | 2500            | 3100                   |

| # of Hi Perf. ASIC Power/Ground Pads    | 2500            | 3100                   |

| Supply Voltage                          | 0.7-0.9 Volts   | 0.5-0.7 Volts          |

| Supply Current                          | 283-220 Amperes | <b>396-283</b> Amperes |

| Hi Perf. Chip Power Dissipation         | (240)198 Watts  | (300)198 Watts         |

| [ 2003 ITRS, 2004 ITRS ]                |                 |                        |

# Interconnects are projected to become

# the principal determinants of the

latency, energy consumption and cost

of gigascale silicon chips.

# **INTERCONNECT FOCUS CENTER**

International Conference on Characterization and Metrology for ULSI Technology Dallas, Texas March 16, 2005

#### **Faculty PI and Student Participation in IFC- Participation by Site**

|                                   | PI's | Students |

|-----------------------------------|------|----------|

| Stanford                          | 10   | 18       |

| MIT                               | 13   | 31       |

| SUNYA                             | 9    | 20       |

| Rennselaer                        | 9    | 31       |

| Georgia Institute of Technology** | 7    | 19       |

| Cornell                           | 1    | 3        |

| UC Santa Barbara                  | 1    | 2        |

| UT Austin                         | 1    | 1        |

| UCF                               | 2    | 2        |

| Carnegie Mellon                   | 1    | 2        |

| NCSU                              | 3    | 2        |

| <u>UC Berkeley</u>                | 3    | 2        |

| <b>Total Participation</b>        | 60   | 133      |

\*\*Lead University

# **Interconnect Focus Center**

# Leadership Council

Prof. Alain Kaloyeros

Prof. James Meindl

Prof. Pulickel Ajayan

Prof. Anantha Chandrakasan

Prof. David A. B. Miller

SUNY at Albany

Georgia Tech

RPI

MIT

Stanford

\* Chairman

| Interconnect Focus Center                                                   |                                                                                 |                                                                                       |  |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|

|                                                                             | Program Matrix                                                                  |                                                                                       |  |

|                                                                             | Driver 1<br>High Performance Network Chips<br><i>Krishna Saraswat, Stanford</i> | Driver 2<br>Low-Energy Mixed-Signal Wireless Node<br><i>Anantha Chandrakasan, MIT</i> |  |

| Task 1<br>Electrical Interconnects<br>Alain Kaloyeros, SUNYA                |                                                                                 |                                                                                       |  |

| Task 2<br>Optical Interconnects<br>David Miller,Stanford                    |                                                                                 |                                                                                       |  |

| Task 3<br>Thermal Management &<br>Power Delivery<br>Paul Kohl, Gerogia Tech |                                                                                 |                                                                                       |  |

| Task 4<br>Circuit & System Design &<br>Modeling<br><i>Duane Boning, MIT</i> |                                                                                 |                                                                                       |  |

| Interconnect Focus Center                                              |                                                                      |                                                                                  |  |

|------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------|--|

|                                                                        | Program Matrix                                                       |                                                                                  |  |

|                                                                        | Driver 1<br>High Performance Network Chip<br><i>Krishan Saraswat</i> | Driver 2<br>Low-Energy Mixed Signal Wireless Node<br><i>Anantha Chandrakasan</i> |  |

| Task 1<br>Electrical Interconnects<br><i>Alain Kaloyeros</i>           |                                                                      |                                                                                  |  |

| Task 2<br>Optical Interconnects<br><i>David Miller</i>                 |                                                                      |                                                                                  |  |

| Task 3<br>Thermal Management &<br>Power Delivery<br><i>Paul Kohl</i>   |                                                                      |                                                                                  |  |

| Task 4<br>Circuit & System Design &<br>Modeling<br><i>Duane Boning</i> |                                                                      |                                                                                  |  |

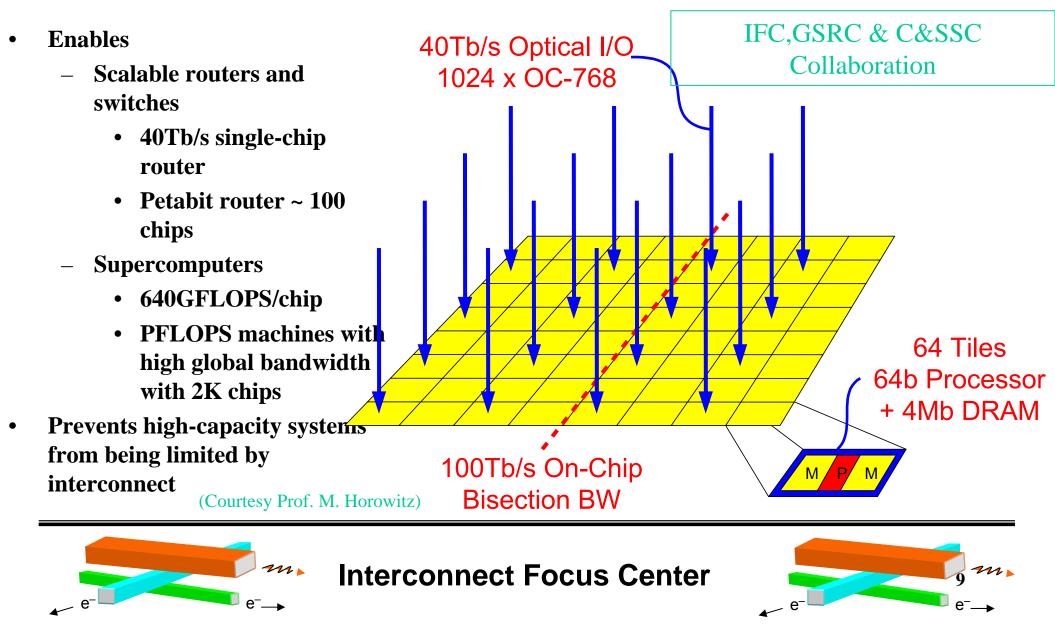

# A High Performance(40Tb/s) Computing/Communication Chip

| Interconnect Focus Center                                              |                                                                      |                                                                           |  |

|------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------|--|

|                                                                        | Program Matrix                                                       |                                                                           |  |

|                                                                        | Driver 1<br>High Performance Network Chip<br><i>Krishna Saraswat</i> | Driver 2<br>Low-Energy Mixed Signal Wireless Node<br>Anantha Chandrakasan |  |

| Task 1<br>Electrical Interconnects<br><i>Alain Kaloyeros</i>           |                                                                      |                                                                           |  |

| Task 2<br>Optical Interconnects<br><i>David Miller</i>                 |                                                                      |                                                                           |  |

| Task 3<br>Thermal Management &<br>Power Delivery<br><i>Paul Kohl</i>   |                                                                      |                                                                           |  |

| Task 4<br>Circuit & System Design &<br>Modeling<br><i>Duane Boning</i> |                                                                      |                                                                           |  |

# Low-Energy Mixed-Signal Wireless Node

#### Key Requirements: Integration of

- Diverse process technologies for *mixed signal* digital, analog, RF and MEMS chips

- Compact 3D form factor

- High performance, energy efficient computation and communication (Courtesy Prof. R. Reif)

| Interconnect Focus Center                                              |                                                                      |                                                                                  |  |

|------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------|--|

|                                                                        | Program Matrix                                                       |                                                                                  |  |

|                                                                        | Driver 1<br>High Performance Network Chip<br><i>Krishna Saraswat</i> | Driver 2<br>Low-Energy Mixed Signal Wireless Node<br><i>Anantha Chandrakasan</i> |  |

| Task 1<br>Electrical Interconnects<br>Alain Kaloyeros                  |                                                                      |                                                                                  |  |

| Task 2<br>Optical Interconnects<br><i>David Miller</i>                 |                                                                      |                                                                                  |  |

| Task 3<br>Thermal Management &<br>Power Delivery<br><i>Paul Kohl</i>   |                                                                      |                                                                                  |  |

| Task 4<br>Circuit & System Design &<br>Modeling<br><i>Duane Boning</i> |                                                                      |                                                                                  |  |

# **Interconnects Supersede Transistors : Latency**

| Technology<br>Generation           | MOSFET Switching<br>Delay, t <sub>d</sub> =CV/I | "RC"Response<br>Time, L <sub>int</sub> =1mm |

|------------------------------------|-------------------------------------------------|---------------------------------------------|

| 1.0 μm<br>(AI, SiO2)               | ~ 20 ps                                         | ~ 1 ps                                      |

| 100 nm<br>(Cu, κ=2.0)              | ~ 5 ps                                          | ~ 30 ps                                     |

| <mark>35 nm<br/>(Cu, κ=2.0)</mark> | <mark>~ 2.5 ps</mark>                           | <b>~ 250 ps</b> (best case)                 |

"Size Effects": Surface/Roughness & Grain Boundary Scattering of Electrons in Metal Interconnects Physics predicts no known methodology to eliminate quantum mechanical scattering at boundaries in ultra-narrow conductors

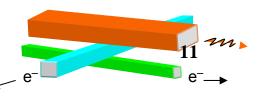

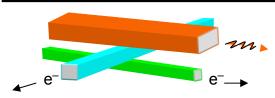

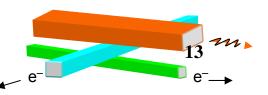

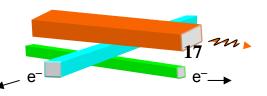

**Potential Solution: Interconnect Nanotechnology** Exploit novel nanoscale electronic transport phenomena, such as:

- Ballistic electron transport in nanotubes, carbon chains, and molecules.

- Conduction occurs via quantum channels.

- Potential for ballistic transport at localization lengths  $\geq 10~\mu m.$

(Courtesy of Prof. A. Kaloyeros)

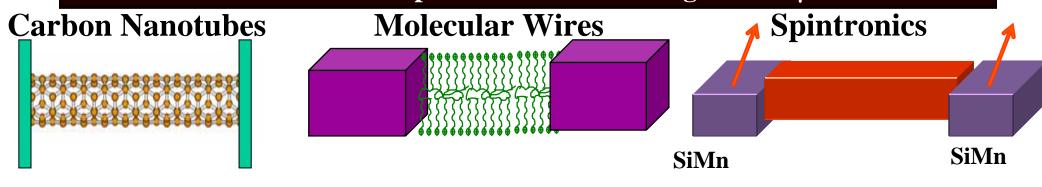

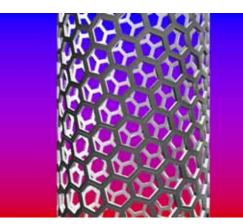

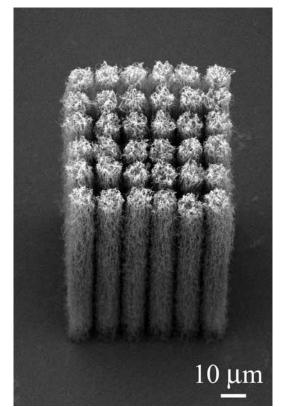

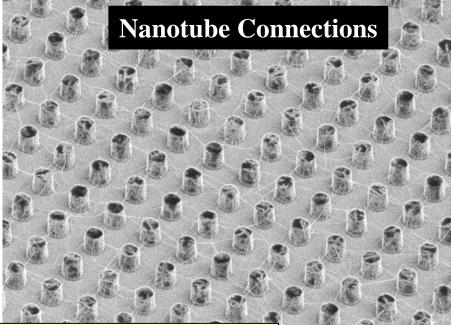

# **Designing Carbon Nanotubes for Interconnect Applications**

New Paradigm for Future Interconnect Technology

**3-D Architectures, Growth, Integration Tailoring Nanotube Structure, Properties Creating and Characterizing Junctions, Networks**

Why Carbon Nanotubes ?

•Low Resistivity

•Small Dimensions

•Mechanically Robust

•High Current Densities

•No Electromigration

•High Thermal Conductivity

(Courtesy Prof. P. Ajayan)

Interconnect Focus Center

2-30 nm

nm

**Near Perfect Nanotubes**

**Multiwalled and Singlewalled**

**Nanotube-Contacts**

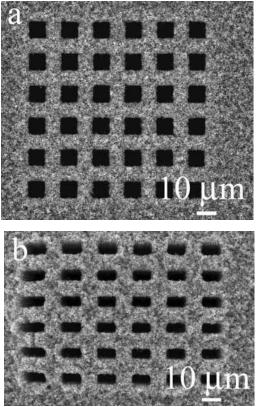

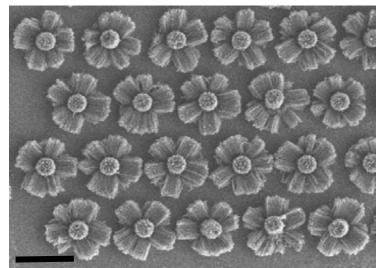

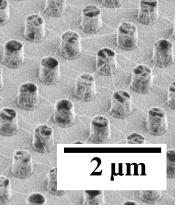

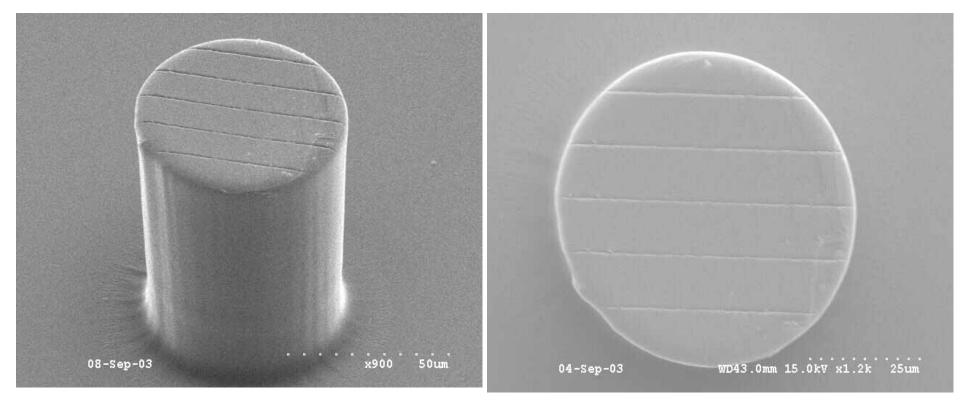

#### **Controlled Assembly of Carbon Nanotube Architectures for Interconnects**

#### **Directed Assembly Based on Substrate Selection**

MSDC & IFC Collaboration

## **Vertical and Horizontal**

**50** μm

SiO<sub>2</sub> layer on Si Substrate

**<u>Control</u>:** Location, Density, Orientation, Dimensions

(Courtesy Prof. P. Ajayan)

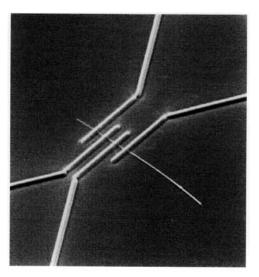

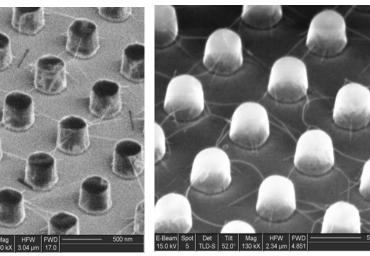

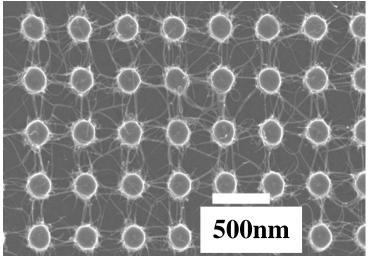

### **Demonstration of 2-D Carbon Nanotube Wiring Network**

Controlled Assembly of Multiple Connections Single-wall Nanotube Networks of Varying Density/Pitch

(Courtesy Prof. P. Ajayan)

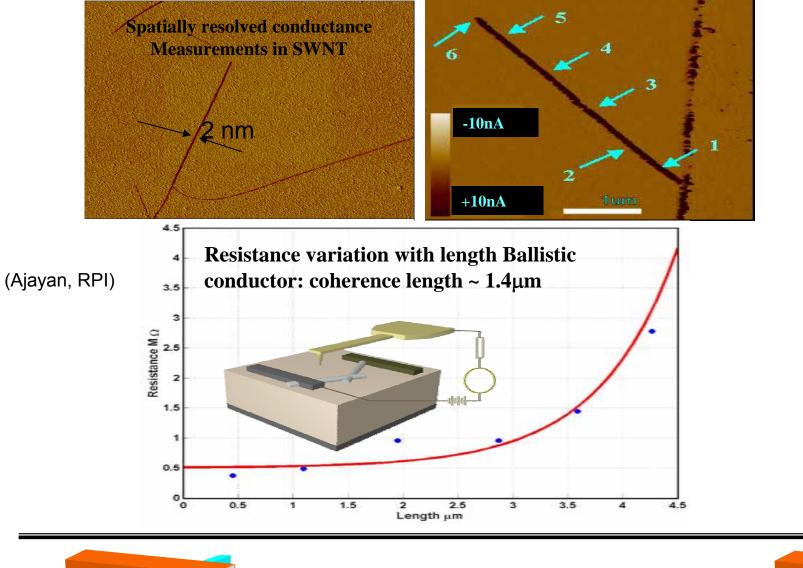

# **Carbon Nanotube Interconnects**

**Ideal Carbon Nanotubes versus Copper Wires in 2016 (22nm Node)**

Bundles of carbon nanotubes should be used for interconnect applications to avoid very slow signal propagation. (Naeemi, Meindl – GIT)

#### **Demonstration of CMOS Compatible Polypeptide Molecular Wire** Self-assembly of functional molecular **Metallic complexes for charge transport** building blocks using bottom-up science OH + directed assembly on patterned surfaces using top-down nanotechnology <u>6 nm</u> **Ala-Gly 'trellis': 1D crystal array** ίΑπ(Απ(Απ(Απ(Απ 250 `o<sup>-Si</sup> 100 150 200 50 nm **Alkylsilane linkage Alkylthiol linkages** for SiO<sub>2</sub> for metal attachment **Successful Directed Self-Assembly** attachment of Molecular Polypeptide Backbone

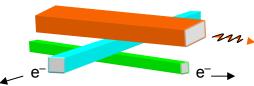

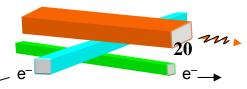

#### **Controlled Self-Assembly of Metal Nanoparticle/Polypeptide Interconnects**

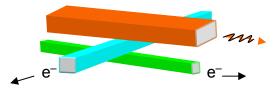

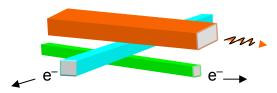

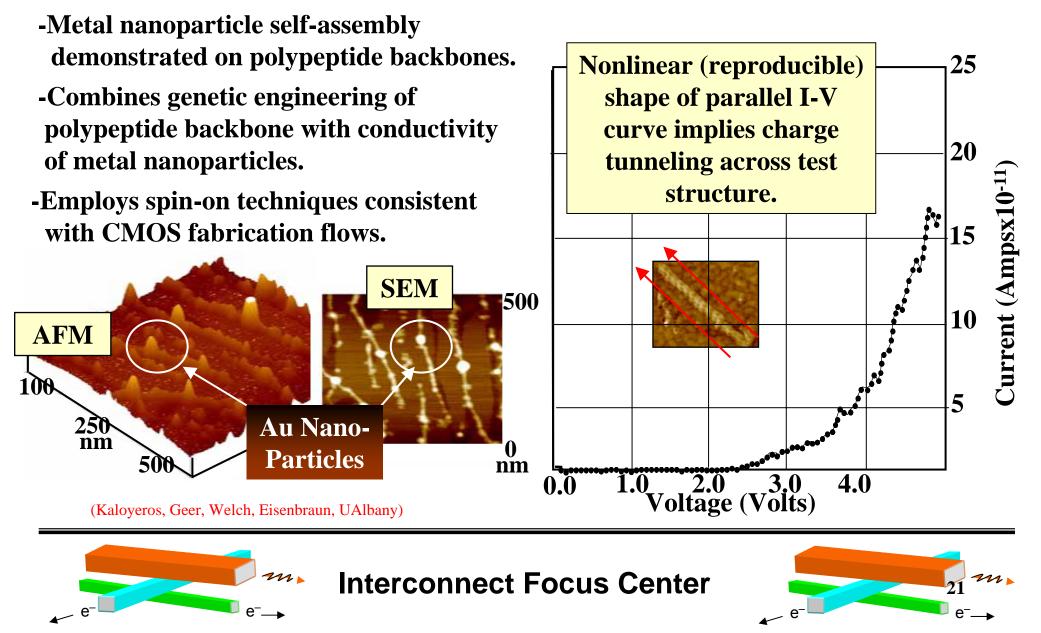

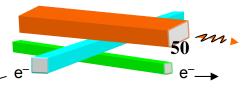

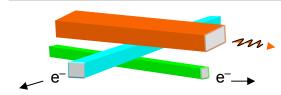

# **Spintronics: Signal transmission via electron spin packets**

| Interconnect Focus Center                                              |                                                                      |                                                                                  |  |

|------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------|--|

|                                                                        | Program Matrix                                                       |                                                                                  |  |

|                                                                        | Driver 1<br>High Performance Network Chip<br><i>Krishna Saraswat</i> | Driver 2<br>Low-Energy Mixed Signal Wireless Node<br><i>Anantha Chandrakasan</i> |  |

| Task 1<br>Electrical Interconnects<br><i>Alain Kaloyeros</i>           |                                                                      |                                                                                  |  |

| Task 2<br>Optical Interconnects<br>David Miller                        |                                                                      |                                                                                  |  |

| Task 3<br>Thermal Management &<br>Power Delivery<br><i>Paul Kohl</i>   |                                                                      |                                                                                  |  |

| Task 4<br>Circuit & System Design &<br>Modeling<br><i>Duane Boning</i> |                                                                      |                                                                                  |  |

# Critical Objectives

- Ultra-high bandwidth, high speed, high density chip-tochip and (subsequently on-chip) optical interconnects

- Interfacing gigascale Si chips(GSI) with optical networklike interconnects to enable "fiber-to-the-chip"

- Optical clock injection for GSI

- Implementation of the preceding advances with low voltage, low power, low cost optoelectronics

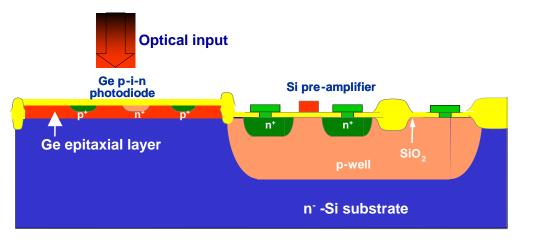

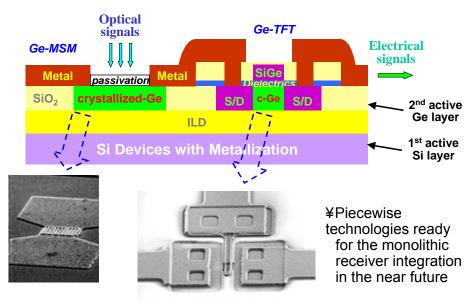

### **Integrated Optical Receivers: Ge**

CMOS Electronics and Ge PIN Photodiode

Successful fabrication of Ge PIN photodiodes on Si substrate

- Dark current: I<sub>d</sub> = 1 mA @10V; diameter = 24mm

- Responsivity: 0.57A/W @2V and I = 1.3 mm

- Bandwidth: 8 GHz @ 10V

Future plans

- Improve and optimize Ge PIN and adjacent CMOS devices

- Develop compatible process technology

(Campbell, UT-Austin)

Interconnect Focus Center

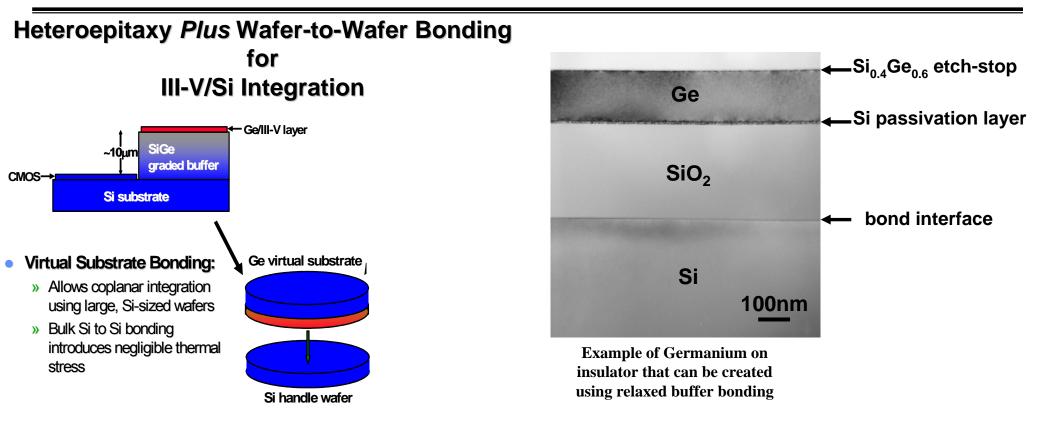

#### **3D Integration of Ge Optoelectronic Devices on Si**

- Employ recrystallization or layer transfer technique for Ge on Si

- Integration of optical receiver in the upper active (Ge) layer

- ⇒ On-chip optical clock distribution in 3D-ICs (Saraswat – Stanford)

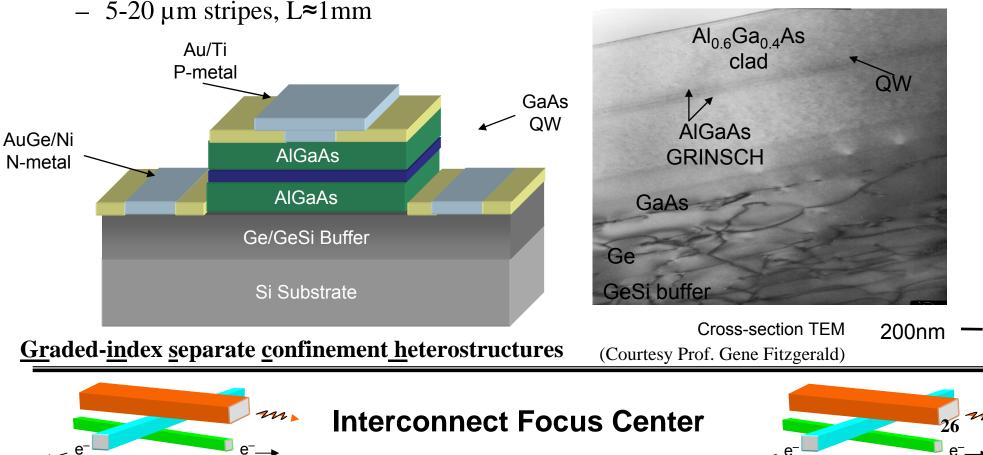

## Silicon-Compatible Laser Design (MOCVD Heteroepitaxy)

- AlGaAs/GaAs and AlGaAs/GaAs/InGaAs GRINSCH quantum well on Si substrate

- CW,  $28^{\circ}$ C operation for > four hours

- Uncoated gain-guided lasers, no heatsinking

- − 5-20  $\mu$ m stripes, L≈1mm

#### •Increase reliability of III-V lasers

•Low threadhold laser design

•Improved Ge/SiGe/Si relaxed buffers so that III-V's have even lower dislocation density

•Creation of substrate materials compatible with producing such devices with Si CMOS

•Use relaxed buffer bonding to create Si CMOS-compatible platforms with embedded optical planes

(Courtesy of Prof. E. Fitzgerald)

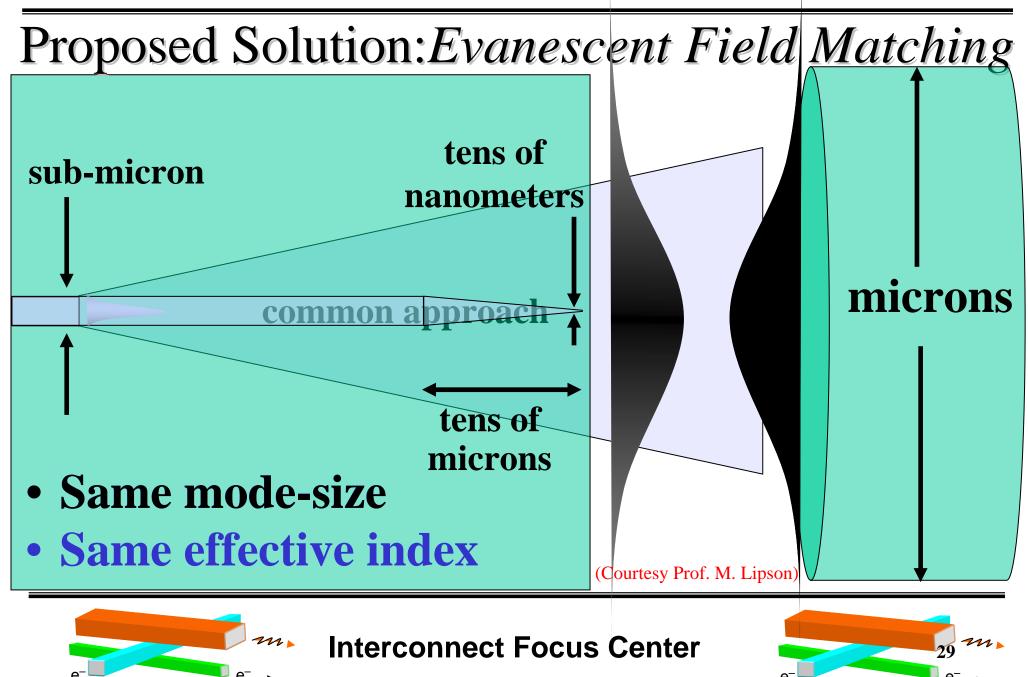

# Coupling from Fiber-to-the- Chip

**Silicon Chip**

**Optical Fiber**

# Silicon Waveguide (High refractive index)

Mode-size mismatch

**Effective index mismatch**

(Courtesy Prof. M. Lipson)

#### ~3% Transmission

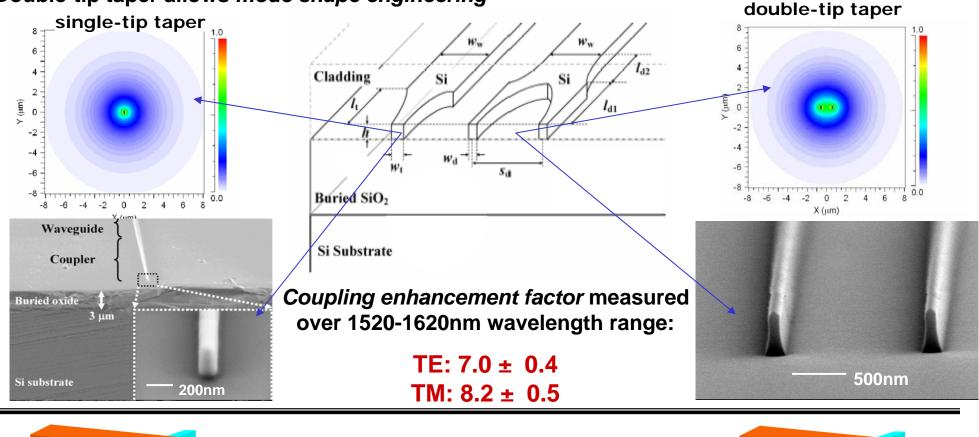

#### **Compact Optical Soldering: Nanotaper Coupler**

98% Efficient mode conversion achieved within only tens of µm :

- Mode field expands outside the high index core into the low index cladding thus matching both shape and effective index of fiber mode (Courtesy Prof. M. Lipson)

- Double-tip taper allows mode shape engineering

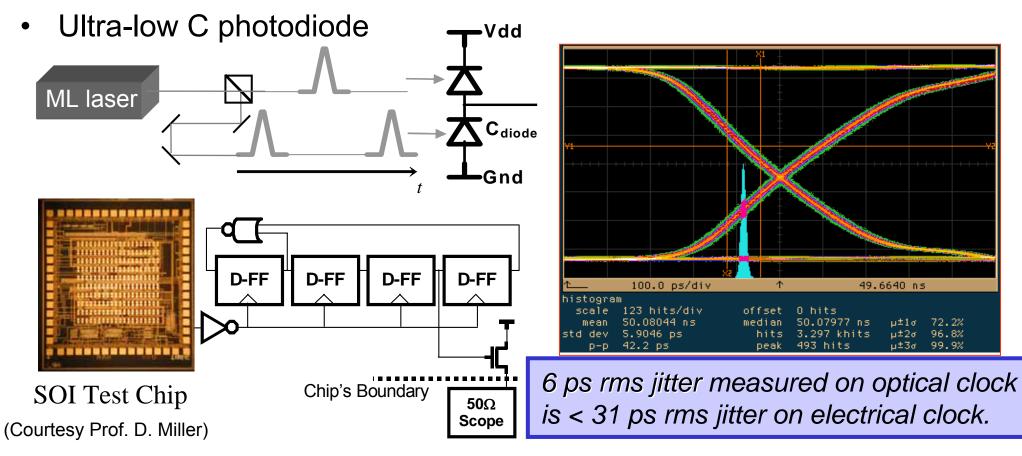

### **Optical Clock Injection Using Modelocked Short Pulse Lasers**

- Modelocked lasers can provide low-jitter, GHz clocks for electronics

- Receiver-less direct optical injection produces low-jitter digital clock

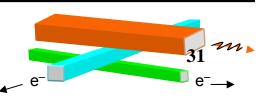

# **Mode-Locked Vertical Cavity Surface Emitting Laser**

| Interconnect Focus Center                                              |                                                                      |                                                                                  |  |

|------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------|--|

|                                                                        | Program Matrix                                                       |                                                                                  |  |

|                                                                        | Driver 1<br>High Performance Network Chip<br><i>Krishna Saraswat</i> | Driver 2<br>Low-Energy Mixed Signal Wireless Node<br><i>Anantha Chandrakasan</i> |  |

| Task 1<br>Electrical Interconnects<br><i>Alain Kaloyeros</i>           |                                                                      |                                                                                  |  |

| Task 2<br>Optical Interconnects<br><i>David Miller</i>                 |                                                                      |                                                                                  |  |

| Task 3<br>Thermal Management &<br>Power Delivery<br><i>Paul Kohl</i>   |                                                                      |                                                                                  |  |

| Task 4<br>Circuit & System Design &<br>Modeling<br><i>Duane Boning</i> |                                                                      |                                                                                  |  |

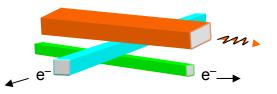

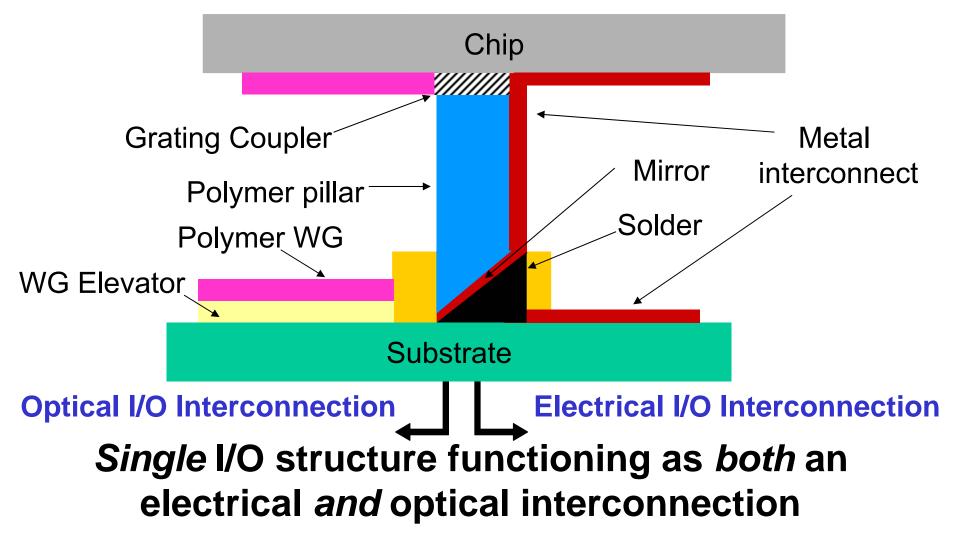

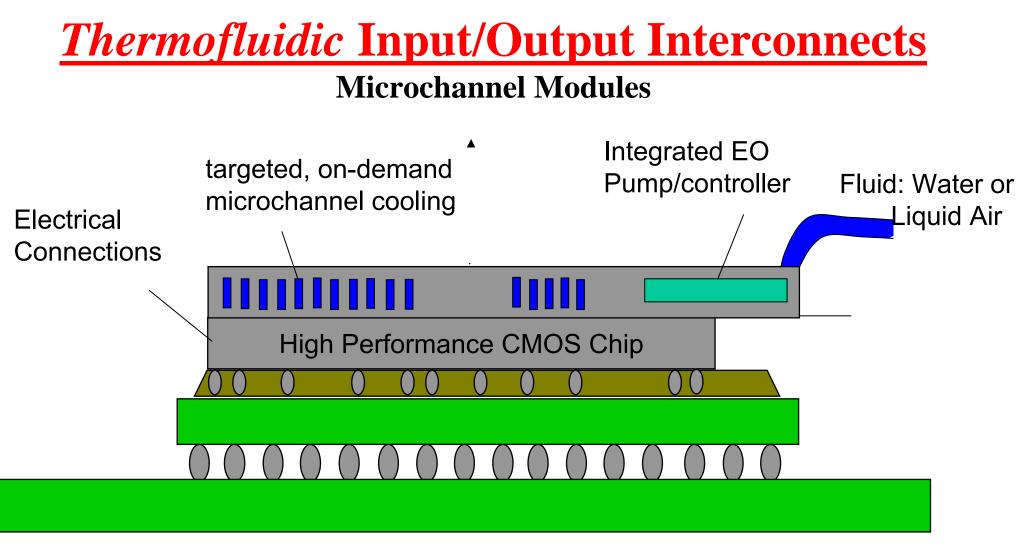

Singular Objective:

# Wafer Level, Batch Fabricated, High Density, Compliant,

# **Compatible Electrical, Optical & Thermofluidic**

# **Input/Output Interconnects**

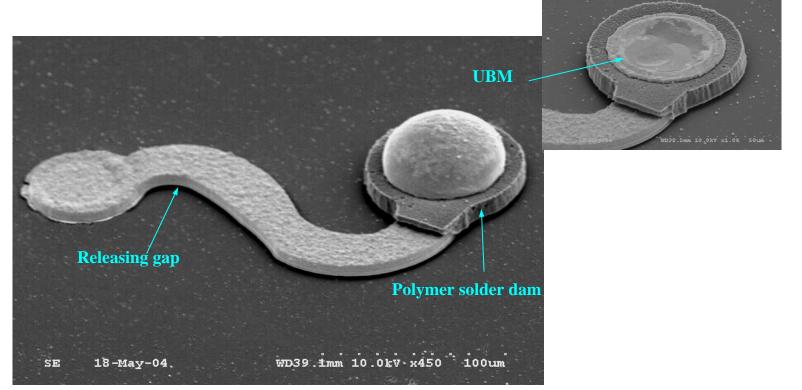

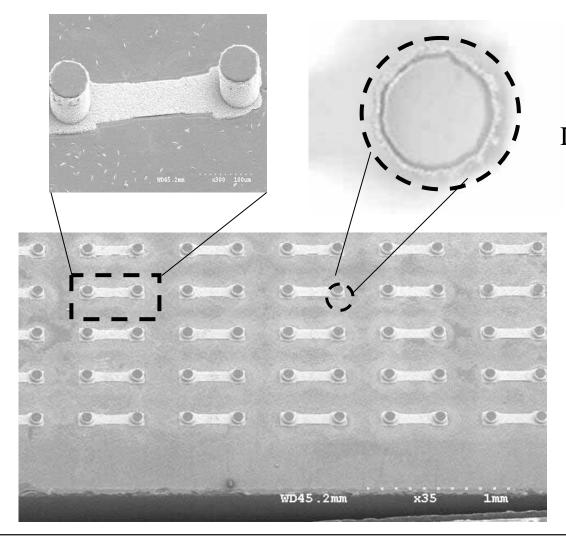

# **Advanced SoL Compliant Interconnects**

□ Complete bumping solution includes:

- Solder dam to protect the metal leads (wicking)

- Ni-UBM as a reliable soldering base for C4

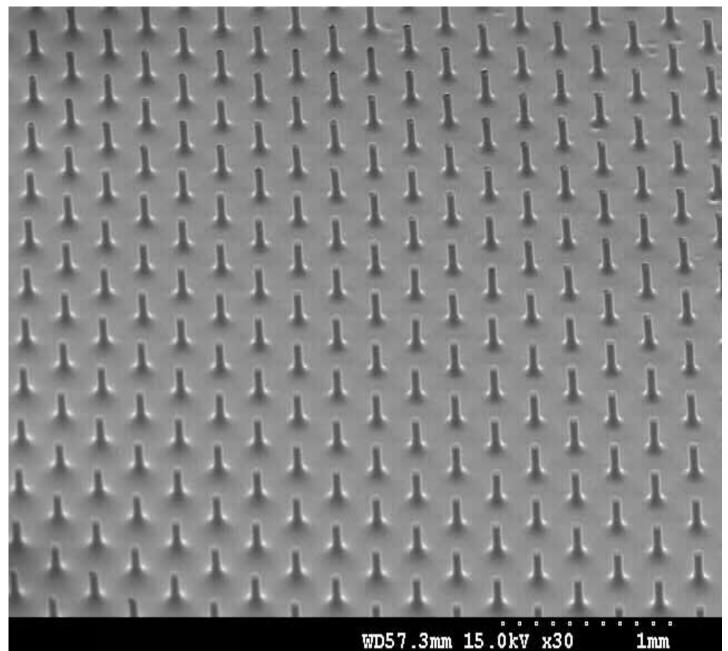

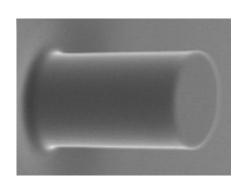

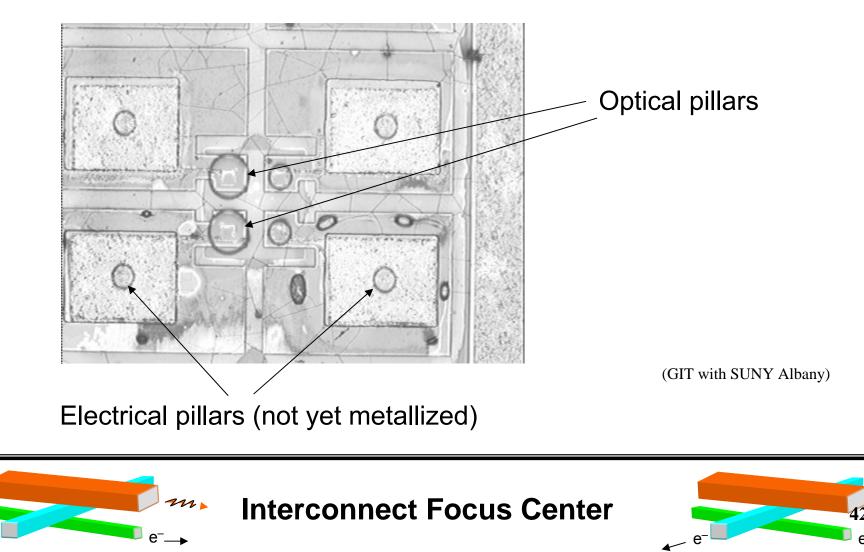

**Second Generation** Sea of Leads:Compliant Polymer Pillars for Compatible <u>Optical & Electrical</u> I/O Interconnects

50 µm x 150 µm tall photo-defined pillars using **Avatrel** (Promerus LLC and GT projects )

(Courtesy of Dr. M. Bakir)

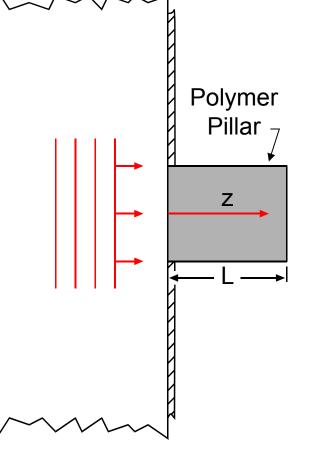

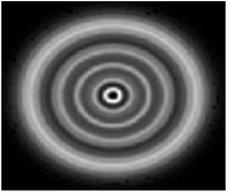

#### POLYMER PILLARS AS COMPLIANT HIGH-QUALITY PRECISION OPTICAL WAVEGUIDES

Polymer Pillar

(Courtesy Prof. T. Gaylord)

Calculated

Measured

**Interconnect Focus Center**

Analysis and measurement of optical transmission of polymer pillar.

## **Diffraction Gratings on Top of Compliant Pillars**

Integration of (GIT) optical pillars with optical detectors (GIT & Stanford) & emitters (GIT &UA,NY)

### **Integration of Compliant Polymer I/O with Photodetectors**

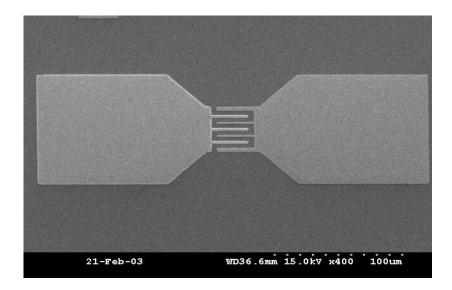

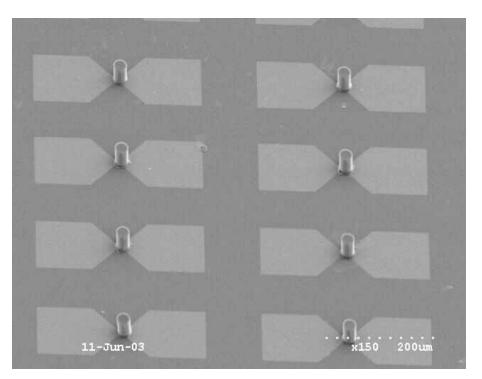

#### **MSM** photodetectors

(GIT & Stanford)

Polymer pins on photodectectors

#### **Dual Function Electrical/Optical Compliant Polymer Pillar I/O**

<sup>(</sup>Courtesy of Dr. M. Bakir)

#### **Dual Function Compliant Polymer Pillars**

Dual-mode polymer pillar: optically transparent tip

(Courtesy of Prof. Ken Goodson)

| Interconnect Focus Center                                            |                                                                      |                                                                                  |

|----------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Program Matrix                                                       |                                                                      |                                                                                  |

|                                                                      | Driver 1<br>High Performance Network Chip<br><i>Krishna Saraswat</i> | Driver 2<br>Low-Energy Mixed Signal Wireless Node<br><i>Anantha Chandrakasan</i> |

| Task 1<br>Electrical Interconnects<br><i>Alain Kaloyeros</i>         |                                                                      |                                                                                  |

| Task 2<br>Optical Interconnects<br><i>David Miller</i>               |                                                                      |                                                                                  |

| Task 3<br>Thermal Management &<br>Power Delivery<br><i>Paul Kohl</i> |                                                                      |                                                                                  |

| Task 4<br>Circuit & System Design &<br>Modeling<br>Duane Boning      |                                                                      |                                                                                  |

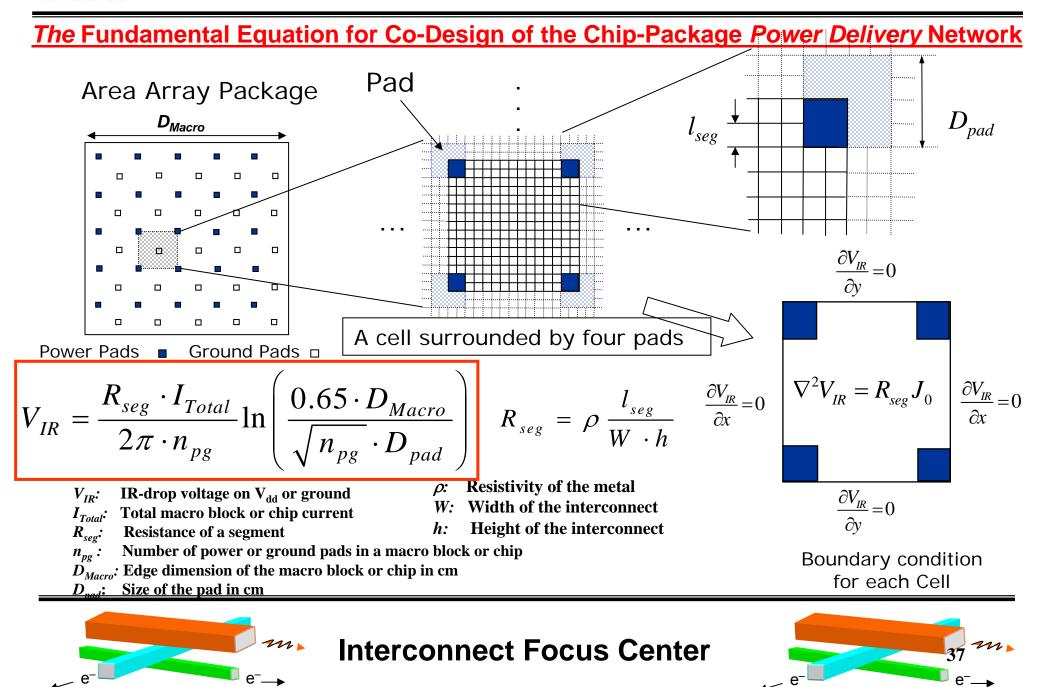

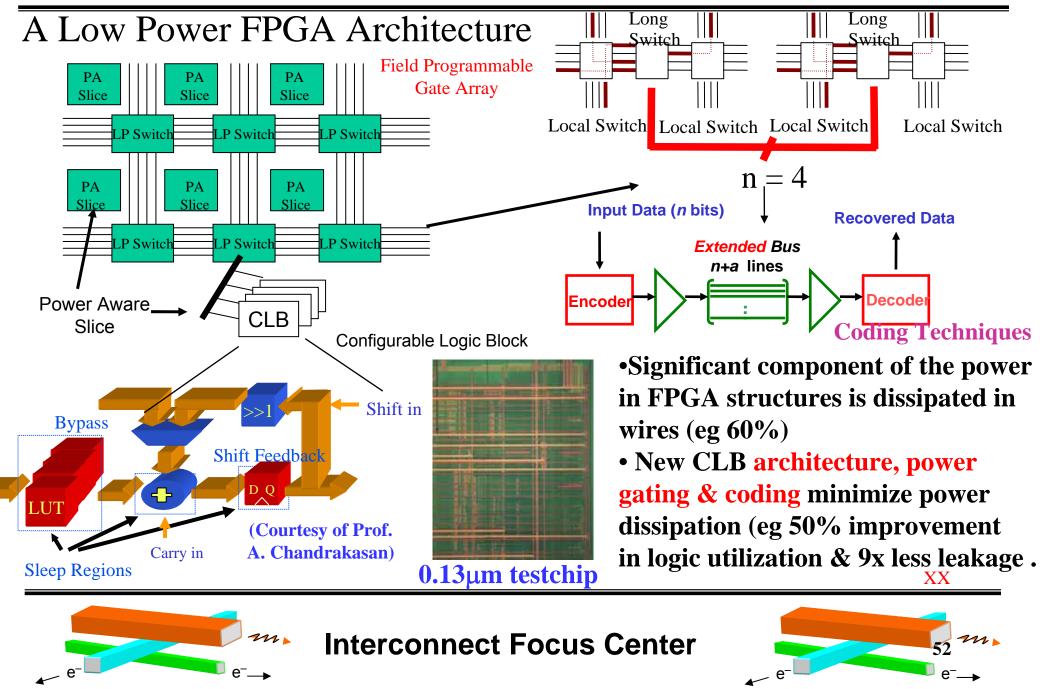

## Key Objectives: Novel Circuits, Systems & CAD Tools

Electrical

#### Signalling

- Extended Electrical Signalling

- Clock-Data Recovery

- Substrate Noise Estimation

- RLCM Impulse Response Extraction

- E-M Analysis of Rough Surfaces

#### Clocking

Standing Wave Clock

#### Power

- Energy in FPGAs

- Power Delivery in Stacked Logic

#### Signalling

- TIA-less Optical Receiver

- 3D E-M Reduced Order Models

- Sensitivity Analysis in Photonic Devices

**Optoelectronic**

- Variation in Optical Splitters

- Simulation of Mode-Locked Laser Dynamics

- Modeling Photonic Crystals

- 3D Maxwell Solution for Optical IR

#### Clocking

PLL-Based Active Optical Clock

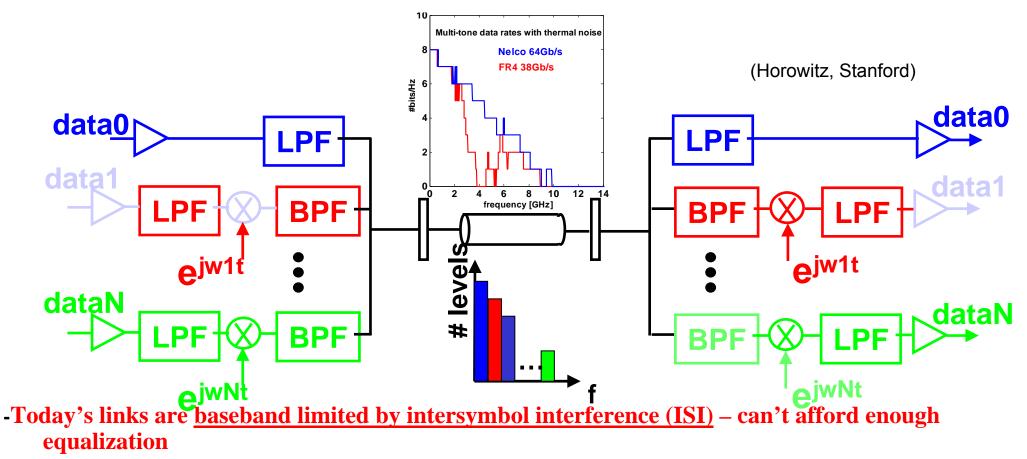

## Extend Electrical Signaling

-Extend performance by multi-tone transmission but must be simple: can't afford discrete multitone (DMT) circuits – explore analog methods

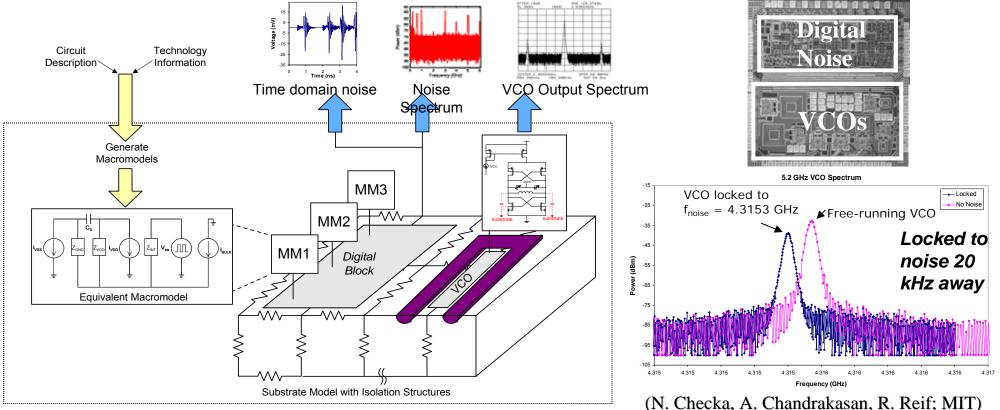

# Substrate Noise Estimation Framework

- Testchip fabricated and tested to study the impact of substrate coupling

- Framework: Demonstrated < 5% error with Spice for key benchmark circuits

- Framework expected to be released in 2005

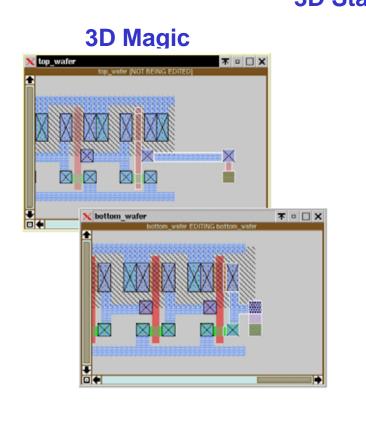

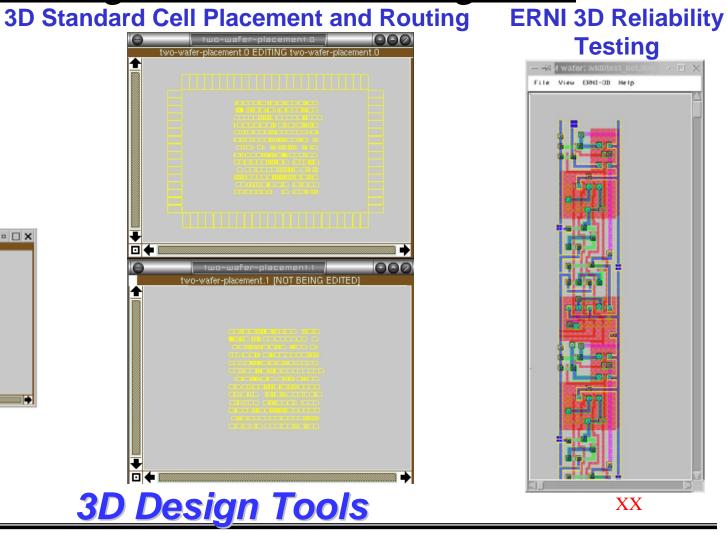

## **Physical Design Tools for 3D Integration**

(A. Chandrakasan & R. Reif; MIT)

#### **Interconnect Focus Center**

XX

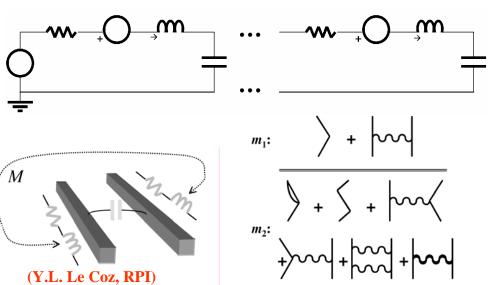

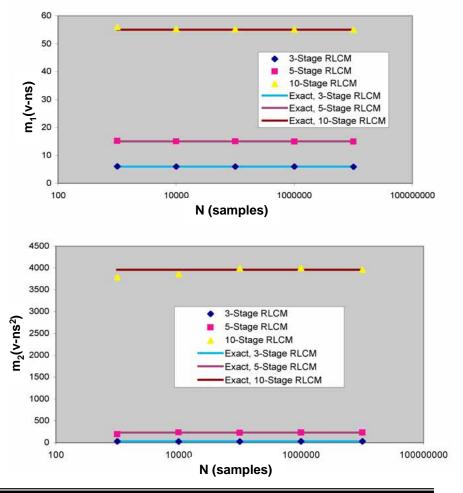

#### **Electrical & Optical Interconnect Impulse-Response Simulator** *Challenge*—create efficient stochastic (random-walk/Monte

- Challenge—create efficient stochastic (random-walk/Mont Carlo) algorithms for IC-interconnect impulse-response (IR) simulation.

- *Results*—created and validated a new algorithm for electrical IR extraction of uncoupled & coupled *RLCM* lines; created a new algorithm for optical IR extraction.

- *Future Work*—analyze *RLCM* bus lines with 1G mutualinductance couplings; test the optical IR-extraction algorithm.

RX

RX

RX

PLL

TX

TX

ТХ

RX

RX

RX

PLL

ТΧ

ТΧ

VCSELs

RX

RX

RX

PLL

TX

TX

TX

...

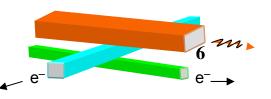

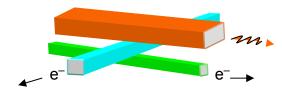

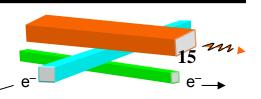

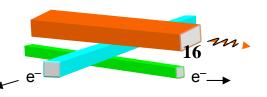

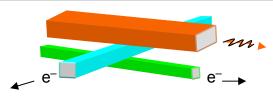

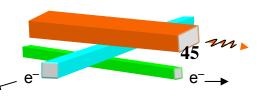

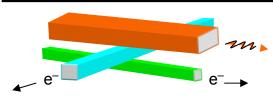

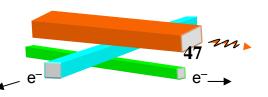

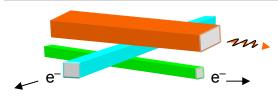

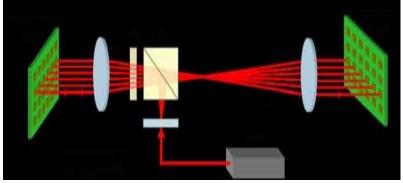

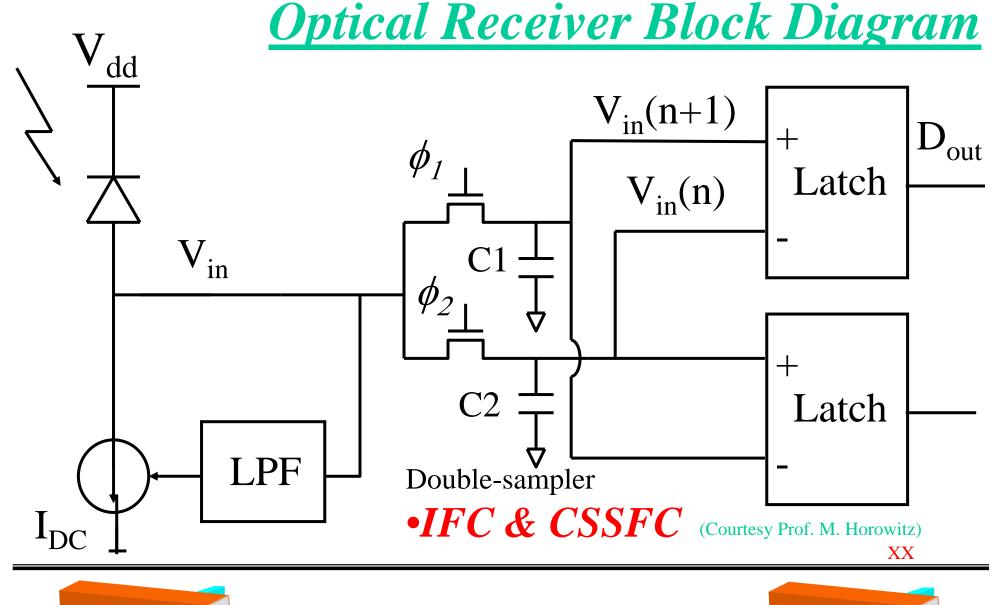

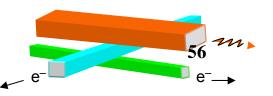

# Parallel Optical Interconnect

Transmitter chip

laser Receiver chip

- Optical transceiver in CMOS

- 5 G/b in 0.25µ technology

- Used flip-chip MQW diodes

- In 90nm, > 15Gb/s, < 30mW

- Uses novel receiver architecture

- No TIA in forward path

- Integrating receiver

(M.Horowitz)

e

SEMICONDUCTOR SUPPLIERS

\_ e⁻

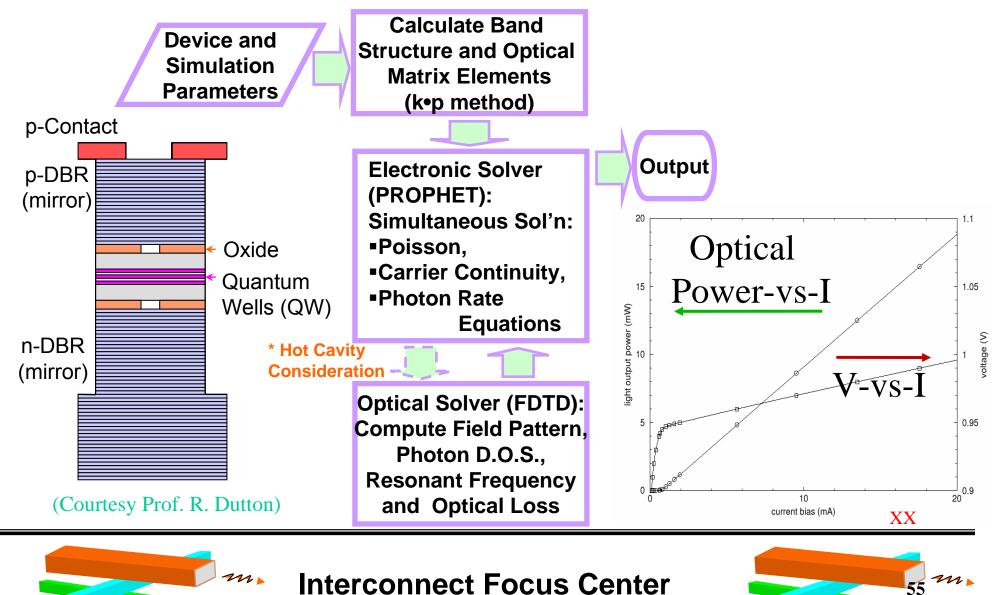

#### **PROPHET: Optoelectronic Simulation of OE/QW Structures**

## **Conclusion--Overarching Challenge of Interconnect Era:**

To Provide a Hierarchy of <u>Electrical, Optical & Thermofluidic</u> Interconnect Solutions

- 5. System: Innovative interconnect-centric system architectures that <u>"keep interconnects short"</u>

- 4. Circuit: Original circuit concepts & physical design tools (eg "amplifier-less" optical receivers & 3D design tools)

- 3. Device: Novel optoelectronic device & interconnect structures (eg mode-locked VSCELs & batch-fabricated polymer optical I/O pins)

- 2. Material: New materials and processes (eg carbon nanotubes and molecular wires)

- 1. Fundamental: Previously untapped fundamental principles(eg on-chip photonics)

# THANK YOU