# A Custom Integrated Circuit Comparator for High-Performance Sampling Applications

Owen B. Laug, Member, IEEE, T. Michael Souders, Senior Member, IEEE, and Donald R. Flach, Member, IEEE

Abstract—This paper reports on the design and performance of an application-specific integrated circuit (ASIC) comparator that has been optimized for equivalent-time waveform sampling applications. The comparator, which has been fabricated with an 8.5 GHz  $f_{T}$ , bipolar silicon process, features a bandwidth of >2 GHz, a settling-time accuracy of 0.1% in 2 ns, and almost total elimination of "thermal tails" in the settling response. Several novel design features that have been used to achieve this level of performance are presented. The comparator can be used in a sampling system for both frequency-domain measurements, e.g., wideband rms voltage measurements, and high-accuracy time-domain pulse measurements.

#### I. Introduction

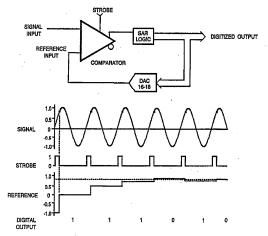

RESEARCH at NIST (National Institute of Standards and Technology) and several other laboratories has demonstrated that very high-performance equivalent-time sampling of repetitive waveforms can be achieved with a high-speed, latching analog comparator used as a sampling device in a technique generally referred to as a Sampling Comparator System (SCS) [1], [2], [3]. Similar to digital sampling oscilloscopes, an SCS can be configured in an elegantly simple circuit referred to as an equivalent-time successive approximation A/D converter as shown in Fig. 1.

Since the configuration in Fig. 1 was used as a test bed to evaluate the comparator it will be instructive to review briefly the operation of the circuit. The A/D conversion is implemented in equivalent time by means of a comparator that provides the sampling function as well as the decision function. As illustrated, the strobed comparator is operated in a feedback loop to sample repetitively the input signal at a given instant on the waveform. The comparator compares the reference voltage applied to one input with the instantaneous value of the input waveform at the time the comparator is strobed. Based on the output state of the comparator, the successive approximation register (SAR) instructs the digital-to-analog converter (DAC) to increment or decrement the level applied to the reference input of the comparator in preparation for the next comparison. The process is repeated until the reference level equals the sampled level of the waveform to the desired degree of precision. Then, the strobe position

Manuscript received May 14, 1992; revised August 20, 1992.

The authors are with the National Institute of Standards and Technology, Gaithersburg, MD 20899.

IEEE Log Number 9205054.

Fig. 1. A sampling comparator system using the successive approximation search routine for controlling the reference input voltage to the comparator.

is moved to another point on the waveform, and the search routine is repeated. This sampling process is continued until a desired record of samples has been obtained. Any arbitrary, repetitive waveform can be measured with the SCS; however, one of the main virtues of the SCS is its exceptional accuracy in the measurement of step-like waveforms. In particular, we are interested in the ability of the SCS to track accurately and settle on the fast transition edge of such waveforms.

At least one manufacturer markets a general-purpose waveform analyzer based on the SCS approach just described. This instrument is configured such that the comparator is housed separately in a small probe connected by an umbilical cable to a mainframe containing the rest of the system. This arrangement permits the sampler to he connected directly to the output of the source of voltage to be measured, eliminating the need for connection cables and the encumbrance of the supporting hardware. The instrument provides a reference voltage with a resolution of 16 b and an equivalent-time resolution of 10 ps in addition to other features that make waveform measurement and processing very easy. We have used this commercial instrument with our own probe circuit as a means of evaluating and reporting the performance of our custom ASIC comparator.

#### II. COMPARATOR DESIGN CONSIDERATIONS

The impressive performance of SCS's in current use has been achieved with inexpensive, commercially available IC comparators, but the performance of the system is almost entirely determined by the comparator. Because the comparators that are generally available for this purpose have not been optimized for this application, there is a potential for significant improvement in performance by developing a comparator specifically designed for SCS's. Initially, GaAs technology was investigated for a custom comparator because of the inherent high-speed characteristics and high input impedance. However, the high-speed characteristic is offset by a number of persistent problems such as backgating and channel conductance dispersion which limit the usefulness in precision analog applications [4]. Silicon devices, although not as fast as GaAs devices, can still provide competitive speeds. A high-performance silicon wafer process with bipolar devices having a typical  $f_T - 8.5$  GHz was selected for our ASIC comparator. The manufacturer offers these highspeed bipolar transistors configured in uncommitted arrays together with resistors, capacitors, JFET's, and Schottky diodes. The devices are contained on a 1.45 mm by 1.45 mm substrate allowing for the economical integration of small, very high-performance circuits. Before the design was committed to fabrication, extensive simulations of the design were performed with models provided by the integrated circuit foundry.

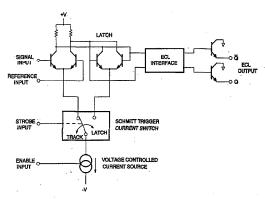

The conflicting requirement for a comparator of both high gain and wide bandwidth can be realized by relying on the regenerative amplification of a latch stage while minimizing the amount of preamplification. Fig. 2 shows a simplified diagram of the custom comparator to illustrate this concept. The first stage is a low-gain differential amplifier that compares the input signal with the reference level and amplifies the difference. The second stage is a master latch that samples the amplified signal from the first stage. When the latch stage is activated (i.e., the current source is switched from tracking to latching), the positive feedback will amplify any small difference from the first stage. The regenerative growth of the initial difference voltage will finally be limited by the current available to the latch so that one device becomes fully on and the other completely off, resulting in a latching of the stage. Thus, the latch stage serves two important functions: regenerative amplification and latching or holding the state of comparison at the sampling moment. Minimizing the gain of the first stage not only improves the bandwidth but lessens the overload recovery time and attendant signal amplitude dependent delay. Any dispersion in the delay of the first stage will cause harmonic distortion. Actually, in this application the first stage can be considered more as a high-speed differential gate rather than an amplifier. The trade-off for this approach is replacement of the equivalent comparator gain by a finite delay time during which small difference signals must regenerate exponentially to higher voltage levels in the latch

Fig. 2. Simplified block diagram of the custom integrated circuit comparator.

stage. An approximation of the time-gain relationship [5], [6] is given by

$$t = \tau \log (A) \tag{1}$$

where A is the equivalent gain of the latch stage defined as the ratio of the latched differential output voltage to the differential input voltage at the sampling moment, and  $\tau$ is the regeneration time constant of the stage. The value of  $\tau$  was determined from simulation to be about 130 ps. For example, a latched differential output voltage of 0.4 V and a 100  $\mu$ V differential input voltage at the sampling moment (a gain of 4000) will require over 650 ps for the latch output voltage to reach 0.4 V. However, the total regeneration time is not an issue in equivalent-time sampling because of the relatively long time between samples. In the early regenerative phase of the latch stage, however, the amount of hysteresis is small so that the stage is sensitive to disturbances such as noise or amplifier "blow by" which may have sufficient energy actually to reverse the polarity of initial exponential growth causing both random and systematic errors. "Blow by" is referred to here as the effect of the signal coupling through the first stage after it has been deactivated. From the standpoint of reducing errors, it is desirable to design the latch stage for the minimum regeneration time constant,  $\tau$ , so that the stage latches as fast as possible.

The speed at which the transition is made from track to latch is important for high slew-rate signals. This transition time defines the effective sampling aperture which not only determines the equivalent bandwidth of the comparator, but also influences the harmonic distortion produced from a sampled waveform [7]. To take advantage of the inherent fast regeneration time constant of the latch stage and make it less dependent on the strobe source transition time, a Schmidt trigger current switch was designed on the chip as part of the comparator. Simulation studies of the Schmitt trigger current switch indicate about a 75 ps (10-90%) transition time for the current to switch to the emitters of the latch stage.

A common observation when step-like waveforms are

being sampled with commercial comparators is that significant settling-time errors persist for several hundred nanoseconds. These errors amount o a few millivolts and may require up to one microsecond to completely settle out. This phenomenon is often referred to as a "thermal tail" error, which is a nonlinear process that manifests itself in the time domain but also can cause significant signal level dependent errors in the frequency domain. The problem arises because the transistors of the input differential pair conduct unequally, except when the input and reference signals are equal. Since the input signals to the comparator are dynamic and usually unequal except at the sampling instant, the difference can be large enough to turn one transistor fully on while the other is turned completely off. This state will unbalance the power dissipation and attendant heating of each transistor from the equal input condition. Because of imperfect thermal coupling between the two transistors, the transistor base-emitter junctions will be at different temperatures. Consequently, the base-to-emitter voltages of the differential pair will differ and will not track with time until many thermal time constants have elapsed. This leads to an offset error as a function of time between the reference voltage and the input voltage which manifests itself as a settling-time error. Convincing evidence of this effect can be observed from the variability of the settling time that occurs when the duty factor of the signal is changed.

### A. Enabling Technique

A new hardware-design approach for eliminating the thermal errors and other errors due to long response time anomalies has been incorporated in the custom comparator. The approach is based on an enabling technique that activates the differential devices within the comparator for only a short interval before being strobed. Refer again to Fig. 2 which shows a voltage-controlled current source that can be turned on by an enable input signal. The idea here is to keep the emitter current to the differential pair off most of the time and to energize the stage just before a comparison is required. Keeping the input stage off most of the time, and then enabling for a short period, minimizes the power dissipated in the transistors and the resulting temperature differences. In this way the differential amplifier is "on" for a period only long enough to track the difference between the signal and the reference voltage. After the current source has been turned on for a period, the strobe signal switches the current source from the first stage to the latch stage. The lead time between the enable and strobe is set at about 2 ns, which was shown by simulation and practice to be sufficient for the stage to track a difference accurately before strobing. In our application, the comparator is strobed at about a 30 kHz rate, which amounts to a very low thermal dissipation duty factor for the first stage.

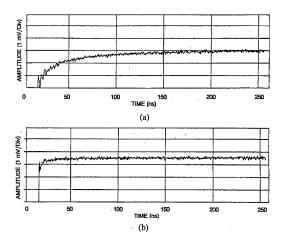

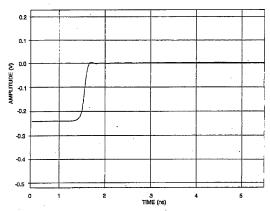

The effectiveness of the enabling technique in improving the settling-time response of our custom comparator used in the SCS system is shown in Fig. 3. In Fig. 3(a)

Fig. 3. (a) Settling-time response of the sampling comparator system with the enabling system of the comparator deactivated so that the current source of Fig. 2 remains continuously on. (b) The much improved settling-time response by enabling the comparator 2 ns before strobing.

the enabling function was deactivated so that the voltage-controlled current source of Fig. 2 remained continuously on. Note that over 200 ns are required to settle to the final DC value. Fig. 3(b) shows the rather dramatic improvement in settling time when the enabling technique is activated. The enabling system can have a similar profound influence in improving the flatness of the overall frequency response, at frequencies corresponding to the thermal time constants of the input stage.

The enabling technique not only reduces thermal errors but can reduce any "low frequency" aberration (thermal or electrical) in the transfer function of the comparator. The presence of undesirable electrical time constants (a linear system phenomenon) within the comparator also can add tails to the settling performance. In either case, the problem is that the comparator's response time is too long. The enabling procedure for eliminating "thermal tails" also applies to these impulse response tails. In effect, the time difference,  $t_d$ , between the activation of the current source and the leading edge of the strobe, defines the effective response time of the comparator. Any tails in the impulse response of the comparator that extend beyond this duration will effectively be truncated. In the frequency domain, the frequency response of the comparator will be the Fourier transform of the truncated impulse response. The truncation will be manifested as a tendency to flatten the frequency response or transfer function for frequencies less than  $1/t_d$ . There is a practical limit, however, to reducing  $t_d$  to the point where short impulse tails cannot be truncated without causing other more serious response distortions.

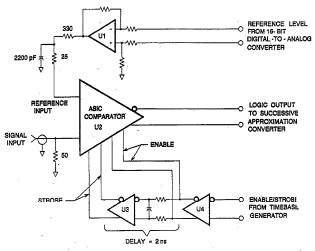

## B. Sampling Comparator Probe

Fig. 4 shows a simplified schematic of the probe circuit developed to evaluate the custom comparator. The comparator and associated devices and components are

Fig. 4. Simplified schematic diagram of the probe circuit for evaluating the custom comparator in a sampling comparator system.

mounted on a multilayer board inside a palm-size metal case. The custom comparator chip is physically mounted within 2 mm of a type SMA input connector and 50-Ω termination. The direct mounting of the chip on the board and its close proximity to the input eliminate the parasitics contributed by the package lead frame and minimize the bond-wire inductance. The quasi-static reference level from the A/D converter is buffered by a low-noise amplifier U1, the output of which is connected to the reference input of the comparator through a low-pass filter and 25 Ω of resistance. When using this comparator, it is important for the high-frequency source resistances of each input to be nearly equal to obtain the fastest settling time of the first stage. A pair of ECL line drivers/receivers (U3 and U4), together with an RC network, provide the appropriate delay between the enable and strobe command to the comparator.

## III. PERFORMANCE RESULTS

The performance of the comparator was evaluated in the previously described probe circuit in conjunction with a commercial instrument that provides all of the necessary signals, display, and waveform processing. A preliminary summary of the salient features and characteristics of the comparator is listed below.

| Transition Duration: (10-90%)      | 150 ps     |

|------------------------------------|------------|

| Bandwidth: (from TD using 0.35/TD) | ) 2.3 GHz  |

| Settling Time:                     |            |

| (referred to final DC value)       |            |

| to 0.1%                            | 2 ns       |

| to 0.02%                           | 10 ns      |

| Slew-rate limit: (above ±1 V)      | 5 V/ns     |

| Input range:                       | ±2.0 V     |

| Maximum differential input:        | ±4.0 V     |

| Noise: (referred to the input)     | 425 μV RMS |

Transition duration (TD) was measured by determining the time between the 10% and 90% amplitude points of the recorded response to a -0.25 V to 0 V, 16 ps TD step-like signal. Fig. 5 shows a plot of the sampled waveform from which the transition duration was determined. The TD, however, is sensitive to amplitude. When the step amplitude is attenuated to 0.125 V the TD increases to 190 ps and approaches a maximum of 280 ps at input levels down to about 5 mV indicating that the bandwidth is amplitude sensitive. This corresponding reduction of bandwidth with amplitude, i.e., the small-signal bandwidth is less than the large-signal bandwidth, is opposite from what is normally experienced with amplifiers. The same effect has been observed in all commercial strobed comparators we have tested, but to a much larger degree. This phenomenon is not well understood and needs to be addressed in future designs.

The measurement of fast settling-time performance to high accuracy is difficult because of the uncertain characteristics of a reference waveform. Most high-quality step-like reference waveforms are designed to settle accurately to zero volts from a positive or negative voltage level, and their performance is inferred from modeling and measurements [8]. The settling-time values reported above were confirmed using reference step generators from three different manufacturers, thus affording a greater confidence in the measurement. The very fast generator (0.25 V, 16 ps) used for measuring the TD was also utilized in making the settling-time measurements. Two other slower generators were also used: one with a TD of 400 ps and a +0.5 V to 0 V negative-going transition and the other having a 240 ps TD that can operate with transitions from either +0.5 to 0 V or -0.5 to 0 V. These three generators all produced similar settling-time results as reported above. Settling time was determined by increasing the vertical sensitivity and noting the time (from

Fig. 5. Response to a 0.25 V, 16 ps input step generator.

the midpoint of the transition) required to settle to and remain within a given tolerance band. The measurement of settling-time accuracies in the 100 ppm range requires an appropriate amount of record averaging to reduce the noise produced by the comparator.

A few words are in order about the apparent slew-rate limitation of the comparator. We have observed that input steps above  $\pm 1$  V with slew rates above 5 V/ns cause a loss of control which manifests itself by a baseline shift and one or more discontinuities in the fast transition portion of the waveform. The cause of this breakdown in function is under investigation.

The RF voltage measurement capability of the system was investigated over a frequency range from 1.0 kHz to 100 MHz. Measurements were compared against an NIST-calibrated thermal voltage converter (TVC), the standard with which rms voltage is determined [9]. Special care must be taken in such comparisons to account for the skin-effect and transmission-line errors in the input connector [10]. To reduce the skin-effect problem contributed by connectors, a special NIST-designed tee apparatus was used. This apparatus is designed to reference the measurement plane to the center of a coaxial type N tee.

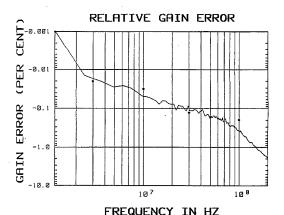

The small errors in the SCS's response over the frequency range of interest can be independently estimated from step response measurements using a fast TD, fastsettling step-like reference waveform of the same type used to measure settling time. The method is described in detail in [11]. The step is sampled with an equivalent-time sampling rate sufficient to give negligible aliasing errors over the frequency range of interest. The discrete impulse response is then computed from the step response data, and the frequency magnitude spectrum is obtained by Fourier transform of the impulse response. Then, gain corrections can be computed from the magnitude spectrum. Fig. 6 shows the results from such a measurement which gives the gain error relative to the first spectral line at 1 MHz. Also included in the figure, shown as solidcircles, are the comparison measurements using the SCS

Fig. 6. Gain error of the SCS relative to the value at 1 MHz. Line: Determined from step response data. Solid circles: Determined from sine wave measurements using a calibrated TVC.

TABLE I MEASURED ERRORS (TVC-SCS)

| Frequency<br>(MHz) | Error<br>(%) |

|--------------------|--------------|

|                    |              |

| 0.01               | 0.003        |

| 0.1                | 0.000        |

| 1.0                | -0.006       |

| 3.0                | -0.009       |

| 10.0               | 0.013        |

| 30.0               | -0.024       |

| 50.0               | 0.002        |

| 100.0              | 0.194        |

and a calibrated TVC at 1 V rms. These points represent the SCS gain error determined from the frequency-domain measurements described above using a calibrated TVC.

A more complete set of measurement results is listed in Table I. Here, the errors listed are the differences in percent between the voltages measured by the TVC and the SCS. For these results, SCS gain error corrections have been applied from the impulse response relative to the spectral line at 0.05 MHz rather than the 1.0 MHz of Fig.

## IV. Conclusions

A custom integrated circuit comparator fabricated for high-performance sampling applications has been described. The comparator can be used in a sampling system for both frequency-domain measurements, e.g., wideband rms voltage measurements, and high-accuracy timedomain pulse waveform measurements. The results of measurements of settling-time accuracy indicate that the comparator is capable of state-of-the-art time-domain measurements. In the frequency domain the RF measurement capability is comparable to the best achievable using TVC's.

Improvements in the comparator design have elimi-

nated the influence of thermal errors common in other comparators. Removing the effect of thermal errors not only improves the settling-time accuracy but also reduces the RF gain error particularly at low levels. Elimination of thermal tail errors in the comparator coupled with its wide bandwidth provides an unsurpassed combination of speed and accuracy when used in equivalent-time sampling applications.

#### ACKNOWLEDGMENT

The authors wish to thank Robert Palm for his valuable contribution in the fabrication and assembly of the sampling comparator probe. Also, special thanks to John Brewer, Scott Williams, and Walt Ainsworth of Tektronix whose suggestions were most helpful in assuring a first-time success in the fabrication of our custom ASIC comparator.

#### REFERENCES

J. Halbert and M. Koen, "A waveform digitizer for dynamic testing of high speed data conversion components," Proceedings 1983 Inter-national Test Conference (Philadelphia), IEEE Computer Society

- [2] T. M. Souders et al., "Characterization of a sampling voltage tracker for measuring fast, repetitive signals," IEEE Trans. Instrum. Meas., vol. IM-36, Dec. 1987.

[3] C. Gyles, "Repetitive waveform high frequency, high precision dig-

- itizer," *IEEE Trans. Instrum. Meas.*, vol. 38, Aug. 1989.

[4] L. E. Larson, C. Chou, and M. J. Delaney, "An ultrahigh-speed

- GaAs MESFET operational amplifier," IEEE Solid-State Circuits,

- vol. 24, pp. 1523-1527, Dec. 1989.

[5] P. J. Lim and B. A. Wooley, "An 8-bit 200 MHz BiCMOS Comparator," *IEEE J. Solid-State Circuits*, vol. 25, pp. 192-199, Feb.

- [6] B. Zojer, R. Petschacher, and W. A. Luschnig, "A 6-bit/200-MHz full nyquist A/D converter," *IEEE Solid-State Circuits*, vol. SC-20, pp. 780-786, June 1985.

- B. Peetz, B. D. Hamilton, and J. Kang, "An 8-bit 250 megasample per second analog-to-digital converter, operation without a sample and hold," *IEEE J. Solid-State Circuits*, vol. SC-21, pp. 997-1002,

- [8] J. R. Andrews, B. A. Bell, N. S. Nahman, and E. E. Baldwin, "Reference waveform flat pulse generator," *IEEE Trans. Instrum. Meas.*, vol. IM-32, pp. 27-32, March 1983.

[9] J. R. Kinard and C. Ti-Xiong, "Determination of ac-dc difference in

- the 0.1-100 MHz frequency range," IEEE Trans. Instrum. Meas., vol. 38, pp. 360-367, April 1989. [10] D.-X. Huang, J. R. Kinard, and G. Rubuldela, "RF-DC differences

- of thermal voltage converters arising from input connectors," *IEEE Trans. Instrum. Meas.*, vol. 40, pp. 360-365, April 1991.

[11] T. M. Souders and P. S. Hetrick, "Accurate RF voltage measurements using a sampling voltage tracker," *IEEE Trans. Instrum. Meas.*, vol. 38, pp. 451-456, April 1989.