Semiconductor Technology Research, Development, & Manufacturing: Status, Challenges, & Solutions

C. R. Helms\* Past President & CEO International SEMATECH

\*Professor Emeritus, Stanford Univ.

Semiconductor Technology Research, Development, & Manufacturing: Status, Challenges, & Solutions

**A New Paradigm in the Making?**

C. R. Helms\* Past President & CEO International SEMATECH

\*Professor Emeritus, Stanford Univ.

# Agenda

Semiconductor Revenue Growth: Yes!

Realize Which Roadmap?

**Technology Challenges**

R&D Cost

# Agenda

- Semiconductor Revenue Growth: Yes!

- Historical Perspective & Extrapolation

- Realize Which Roadmap?

- End Equipment & Product

- Cost per Function

#### **Technology Challenges**

- Mask Availability, Cost, Cycletime

- Post 193nm Exposure Technology

- New Materials

#### R&D Cost

- How Many Si Tech R&D Centers Can the Industry Support?

- R&D Foundries, Partnerships, & Alliances Win!

international SEMATECH

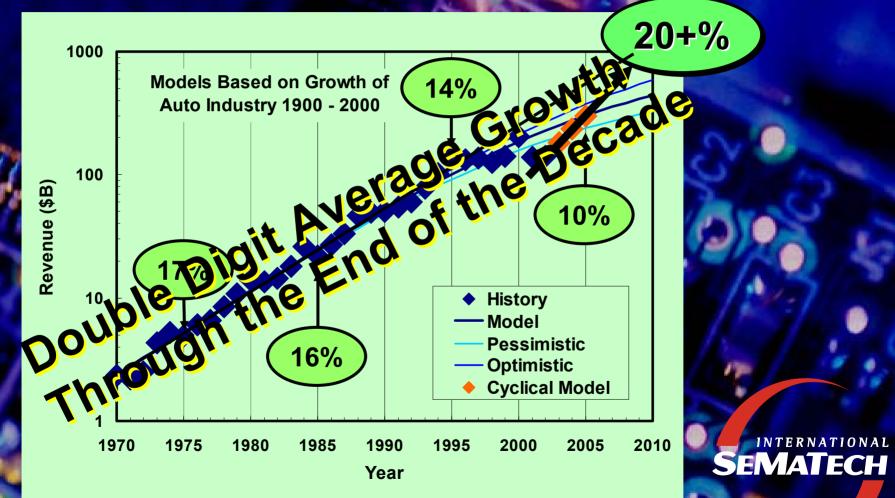

#### Semiconductor Industry Revenue Growth Summary

- 17% CAGR in the 70's and 80's

- Drove High Rates of Capital Investment and R&D

- In Turn Drove Better Penetration of Existing Markets and the Opening of New Ones

- In Turn Drove Revenue Growth

- This is a Cyclical Growth Industry with a 5-Year Period

Maturation is Occurring

– But not that Fast!

### **Projections from a Historical Study of Industry Growth Trends**

# Agenda

- Semiconductor Revenue Growth: Yes!

Historical Perspective & Extrapolation

- Realize Which Roadmap?

End Equipment & Product

Cost per Function

#### **Technology Challenges**

- Mask Availability, Cost, Cycletime

- Post 193nm Exposure Technology

- New Materials

#### R&D Cost

- How Many Si Tech R&D Centers Can the Industry Support?

- R&D Foundries, Partnerships, & Alliances Win!

# **Roadmap Hierarchy**

End Equipment (PCs, DVDs, Hand-helds, Wireless)

Products (µPU, DRAM, DSP, Baseband)

#### Modules (Logic, Memory, Analog)

Specifications (V<sub>DD</sub>, Freq., Pwr., Cost, Lifetime)

**Requirements**

RS

Layout/Architecture (Random, Gate Array, Logic-Based, Memory-Based)

Materials/ Structures (Cu, Low K, SOI, ½ Pitch) Processes/Tools

(193nm, CMP ) Solutions

Too Much Focus on the Lower Level "REQUIREMENTS" can Drive Unprofitable Investments, i.e.

Low K Interconnects

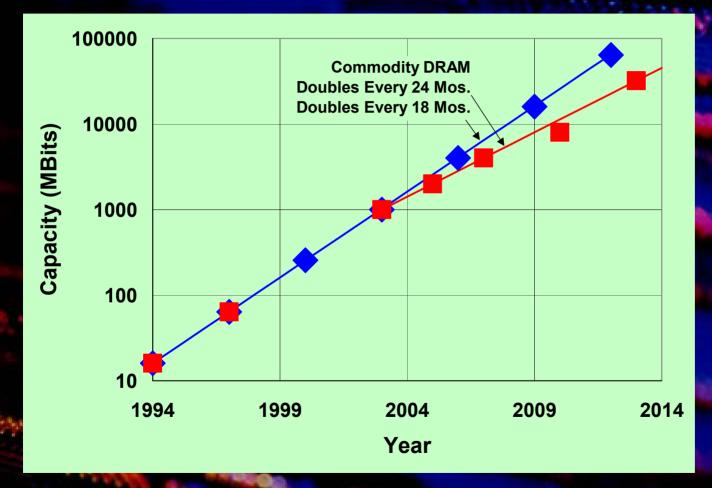

### Commodity DRAM Product Roadmap

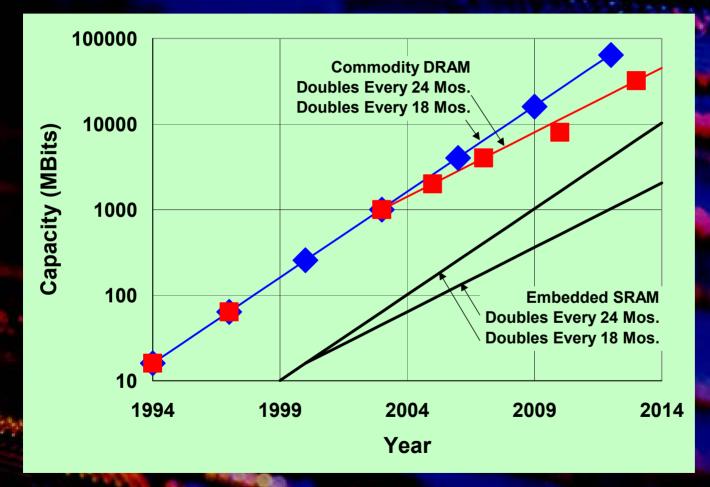

# Commodity DRAM & Embedded SRAM Product Roadmap

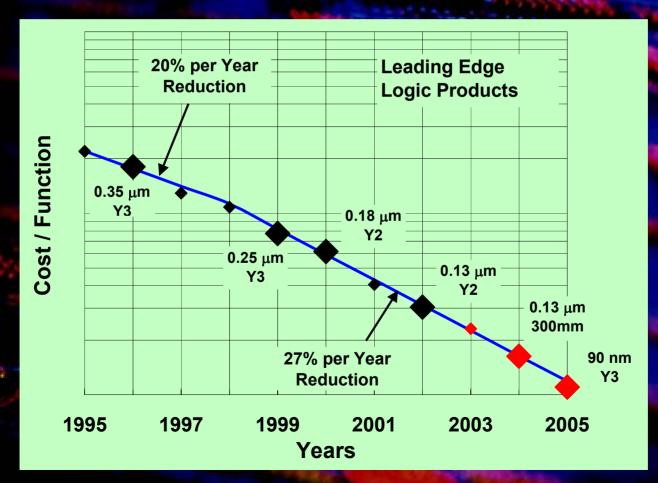

### Manufacturing Cost per Function Roadmaps

Driven by Transistors per Area and Cost per Area

2-Year Cycle 3-Year Cycle

40%

8%

4%

27%

25%

4%

4%

Annual Transistor per Unit Area Increase

Average Cost per Unit Area Increase – Constant Wafer Size

Average Cost Reduction for Wafer Size Conversion Every 10 Years

Predicted Annual Cost per Function Decrease

**2-Year Cycle Wins!**

# Validated ISMT Cost per Function Model Slope Change in 1998 due to 2-Year Cycle 300mm Cross-Over Predicted in 2004

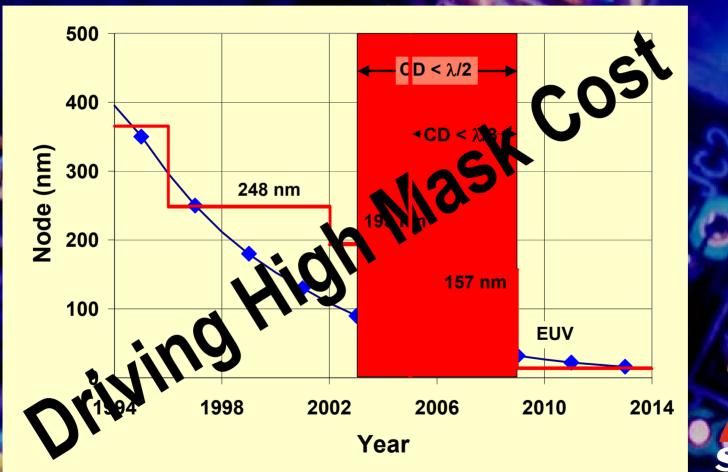

### Major Technology Challenge: The Sub – 1/2 Wavelength Red Zone

# Agenda

- Semiconductor Revenue Growth: Yes!

- Historical Perspective & Extrapolation

- Realize Which Roadmap?

- End Equipment & Product

Cost per Function

- **Technology Challenges**

- Mask Availability, Cost, Cycletime

- Post 193nm Exposure Technology

- New Materials

#### R&D Cost

- How Many Si Tech R&D Centers Can the Industry Support?

- R&D Foundries, Partnerships, & Alliances Win!

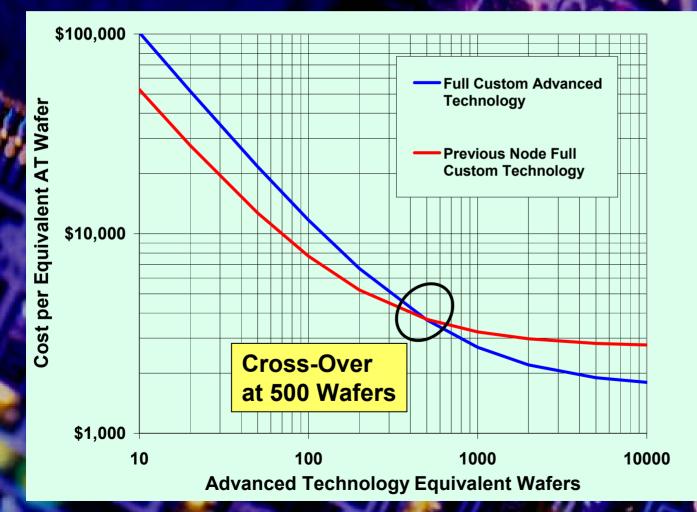

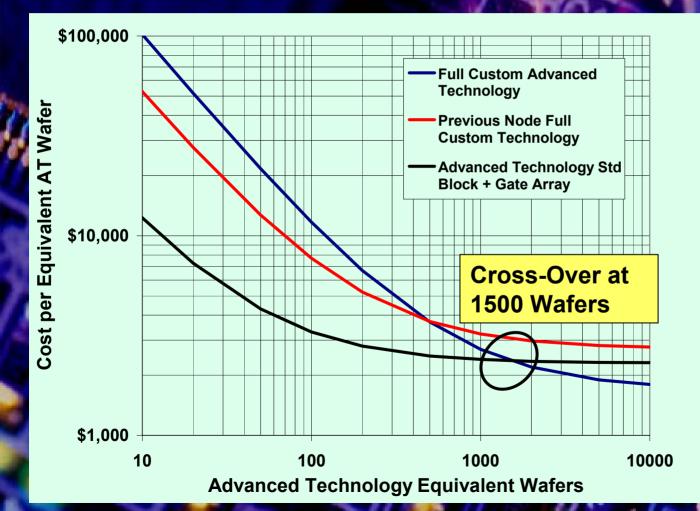

### Mask Issues

- Phase Shift & OPC Requires 2x+ Resolution Improvement

- Infrastructure Development Cost not **Supported by Revenue**

- **Database Size Exploding**

- **Cost Going up 2x per Generation**

- Manufacturing () 130nm \$ 600K

- \$1200K 90nm \$2400K ?

**65nm**

E

# Mask Cost Analysis 130nm to 90nm Only Manufacturing Considered

#### Smart Gate Arrays Become More Attractive

### Summary of Top Technical Challenges

- Mask Availability, Cost, and Cycletime

- Especially for Custom Products

- Post 193nm Litho Exposure Tools – 157nm in Mainstream Production in 2006/2007 – EUV in Mainstream Production in 2009/2010

- New Materials

- Low K's

- High K's

- Memory Materials

### Summary of Top Technical Challenges

- Mask Availability, Cost, and Cycletime

- Especially for Custom Products

- Post 193nm Litho Exposure Tools – 157nm in Mainstream Production in 2006/2007 – EUV in Mainstream Production in 2009/2010

- New Materials

- Low K's

- <mark>High K</mark>'s

- Memory Materials

# Agenda

- Semiconductor Revenue Growth: Yes!

- Historical Perspective & Extrapolation

- Realize Which Roadmap?

- End Equipment & Product

Cost per Function

- Technology Challenges

- Mask Availability, Cost, Cycletime

- Post 193nm Exposure Technology

- New Materials

#### R&D Cost

- How Many Si Tech R&D Centers Can the Industry Support?

- R&D Foundries, Partnerships, & Alliances Win!

#### The New Economy for Microelectronics

- A New Factory (Fab) Runs 130nm Technology with Cu Wiring at 300mm

- At a Capital Cost of \$2B \$4B — Increasing at a Rate of 15% per-Year

- Technology R&D to Support 2-Year Major & 1-Year Minor Product Cycles At a Cost of > \$500M per Year for a Tier 1 Logic Manufacturer

- Increasing at a Rate of > 20% per Year

#### Table Stakes for Independent Semiconductor Manufacturer

- Cap Ex of \$1B per Year or Min. of 20% of Revenues

- Implies Revenues of \$5B/yr

Technology R&D Investment of \$500M per Year

> If Requirement of <5% of Revenues for IDM Implies Revenues of \$10B/yr

### **R&D Partnership Risks & Rewards**

- Rewards

- Faster Speed of Execution

Lower Costs

- Risks

- Sacrifice of IP & Potential Competitive Advantage

- Cultural, Geographic, and NIH Factors can Slow Progress

- Divergence of Interests

# Summary

- Semiconductor Revenue Growth: Yes!

> 10% CAGR Through the Decade

- **Realize Which Roadmap?**

- End Equipment & Product

Cost per Function

#### **Technology Challenges**

- Mask Availability, Cost, Cycletime

- Post 193nm Exposure Technology

- New Materials

#### R&D Cost

Consolidation of Si Tech R&D Centers Required

R&D Foundries, Partnerships, & Alliances Win!

INTERNATIONAL SEMATECH

# Addenda

### **Killer App for the Future?**

- Enabler Products

- Broadband

- 3+G Wireless

- **Voice** Recognition

- No Keyboards

- **BioMedical Electronics**

- Reduced Cost of Health Care

- Enabler Technologies

MEMS (MicroElectroMechanicalSystems)

NanoTechnology NanoElectronics

Biotechnology BioElectronics

Silicon Core CMOS – The Platform of Choice