# **Frontiers in Defect Detection**

FCMN 2013, Gaithersburg, USA March 25-28, 2013

Lothar Pfitzner, Sabrina Anger, Matthias Koitzsch, Ulrich Schoepka, Georg Roeder, Alexander Tobisch, Martin Schellenberger, Markus Pfeffer

Fraunhofer Institute for Integrated Systems and Device Technology (IISB)

Erlangen, Germany

Phone: +49 9131 761-110 Email: lothar.pfitzner@iisb.fraunhofer.de

# Agenda

#### Introduction

- Yield Enhancement & ITRS

- Metrology

- Latest Equipment Developments

- Defect Inspection Tools

- Gi-SAXS

- Vacuum Ultra-Violet (VUV)

- Makyoh Metrology Tool

- Zero-Defect Resizing of Large Crystalline Silicon Wafers with TLS

- 450 mm Developments

- Virtual Metrology (VM)

- Summary and Outlook

# Agenda

#### Introduction

- Yield Enhancement & ITRS

- Metrology

- Latest Equipment Developments

- Defect Inspection Tools

- Gi-SAXS

- Vacuum Ultra-Violet (VUV)

- Makyoh Metrology Tool

- Zero-Defect Resizing of Large Crystalline Silicon Wafers with TLS

- 450 mm Developments

- Virtual Metrology (VM)

- Summary and Outlook

### Introduction

Overall objective: to increase manufacturing yields

- Strong increase in processing complexity requires growing efforts in tackling of the challenges in defect detection and yield control

- Defect detection is more than "looking for particles"!

- All defects leading to lower yield must be identified and controlled.

Metrology is defined by the <u>international Bureau of Web/ths and Measures</u> (BIPM) as "the science of measurement, embracing both <u>experimental</u> and <u>theoretical</u> determinations at any level of <u>uncertainty</u> in any field of science and technology.<sup>42</sup> The <u>andburgy</u> and <u>international vocabulary of metrology</u> (VIM) is maintained by the Joint Committee for Guides in Metrology (JCGM), a group made up of eight international organisations - <u>BiPM</u>, <u>HCE, HCC, BC, UDAC, UDAC, UDAC, UDAC, UDAC, CIBA, Ad. LCC.<sup>23</sup></u> Metrology is a very broad field and may be divided into three basic activities subfields, though there is considerable overlap between the various fields;<sup>3023</sup> Definiting of internationally accepted unit of measurement. Readisating these units of measurement in practice Application of chains of tracability linking measurements made in practice to reference standards. Metrology also has three basic subfields, all of which make use of the three basic activities, though in varying proportions;<sup>42</sup> Scientific or fundemental metrology Applied, technical or industrial metrology Lead metrology

ESD Interconnects overlay Damage Metal 2 Via particle oper short Metal <sup>·</sup> layer thickness particle p-well interfaces: roughness, state density, charges contamination Si crystal: stacking faults, contamination, stress COP (crystal originating particles), epi defects

> Examples of yield distracting defects possible during microelectronics production processes (source: ITRS YE chapter)

## Agenda

#### Introduction

#### Yield Enhancement & ITRS

Metrology

Latest Equipment Developments

- Defect Inspection Tools

- Gi-SAXS

- Vacuum Ultra-Violet (VUV)

- Makyoh Metrology Tool

- Zero-Defect Resizing of Large Crystalline Silicon Wafers with TLS

- 450 mm Developments

- Virtual Metrology (VM)

Summary and Outlook

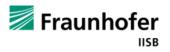

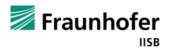

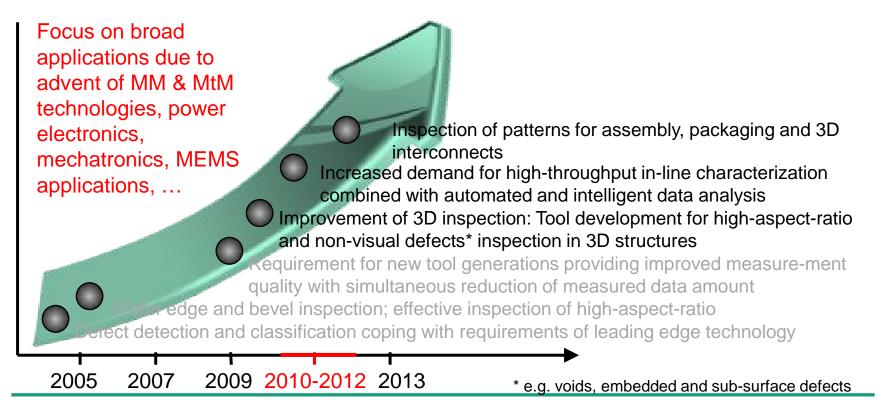

Defect detection is one major scope of activities.

Focus of respective activities was changed and extended with time:

Defect detection for leading edge technologies Defect detection for broad applications ("More Moore" (MM) and "More than Moore" (MtM) technologies, power electronics, mechatronics, MEMS applications, ...)

- Ever remaining challenges for defect inspection:

- Satisfaction of demands arising from shrinking of device dimensions and corresponding critical defect dimensions

- Keeping in-line inspection costs low!

- $\rightarrow$  Need for high sensitivity, high throughput and low CoO tools.

Overview of focus change and extension of defect detection activities within ITRS Yield Enhancement with time

FCMN 2013, Gaithersburg, USA March 25-28, 2013

Fraunhofer

Overview of focus change and extension of defect detection activities within ITRS Yield Enhancement with time

FCMN 2013, Gaithersburg, USA March 25-28, 2013

Overview of focus change and extension of defect detection activities within ITRS Yield Enhancement with time

FCMN 2013, Gaithersburg, USA March 25-28, 2013

Overview of focus change and extension of defect detection activities within ITRS Yield Enhancement with time

How to supplement common defect detection for yield enhancement purposes?

$\rightarrow$  Use of electrical device characteristics and pass or fail characteristics of chips

$\rightarrow$  Use of already present data and statistical/ systematical approaches for data analysis

Inspection of patterns for assembly, packaging and 3D interconnects

Increased demand for high-throughput in-line characterization mbined with automated and intelligent data analysis

provement of 3D inspection

quality with simultaneous reduction of measured data amount

edge and bevel inspection; effective inspection of high-aspect-ratio

erect detection and classification coping with requirements of leading edge technology

2005 2007 2009 2011 2012-2013

FCMN 2013, Gaithersburg, USA March 25-28, 2013

lacking

capacity

measurement

Future challenge:

Appropriate defect

detection despite of

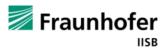

## **Metrology in Semiconductor Manufacturing**

**Production Ramp Curve**

## **Contributions by Fraunhofer IISB**

### Network in Metrology

March 25-28, 2013

# Agenda

#### Introduction

- Yield Enhancement & ITRS

- Metrology

#### Latest Equipment Developments

- Defect Inspection Tools

- Gi-SAXS

- Vacuum Ultra-Violet (VUV)

- Makyoh Metrology Tool

- Zero-Defect Resizing of Large Crystalline Silicon Wafers with TLS

- 450 mm Developments

- Virtual Metrology (VM)

- Summary and Outlook

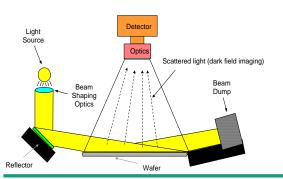

Innovative Meso Defect Inspection (SEA-Project)

#### Short description:

- Implementation of new very high throughput and high sensitivity approach for wafer inspection

- Assessment for 3D-Integration (TSV), patterned and un-patterned wafer inspection

Todays Standard Technology:

#### New Inspection Approach:

FCMN 2013, Gaithersburg, USA March 25-28, 2013

Advances

- Combines bright field illumination, dark field illumination with full wafer illumination without movement of the wafer

- Bright or dark field images of the full 300mm wafer are captured in one shot at high sensitivity of 1-10µm

- Use of full-wafer imaging permits for a first time to rapidly inspect every processed wafer at 100% of the surface

- SW algorithms to extract the defects of interests reliably and to automatically identify defect signatures are being optimized during the project

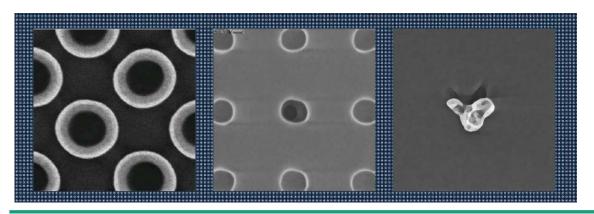

**Defect Inspection Tools**

State of the Art in defect inspection:

- SEM (pixel resolution < 3nm)</p>

- Patterned and unpatterned wafers

- Root cause analysis:

- Difficult due to variety of defect types

- Material information required

- Slow SEM measurements

- throughput limited

- especially for upcoming 450 mm wafer processing

Source: Applied Materials

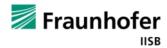

**Defect Inspection Tools**

New developments in defect inspection:

- Increased pixel resolution (< 1nm) enables detection of smaller defects

- Integration of material analysis detectors (e.g. EDX, WDX) for improved defect review

- Utilization of multi-column e-beam SEM systems for improved throughput

Source: Applied Materials

FCMN 2013, Gaithersburg, USA March 25-28, 2013

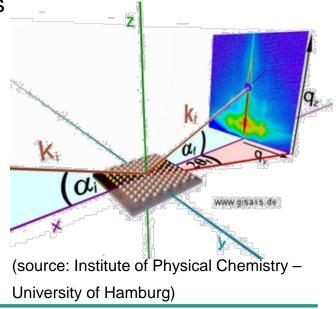

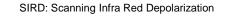

Grazing-incidence small-angle x-ray scattering (GI-SAXS)

Inspection of surface structures in thin layers

- Novel functional layers increase demand for advanced layer characterization techniques (e.g. pore size distribution in low-k materials)

- GI-SAXS enables detection and characterization of surface structures in thin layers → improved defect inspection capabilities

- Full layer characterization through combination with XRR/XRD techniques:

- Film thickness

- Film density

- Crystallographic properties

Vacuum Ultra-Violet (VUV)

Characterization of ultra thin layers at VUV wavelengths

- Key dielectric materials applied in semiconductor manufacturing have unique absorption properties at VUV wavelengths (120 nm to 200 nm)

- VUV measurement applications

- Thickness measurement at ultra thin (<10 nm) layers, e.g. SiO2/Si3N4 (ONO), HfO2

- Determination of material composition, e.g. SiON, high-k layers

- Fast, non-destructive inline characterization

VUV reflectometer for 200 mm/300 mm wafers

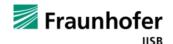

Vacuum Ultra-Violet (VUV)

Investigation of in situ contamination layer removal by VUV/VIS exposure

- Efficiency and control of the contamination removal

- Influence of the VUV exposure on the measurement result

Results

- Repeated measurements clean monolayer from surface

- Selection of measurement point reflecting clean surface depends on type of material

- Layer modification visible as small increase of thickness (1 to 4 pm/pt); reduction by minimization of measurement time

Surface contamination removal and layer modification during the VUV measurement

Vacuum Ultra-Violet (VUV)

Application example – analysis of SiON thin films

Analysis of the measurement point after contamination removal

| Method | N <sub>2</sub> concentration<br>(%) | SiON layer<br>thickness (nm) |

|--------|-------------------------------------|------------------------------|

| VUV    | 9.9 ± 0.35                          | 1.6 ± 0.01                   |

| XPS    | 9.4 ± 0.30                          | 1.9 ± 0.02                   |

- The results show a good correlation to the XPS measurement for nitrogen concentration

- The layer thickness measured by VUV is ≈ 0.3 nm thinner the XPS results which may indicate the present contamination layer measured within the XPS results

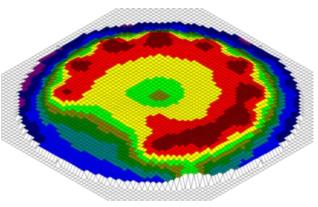

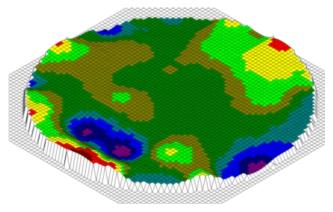

#### Nitrogen concentration map of a 2 nm SiON film with 9% nitrogen

Film thickness map of a 2 nm SiON film with 9% nitrogen

FCMN 2013, Gaithersburg, USA March 25-28, 2013

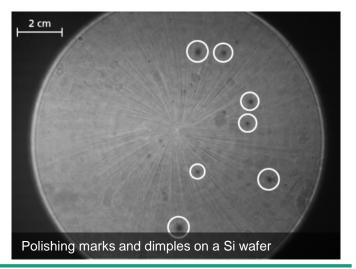

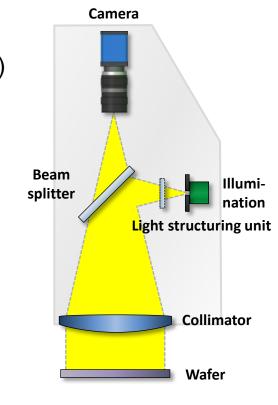

**Makyoh Metrology Tool**

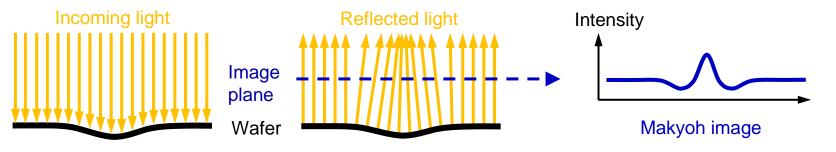

#### Makyoh (magic-mirror) principle:

- The intensity distribution of initially collimated light that was reflected from the wafer surface carries (qualitative) information about the wafer topography

- $\rightarrow$  real-time defect detection

FCMN 2013, Gaithersburg, USA March 25-28, 2013

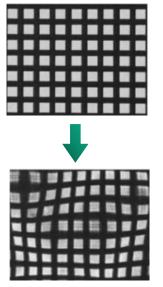

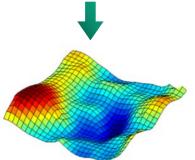

**Makyoh Metrology Tool**

### **Quantitative Makyoh**

Structured illumination is used to quantify the measurement

- Projection of patterns e.g. gratings

(binary intensity coding) or

continuous (color) patterns (multilevel intensity coding or multiwavelength coding)

- Detect pattern distortion

- Calculate surface slopes

- Retrieve height topography by 2Dintegration

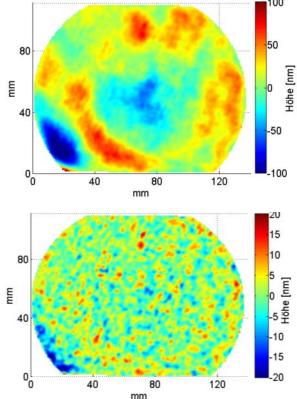

Flatness (top) and Nanotopography (bottom) of a polished Si wafer

FCMN 2013, Gaithersburg, USA March 25-28, 2013

**Makyoh Metrology Tool**

- Current specifications of prototype

- Measuring area:  $\otimes$  135 mm ( $\rightarrow$  R&D for  $\otimes$  300 mm)

- Vertical resolution: < 20 nm</p>

- Lateral resolution: 100 µm

- Benefits

- Large measuring area, no scanning

→ high throughput

- Fast defect detection

- Robust to external vibrations due to slope measurement

Schematic setup

FCMN 2013, Gaithersburg, USA March 25-28, 2013

Zero-Defect Resizing of Large Crystalline Silicon Wafers with TLS

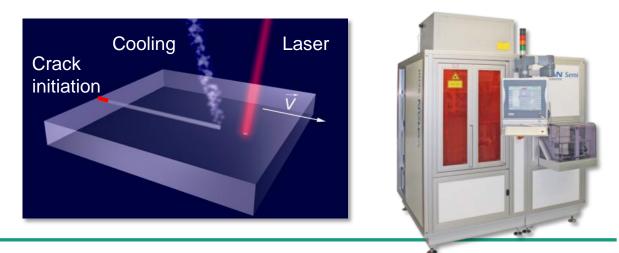

Thermal Laser Separation (TLS)

- Principle of TLS: Crack guiding with thermally induced mechanical stress

- Step Crack initiation: With diamond tip or ablation laser

Predetermined cleaving point

- Step Cleaving: Laser-based heating, subsequent water cooling

High tensile stress inside the overlap zone between heating and cooling results in a complete cleaving of the substrate

FCMN 2013, Gaithersburg, USA March 25-28, 2013

Zero-Defect Resizing of Large Crystalline Silicon Wafers with TLS

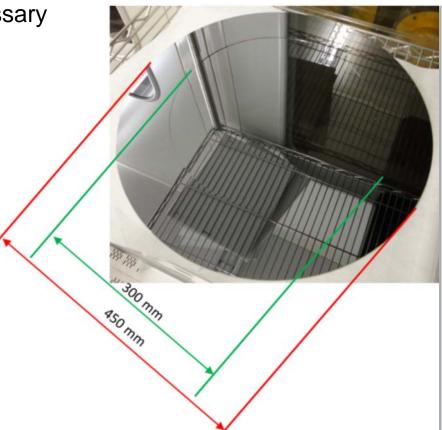

TLS for resizing large crystalline Si wafers

- Cleaving process is not bound by lattice planes

- Mounting on tape and frame is not necessary

- Single crystalline (100) Si wafers

- 200 W cw fiber coupled **fiber laser**

- **NIR** wavelength

- 7-9 ml/min water flow rate for cooling

FCMN 2013, Gaithersburg, USA March 25-28, 2013

Zero-Defect Resizing of Large Crystalline Silicon Wafers with TLS

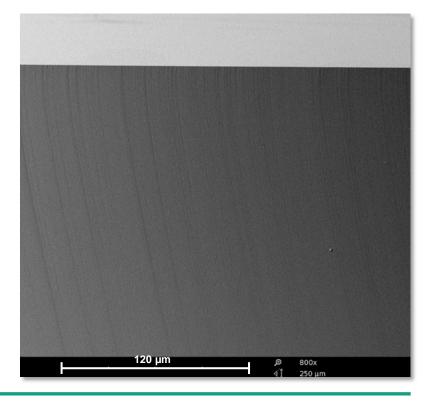

Results of resizing large Si wafers with TLS

### High edge quality

- Zero chipping

- Smooth side walls

- No residual mechanical stress

- ➔ High bending strength

- Short process time

- Feed rate 20-40mm/s

- 3-5min/wafer (300mm → 200mm)

- ➔ High throughput

- TLS is a promising technique for zero-defect resizing

FCMN 2013, Gaithersburg, USA March 25-28, 2013

### 450 mm Activities – Equipment as well as Metrology Equipment

Requirements for 450 mm and possible benefits for smaller diameters include:

- Improved equipment performance

- Lower defect generation

- Significantly better control

- Advanced sensors

- Faster handling and processing

- Higher equipment reliability

- Significantly better data processing

Fraunhofer

FCMN 2013, Gaithersburg, USA March 25-28, 2013

### 450 mm Tools

### Impact of 450 mm Wafer Diameter

### on Equipment and Metrology Tools

| Diameter  | 300 mm              | 450 mm               |

|-----------|---------------------|----------------------|

| Thickness | 775 µm              | 925 µm               |

| Area      | 706 cm <sup>2</sup> | 1589 cm <sup>2</sup> |

| Impacted Areas  | Focus Items                                                                                                                                                                                                |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processes       | Process uniformity, contamination, thermal effects/<br>uniformity, (cleaning, polishing, deposition, etch, anneal,<br>)                                                                                    |

| Lithography     | Increase of area by 2.25 times requires high performance<br>– high speed litho                                                                                                                             |

| Handling        | Deformation (→stress), transport issues, wafer translation<br>(large distances, acceleration and settling times increase,<br>vertical drift along the wafer)                                               |

| Metrology       | Stages and handling, mapping capabilities, increase<br>of area by 2.25 times requires high performance –<br>high speed metrology (inspection), dimensional<br>change due to thermal expansion coefficient, |

| Data Management | Amount of data, data quality,                                                                                                                                                                              |

#### 450 mm Activities - Material

- Wafer Manufacturing

- Important Wafer Parameters

- Required Metrology

FCMN 2013, Gaithersburg, USA March 25-28, 2013

#### **IMPORTANT WAFER PARAMETERS/CHARACTERISTICS**

- Specified wafer parameters are:

- Resistivity

- Oxygen concentration

- Bulk defects (dislocations, COP, swirl,...)

- Surface defects (LLS, particles, PID,...)

- Metal contamination (bulk, surface)

- Local flatness

- Global Flatness, Nanotopography

- Edge profile

- Roughness

- Backside conditions

#### All parameters have to be verified by adequate metrology!

**Courtesy of Siltronic**

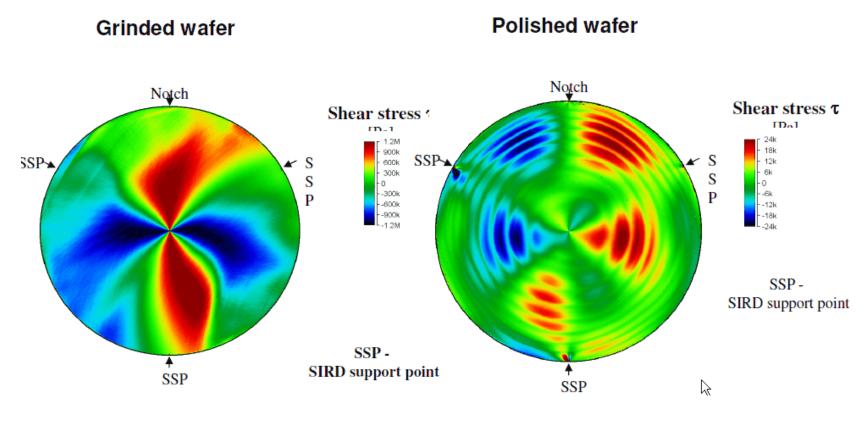

#### **Example: Bulk wafer metrology**

#### Stress measurements

FCMN 2013, Gaithersburg, USA March 25-28, 2013

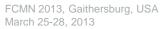

#### **Example: Bulk wafer metrology**

#### Interferometer Measurement:

Total Thickness Variation: 1.4 µm

### **ULE: Two chuck design options**

### support at 3 points (Bessel's radius)

Massive chuck:

19 mm max. thickness (by mass constraint)

Light-weight chuck:

32 mm max. thickness bore holes unsymmetric (below centerplane)

IISB

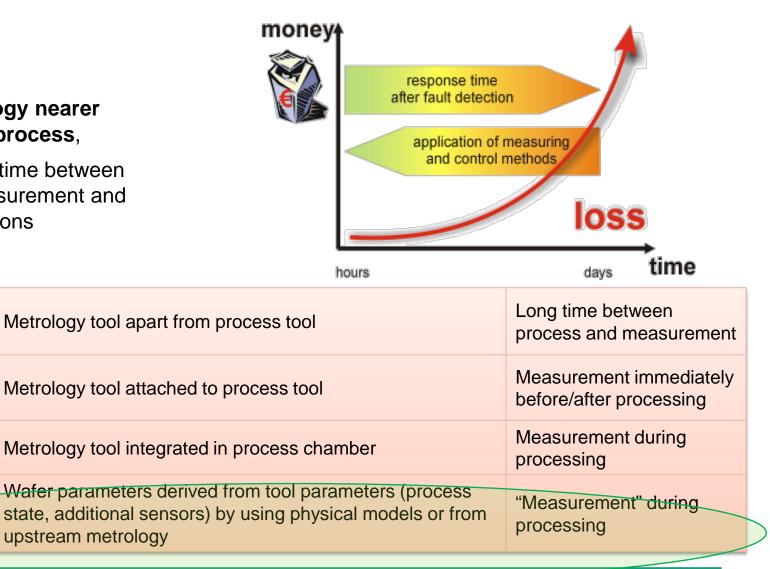

### Metrolgy as Basis for Advanced Process Control (APC)

#### **Objective:**

Offline Metrology

In situ Metrology

Virtual Metrology

Inline

Metrology

#### Draw metrology nearer towards the process,

to reduce the time between process, measurement and corrective actions

upstream metrology

FCMN 2013, Gaithersburg, USA March 25-28, 2013

🗾 Fraunhofer IISB

## Latest Developments in Manufacturing Science

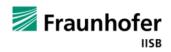

Virtual Metrology (VM)

#### VM definition

Technology of prediction of post process metrology variables (either measurable or non-measurable) using process and wafer state information that could include upstream metrology and/or sensor data.

#### VM benefits

- Support or replacement of stand-alone and in-line metrology operations

- Support of FDC, run-to-run control, and PdM

- Improved equipment control for VM running on equipment level

- Improved understanding of unit processes

Process/process module n-1 Pre-process module n-1 FDC system VM module Quality parameter

FCMN 2013, Gaithersburg, USA March 25-28, 2013

# Latest Developments in Manufacturing Science

Virtual Metrology (VM)

Virtual Equipment test bench for development and test of VM models

- Utilization of history fab data

- Simulation of relevant equipment and process behaviour

- Application of noise, typical faults, and process drifts

FCMN 2013, Gaithersburg, USA March 25-28, 2013

Fraunhofer الله Fraunhofer

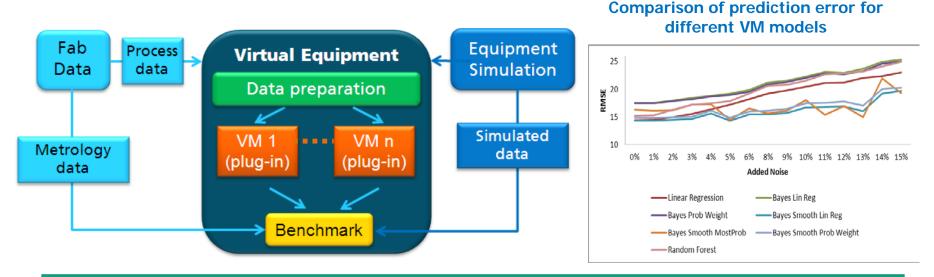

# Latest Developments in Manufacturing Science

Virtual Metrology (VM)

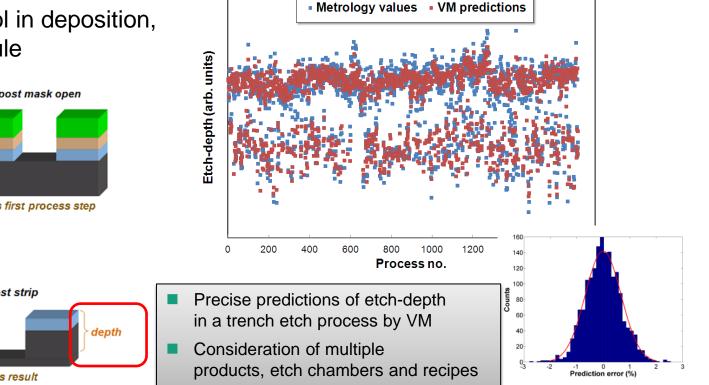

Prediction of etch-depth in a trench etch process

Objective: Establish wafer-fine run-to-run control in deposition, etch, CMP module

FCMN 2013, Gaithersburg, USA March 25-28, 2013

\*)Source: ISMI

Fraunhofer

FCMN 2013, Gaithersburg, USA March 25-28, 2013

\*)Source: ISMI

Fraunhofer

FCMN 2013, Gaithersburg, USA March 25-28, 2013

## **Summary and Outlook**

Metrology is a non-productive step: ideally ZERO metrology

- BUT reality:

- Increasing number of non-product wafers during

- Process development

- Pilot production

- Transfer into high-volume manufacturing

- New developments needed

- Advanced strategies needed

- Advances required by

- Technology nodes

- Wafer diameters

- Quality improvements

Part of the presented work has been performed within the context of the European ENIAC Joint Under-taking projects IMPROVE and EEMI450, the Catrene project UTTERMOST, and the EU projects, SEA-NET and SEAL.

FCMN 2013, Gaithersburg, USA March 25-28, 2013

# www.iisb.fraunhofer.de

FCMN 2013, Gaithersburg, USA March 25-28, 2013