IR-Drop Based Electromigration Assessment Materials Data and Characterization Requirements

### Valeriy Sukharev<sup>1</sup>, Jun-Ho Choy<sup>1</sup>, Armen Kteyan<sup>2</sup>, and Xin Huang<sup>3</sup>

<sup>1</sup>Mentor Graphics, Fremont, CA, USA <sup>2</sup>Mentor Graphics, Armenia <sup>3</sup>UCR, Riverside, CA, USA

### Outline

- Introduction and motivations

- Chip design verification for sign-off EM assessment

- On-chip interconnect elemental unit for EM reliability vs. standard test-structures

- A role of interconnect redundancy in the resistance degradation

- Power/ground grid vs. signal nets

- A role of residual stress and temperature in EM-induced degradation

- Methodology of across-interconnect residual stress assessment

- Methodology of across-interconnect temperature assessment

- Voiding-induced IR-drop degradation parametric failure

- Multi-scale materials data as input for the simulation

- Characterization techniques for models/methodology validation

### **Reliability vs. Performance**

• Current assessment of chip reliability kills chip performance!

#### **Question**:

How can one predict an IR-drop degradation for a particular chip design?

#### **Answer**:

- Accurate physics

- Solid models

- Fast and clever algorithm

- Reduction of the operation frequency or voltage at the instance in time when IR drop degradation (increase) exceeds a projected value is killing the chip performance while not affecting the chip EM reliability.

### **Electromigration Basics**

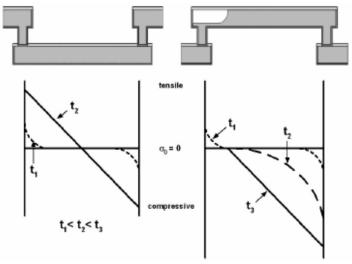

- Material depletion and accumulation occurring at the sites of atomic flux divergence results the localized tensile and compressive stresses

- Resulting stress gradient creates a backflow atomic flux

- If the electron-wind and back-stress forces balance each other before the critical stresses needed for void nucleation or metal extrusion are developed the interconnect segment will be immortal.

### **General Physical Model**

If atom an flux divergences somewhere inside metal line then accumulation or depletion of atoms is happening there:  $\frac{\partial N_A}{\partial t} + \vec{\nabla} \vec{J}_A = 0 \implies \frac{\partial \sigma_{Hyd}}{\partial t} = \frac{\partial}{\partial x} \kappa \left( \frac{eZ\rho j}{\Omega} + \frac{\partial \sigma_{Hyd}}{\partial x} \right)$  $\bigwedge z$ Anode area Cathode area W Fast diffusion  $J_{3}(x+dx)$ Η x + dxх Slow diffusion Slow diffusion Solution of Korhonen's equation: 1000 800  $\sigma(x,t) = \sigma_{res} - \frac{eZ\rho j}{\Omega} \left( x + 4L \sum_{n=0}^{\infty} \frac{\cos(m_n(1/2 + x/L))}{m_n^2 \exp(m_n^2 \kappa t/L^2)} \right)$  $\sigma_{\scriptscriptstyle crit}$ 600 500  $\sigma_{\scriptscriptstyle crit}$ (MPa) 000 (MPa)  $\sigma_{\mathsf{Hyd}}$  (MPa)  $\sigma_{\mathsf{Hyd}}$ Condition for the stable void formation: 200 -500  $\sigma_{crit} = \sigma_{res} - \frac{eZ\rho j}{\Omega} \left( x + 4L \sum_{n=0}^{\infty} \frac{\cos(m_n(1/2 + x/L))}{m^2 \exp(m^2 \kappa \cdot t / L^2)} \right)$ I nuc (b) (a) -1000 0 2 40 60 80 100 0 8 10 0 20  $x (\mu m)$ t (s)  $\times 10^7$ Nucleation time for stable, growing void: Evolution of the hydrostatic stress (a) along the metal line loaded with DC current, and at the cathode end of line, (b)  $j = 5x10^9 A/m^2$ , T =  $t_{nuc} \approx \frac{L^2}{2D_0} \frac{k_B T}{\Omega B} e^{\frac{E_V + E_{VD} - \Omega^* \sigma_T - eZ\rho jL/2}{k_B T}} \ln \left\{$ 400K. V. Sukharev, "Beyond black's equation: Full-chip Em/Sm assesment in 3D IC stack," Microelectronic  $\cdot \sigma_{\scriptscriptstyle crit}$ Engineering, vol. 120, pp. 99-105, May 2014. © 2010 Mentor Graphics Corp.

www.mentor.com

FCMN2015, Dresden

Graphic

### **Black's equation based MTTF**

- TTF averaged with the accepted distribution function provides mean time to failure (MTTF).

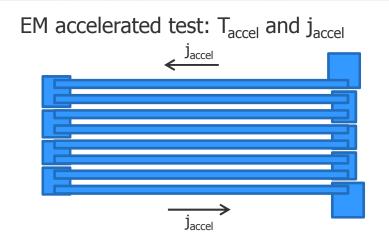

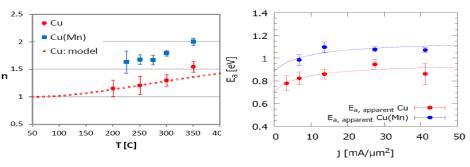

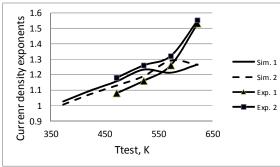

- A set of calculated MTTF obtained for different T<sub>accel</sub> and j<sub>accel</sub> is used for extraction of the current density exponent *n* and apparent activation energy *E* used in the Black's equation:

$$MTTF = \frac{A}{j^n} \exp\left\{\frac{E}{kT}\right\}$$

Assuming an "universal" character of the extracted *n* and *E*, the MTTF at the used conditions is:

$$MTTF_{use} = MTTF_{accel} (j_{accel} / j_{use})^n \exp\left\{\frac{E}{k} \left(\frac{1}{T_{use}} - \frac{1}{T_{accel}}\right)\right\}$$

Different lines characterizing by different microstructures reveal different times to failure (TTF)

Experiments demonstrates that **n** and **E** by themselves are the functions of **j** and **T**

M. Hauschildt, C. Hennesthal, G. Talut, et al. (GF & Fraunhofer), 2C.1.1, IRPS 2013

© 2010 Mentor Graphics Corp. www.mentor.com

FCMN2015, Dresden

### EM Assessment – PROBLEM!

- Stress and temperature dependency of the current density exponent,

- Current density and temperature dependency of the activation energy

- Across-interconnect temperature and residual stress variation

ALL THESE FACTORS MAKE QUESTIONABLE USING BLACK EQUATION and BLECH LIMIT (CRITICAL PRODUCT) FOR ACCURATE EM ASSESSMENT!

$$t_{nuc} = \frac{A(\vec{r}, \sigma_{res})}{j^{n(T, \sigma_{res})}} \exp\left\{\frac{E(j, T)}{kT}\right\}$$

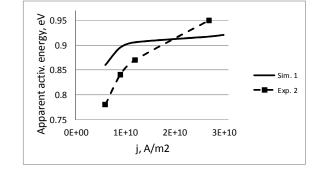

$$(j \times L)_{crit} = \frac{\Omega(\sigma_{EM} \pm \sigma_{res}(\vec{r}, T))}{eZ\rho}$$

#### **EM assessment requires:**

- Current density assessment

- Temperature assessment

- Residual stress assessment

V. Sukharev and E. Zschech, "Multi-scale simulation flow and multi-scale materials characterization for stress management in 3D through-silicon-via integration technologies -Effect of stress on 3D IC interconnect reliability", AIP Conference Proceedings 1601, 18 (2014); DOI: 10.1063/1.4881339

> © 2010 Mentor Graphics Corp. www.mentor.com

FCMN2015, Dresden

### **Chip-scale EM assessment**

#### **Interconnect functionality**

- interconnectivity for signal propagation

*bidirectional pulsed currents*

- voltage delivery

*-unidirectional current*

- <u>power grids, more</u> <u>susceptible to EM effect</u>

Interconnect tree

#### **Traditional segment-based EM assessment**

- single segment based stress analysis

- assume individual segment is confined by diffusion barriers

- *however*, in power grids, atoms can diffuse in the interconnect tree, stress redistribution

- EM induced failure rate of the individual segment

#### **EM induced degradation in power grids**

- high level of redundancy

- Failure: loss of performance, parametric failure

- cannot deliver needed voltage to any point of the circuitry

#### New methodology for EM assessment:

- IR drop based assessment

- Forphysics based models for void initiation and evolution

### **STRESS ASSESSMENT**

### **IC Problem**

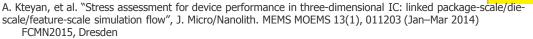

Consumer demand is driving the need for thinned substrates, introduction of new connectivity structures (e.g. 3D stacking, TSVs, C4- and u-bumps) that cause unexpected device performance

You don't want this to happen when stacking a thin die on top of a thick bottom die How to avoid ?!

How to design for this !

IMEC

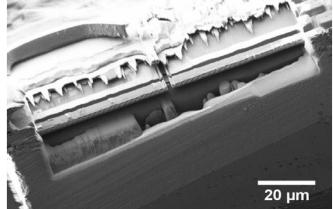

Mechanical stress caused by IC architecture and packaging impacting MOSFET characteristics/performance – Chip-Package-Interaction (CPI)

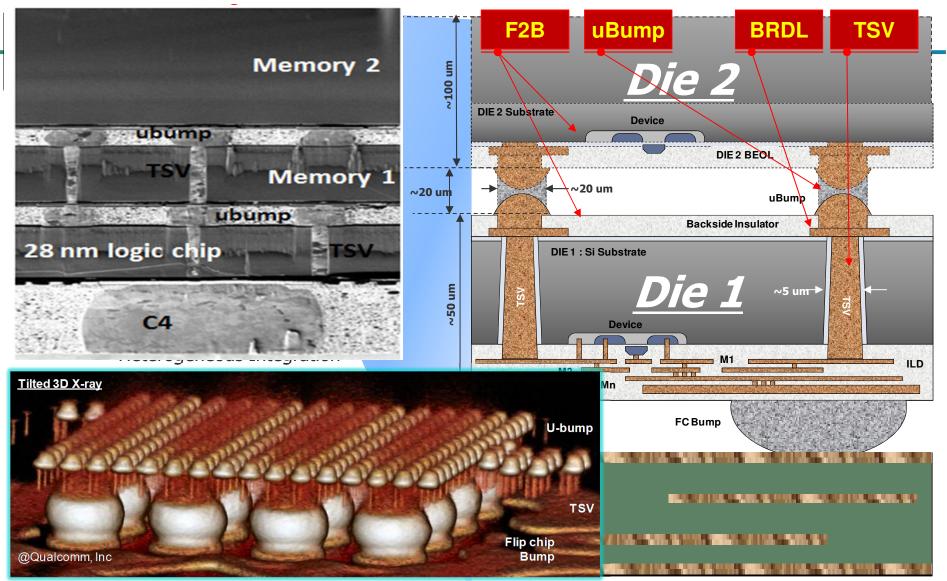

#### What is 3D TSS (Through Si Stacking) Technology

R. Radojcic, E. Zschech, V. Sukharev, "Managing the Effects of Mechanical Stress on Performance of Modern SoCS", iMAPS 2013, Hand-out for Tutorial T7.

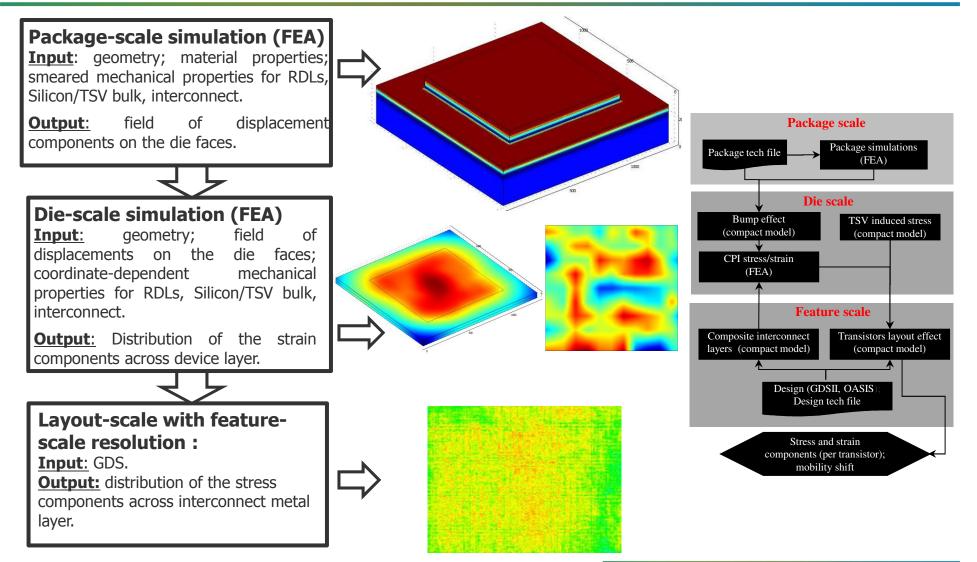

#### Multiscale methodology for calculation of device-todevice variation of stress: Stress Exchange Format

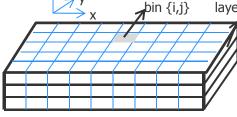

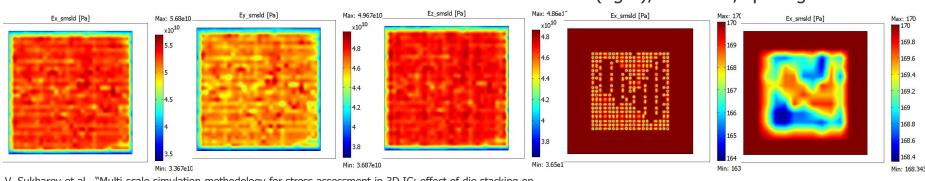

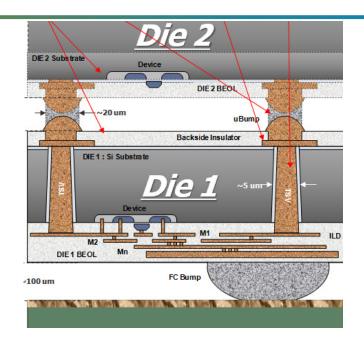

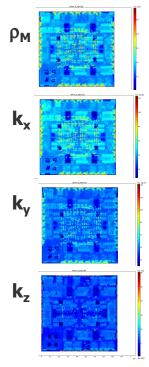

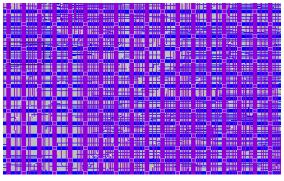

### **Effective mechanical properties of BEoL, BRDL interconnects and Si/TSV bulk layer**

- Theory of the mechanical properties of anisotropic composites is employed.

- Required input: (a) Thermo-mechanical properties of each material metal, dielectric: CTE, Young's moduli, Poisson factors; (b) fraction of dispersed phase; (c) routing direction of the metal layer.

- For each bin of each layer of interconnect, depending on routing direction: for example the Young's modulus:

$$\begin{split} E_{\parallel}^{i,j} &= E_{M} \rho_{M}^{i,j} + E_{D} \left( 1 - \rho_{M}^{i,j} \right) \\ E_{\perp}^{i,j} &= \frac{E_{M} E_{D}}{E_{D} \rho_{M}^{i,j} + E_{M} \left( 1 - \rho_{M}^{i,j} \right)} \end{split}$$

Young's modulus components for M1 layer

E<sub>x</sub> for bulk Si/TSVs: bin size 20 (left) and 100nm (right), TSV 6nm, spacing 40nm.

V. Sukharev et al., "Multi-scale simulation methodology for stress assessment in 3D IC: effect of die stacking on device performance," J. Electron. Test. 28(1), 63–72 (2012).

© 2010 Mentor Graphics Corp. www.mentor.com

FCMN2015, Dresden

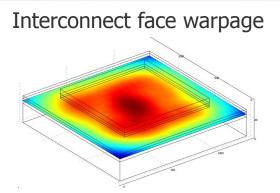

### **Supported Compact Models**

1. Package-scale: Warpage-Induced Stress

2. Compact Model for Bump-Induced Displacements

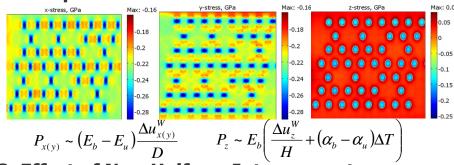

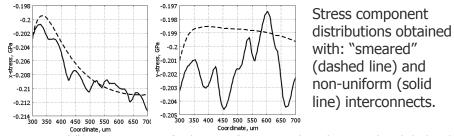

3. Effect of Non-Uniform Interconnect

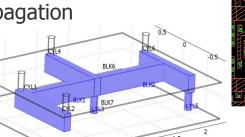

#### 4. Compact Model for TSV-Induced Stress:

Based on: S. Ryu, K. Lu, X., et Al., , "Impact of Near-Surface Thermal Stresses on Interfacial Reliability of Through-Silicon Vias for 3-D Interconnects", IEEE TDMR, VOL. 11, NO. 1, (2011) pp. 35-43

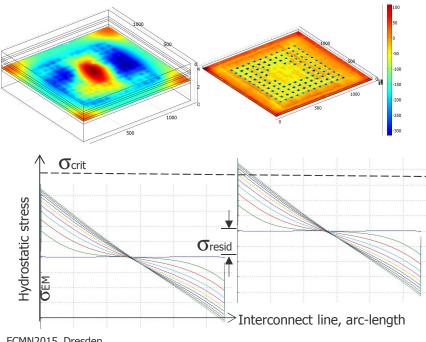

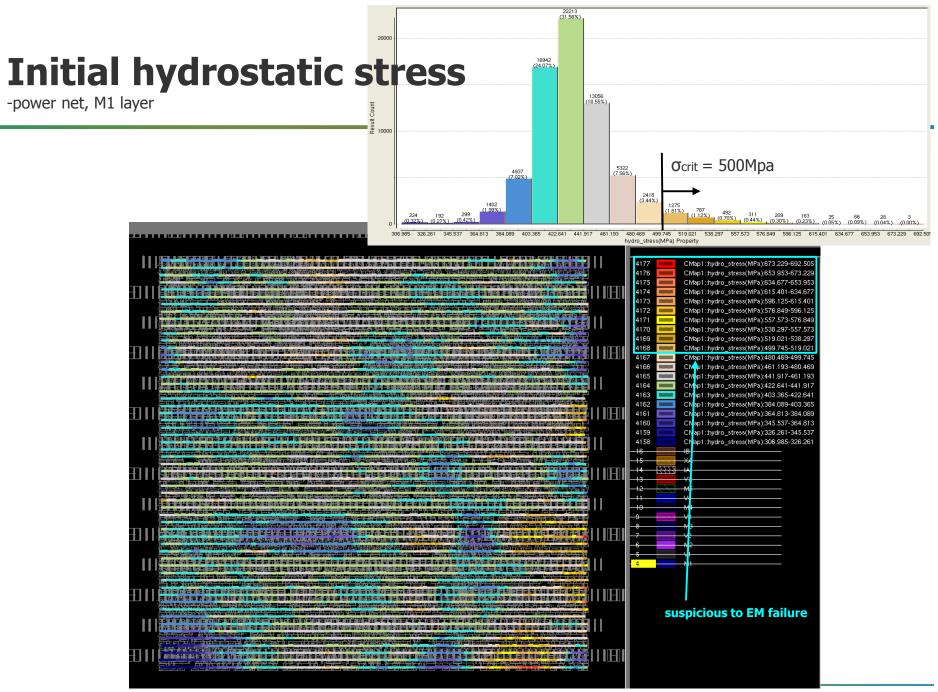

### **Residual stress in on-chip interconnect**

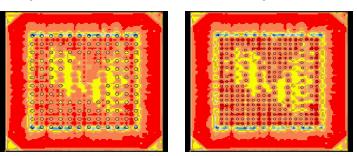

Hydrostatic stress in M1 layer

Residual (hydrostatic) stress distribution across M1 layer with the overlaid C4 bumps, (left) and ubumps (right).

Interconnect tree is a elemental EM reliability unit representing a continuously connected, highly conductive metal (Cu) lines within one layer of metallization, terminated by diffusion barriers.

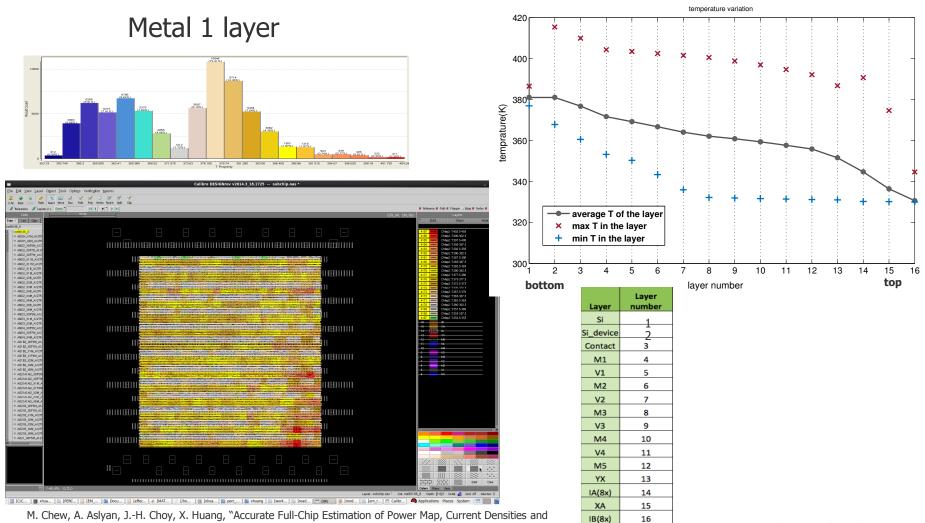

### **TEMPERATURE ASSESSMENT**

- MGC's effective thermal properties extractor.

- Each interconnect layer is considered as a composite: a mixture of metal fibers included in a dielectric matrix.

- Calculates the effective thermal conductivity ( $k_i$ , i=x,y,z), specific heat of each interconnect layer as a function of local metal density ( $\rho_M$ ).

- Lateral components  $K_{x,y}$  inside each metal layer are determined by a routing direction:

- Parallel to the routing direction:

- Normal to the routing direction:

- A vertical component:

$$k_{\perp} = k_{ILD} \left[ 1 + \frac{\rho_M}{k_{ILD} / (k_M - k_{ILD}) + (1 - \rho_M) / 2} \right]$$

$$k_Z = \rho_M k_M + (1 - \rho_M) k_{ILD}$$

$k_{\mu} = \rho_{\nu} k_{\nu} + (1 - \rho_{\nu}) k_{\mu\nu}$

#### Thermal Netlist Builder.

A die is represented by a 3D array of cuboidal thermal cells. Each cell contains a thermal node, and is characterized by local effective thermal properties(R<sub>th</sub>, C<sub>th</sub>).

The array transforms into a thermal netlist.

#### • SPICE simulator.

- Calculates transistor power consumption.

- Solves for temperature for each thermal node.

Effective thermal properties of a die

# From effective thermal props to thermal netlist

- Construct an array of cuboidal cells of dimension, LxLxt : "L" is user-supplied binSize.

- For each cell, MGC's engine uses Calibre to extract local metal density, and calculates effective thermal properties.

- Thermal netlist builder transforms effective thermal properties into R<sub>th</sub> and C<sub>th</sub>.

$$R_{top/bottom.i} = \frac{1}{k_{z,i}} \frac{t_{M6}/2}{L^2}; R_{north/south,i} = \frac{1}{k_{y,i}} \frac{L/2}{t_{M6}L}; R_{east/west,i} = \frac{1}{k_{x,i}} \frac{L/2}{t_{M6}L}$$

$$C_{cell,i} = S_i \cdot (L \cdot L \cdot t_{M6})$$

- The array transforms into a thermal netlist.

- Consideration on boundaries

- Fixed T with V source & R=0; Insulation with large R.

#### **Power map**

#### **Temperature across M1**

$t_{M6}$

t<sub>v5√</sub>

C<sub>M5</sub>

© 2010 Mentor Graphics Corp. www.mentor.com

Cell i:  $(\rho_{Mi}, k_{xi}, k_{vi}, k_{zi}, S_i)$

z // top

y // north

\_ x // east

FCMN2015, Dresden

## INTERCONNECT SCALE EM MODELING

### **Chip-scale EM assessment**

#### **Interconnect functionality**

- interconnectivity for signal propagation

*bidirectional pulsed currents*

- voltage delivery

*-unidirectional current*

- <u>power grids, more</u> <u>susceptible to EM effect</u>

Interconnect tree

#### **Traditional segment-based EM assessment**

- single segment based stress analysis

- assume individual segment is confined by diffusion barriers

- *however*, in power grids, atoms can diffuse in the interconnect tree, stress redistribution

- EM induced failure rate of the individual segment

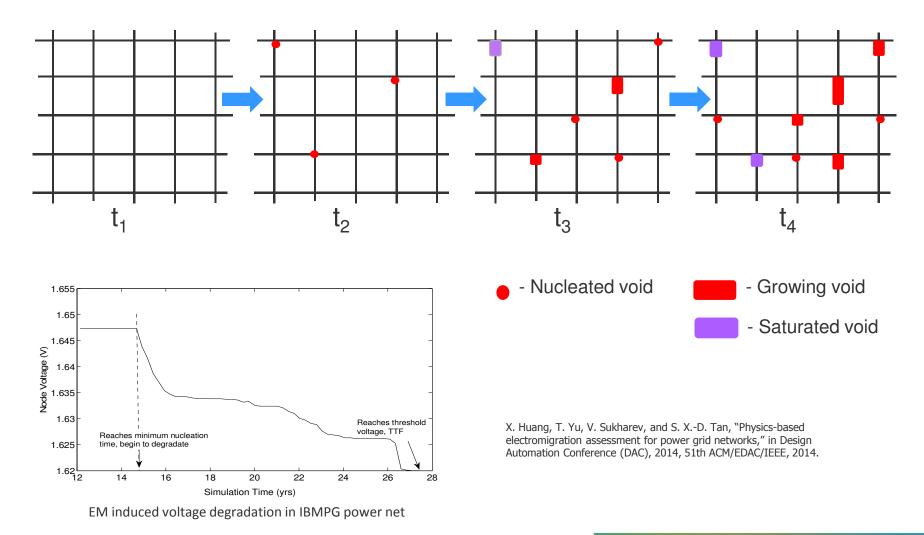

#### **EM induced degradation in power grids**

- high level of redundancy

- Failure: loss of performance, parametric failure

- cannot deliver needed voltage to any point of the circuitry

#### New methodology for EM assessment:

- IR drop based assessment

- Forphysics based models for void initiation and evolution

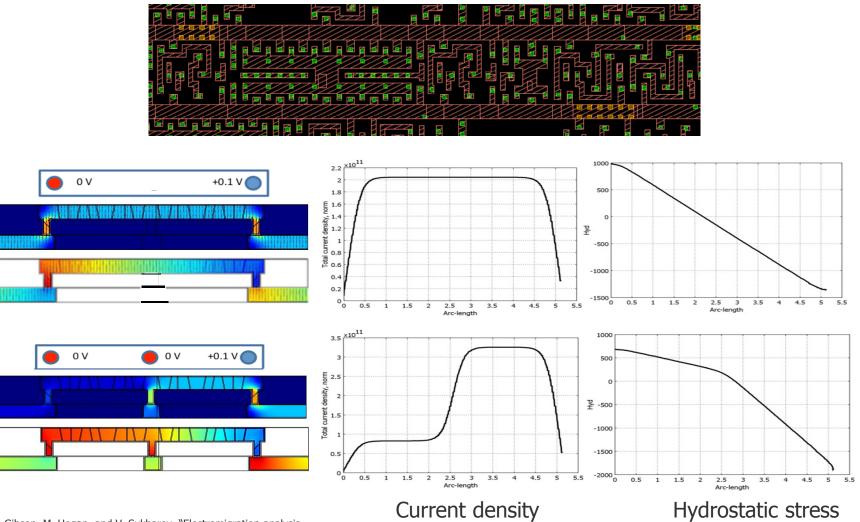

### Interconnect segment vs. wire

P. Gibson, M. Hogan, and V. Sukharev, "Electromigration analysis of full-chip integrated circuits with hydrostatic stress," in *2014 IEEE International Reliability Physics Symposium*, 2, pp. 2.1–2.7, 2014.

FCMN2015, Dresden

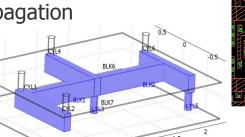

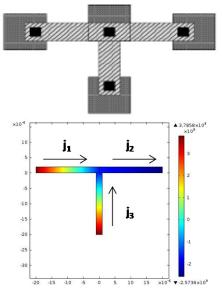

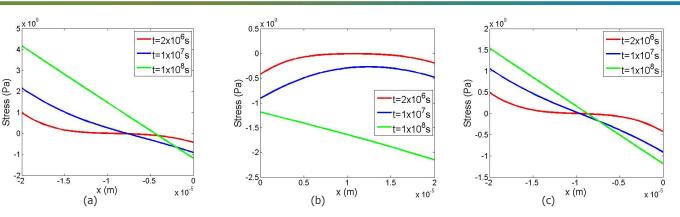

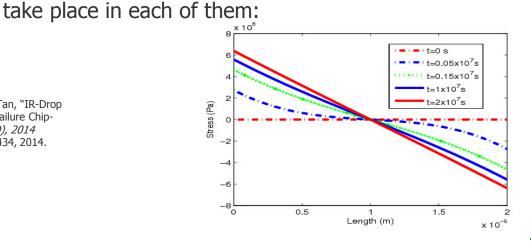

### **Closed-form analytical solution for stress evolution in the multi-branched interconnect tree**

Evolution of the stress distribution along the segment of the shown T-shaped tree; (a) line 1, (b) line 2, and (c) line 3.

If we disassemble these brunches a standard stress evolution will

T-shaped interconnect tree with shown directions of the electron flows.

> V. Sukharev, X. Huang, H.-B. Chen, and S. X.-D. Tan, "IR-Drop Based Electromigration Assessment: Parametric Failure Chip-Scale Analysis" in *Computer-Aided Design (ICCAD), 2014 IEEE/ACM International Conference on*, pp. 428–434, 2014.

© 2010 Mentor Graphics Corp. www.mentor.com

FCMN2015, Dresden

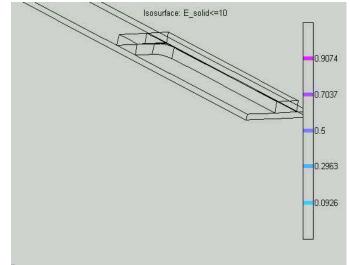

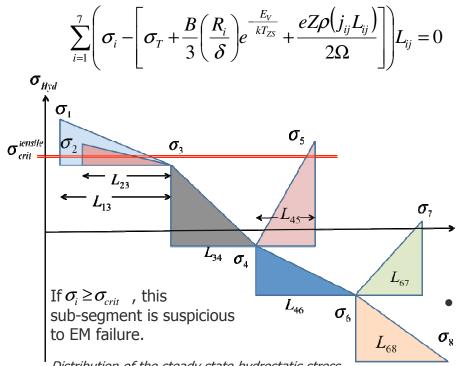

### Steady state distribution of the hydrostatic stress inside interconnect tree in void-less regime

Assume (just for a moment) that the void less steady state was achieved in the tree.  $\sigma_{i}^{cathod} - \sigma_{j}^{anode} = \Delta \sigma_{ij} = \frac{eZ\rho(j_{ij}L_{ij})}{2}$

*For the steady state:*

Consider the redistribution of the atoms between sub-segments due to unblocked sub-segment ends:

Distribution of the steady state hydrostatic stress

along the considered tree X. Huang, T. Yu, V. Sukharev, and S. X.-D. Tan, "Physics-based electromigration assessment for power grid networks," in Design

Automation Conference (DAC), 2014, 51th ACM/EDAC/IEEE, 2014.

2 5 J<sub>23</sub> 154 176 34 3 6 4  $J_{46}$ J68  $J_{13}$ П 8 j<sub>mn</sub> is the density of electron flow 1 (opposite to the current direction).

Example of an interconnect tree

Previously, we use uniform temperature distribution:

The shortest void nucleation time is characterized by the biggest steady state stress  $\sigma_{\rm m}(j_1, j_{2,...}, j_n)$ ,

$$t_{nuc}^{\rm m} \approx \frac{L_{\rm max/min}^2}{2D_0} e^{\frac{E_V + E_D}{kT}} \frac{kT}{\Omega B} \exp\left\{-\frac{f\Omega\sigma_{\rm m}(j_1, j_{2,...}, j_n)}{kT}\right\}$$

$$\cdot \ln\left\{\frac{\sigma_{\rm m}(j_1, j_{2,...}, j_n) - \sigma_{\rm Res}}{\sigma_{\rm m}(j_1, j_{2,...}, j_n) - \sigma_{\rm crit}}\right\}$$

With temperature variation: Void nucleation time is affected by both T and hydrostatic stress. Consider both factors to find the first nucleated void  $(\min\{t_{nuc}^{i}\})$

> © 2010 Mentor Graphics Corp. www.mentor.com

FCMN2015, Dresden

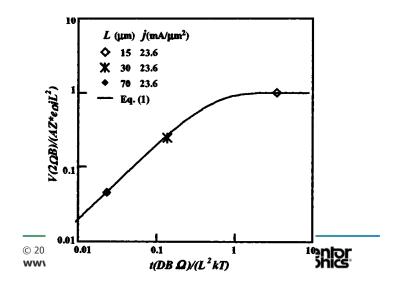

### Voiding

When void is nucleated the stress at the void surface is zero. The solution of the stress kinetics equation with the zero-flux condition at the downstream (anode) end of the line is [J. He and Z. Suo, AIP Conf. Proceedings, vol. 741, 2004]:  $(t \ge t_{nuc})$

$$\sigma(x,t) = -\frac{eZ\rho jL}{\Omega} \left( \frac{x}{L} + \frac{8}{\pi^2} \sum_{n=0}^{\infty} \frac{(-1)^n}{(2n-1)^2} \sin\left[ \frac{(2n-1)\pi x}{2L} \right] \exp\left\{ -\left(\frac{2n-1}{2}\pi\right)^2 \frac{t}{\tau} \right\}$$

Once the stress field is solved, the void volume is calculated from the volume of atoms drifted into the line:

$$\tau = \frac{L^2}{\kappa} = \frac{L^2 k_B T}{DB\Omega}$$

Void Je electron flow Atoms from area occupied by void

$$V = -A \int_{0}^{L} \Omega N_{PL} dx = -A \int_{0}^{L} \Omega \left(\frac{\sigma}{B} N_{A}\right) dx = -A \int_{0}^{L} \left(\frac{\sigma}{B}\right) dx = \frac{eZ\rho j L^{2} A}{2\Omega B} \left(1 + \frac{32}{\pi^{3}} \sum_{n=0}^{\infty} \frac{(-1)^{n}}{(2n-1)^{2}} \exp\left\{-\left(\frac{2n-1}{2}\pi\right)^{2} \frac{t}{\tau}\right\}\right)$$

There are two limiting cases for volume void: 1. Short time; stress in the line is small, so

$$\Gamma(\vec{r}) = \frac{D}{\Omega k_B T} e Z \rho j$$

and  $V = \Omega \Gamma A t = \frac{e Z \rho j D A t}{k_B T}$

2. Steady state was reached; the atomic flux vanishes, void volume is saturated:

$$\sigma(x) = -\frac{eZ\rho jx}{\Omega}$$

and  $V_{sat} = -A \int_{0}^{L} \left(\frac{\sigma}{B}\right) dx = \frac{eZ\rho jL^2 A}{2\Omega B}$

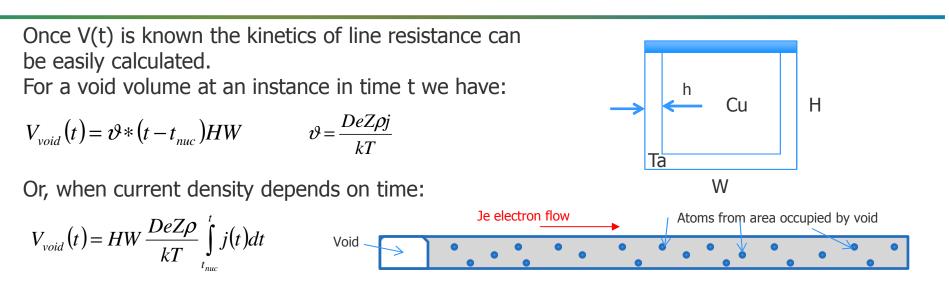

### Void growth-induced line resistance change

For the corresponding change in the line resistance we can write:

$$\begin{split} \Delta R &= R_{Ta}^{Void} - R_{Cu}^{Void} \\ \frac{1}{R_{Ta}^{Void}} &= \frac{1}{R_{Ta}^{void} - wall} + \frac{1}{R_{Ta}^{void} - wall} + \frac{1}{R_{Ta}^{void} - bottom} \\ R_{Ta}^{void} - wall &= \rho_{Ta} \frac{\vartheta * (t - t_{nuc})}{hH}; R_{Ta}^{void} - bottom} = \rho_{Ta} \frac{\vartheta * (t - t_{nuc})}{hW}; R_{Cu}^{Void} = \rho_{Ta} \frac{\vartheta * (t - t_{nuc})}{HW} \\ \Delta R(t) &= \vartheta * (t - t_{nuc}) \left[ \frac{\rho_{Ta}}{h(H + 2W)} - \frac{\rho_{Cu}}{HW} \right] \approx \vartheta * (t - t_{nuc}) \frac{\rho_{Ta}}{h(H + 2W)} = \frac{V_{void}(t)\rho_{Ta}}{h(H + 2W)HW} \end{split}$$

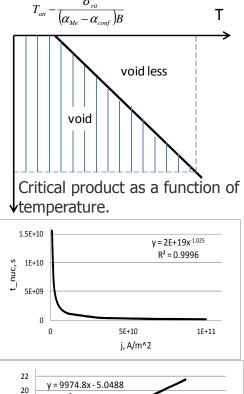

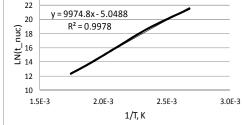

#### Void nucleation time and void growth time as the functions of the current density and test temperature

|          | Void nucleation |          |          |          |          |          | Void growth |                                                                                                                                                                                                |                                                                                                                                                               |                                                                                                                              |                                                                                             |                                                            |                           |

|----------|-----------------|----------|----------|----------|----------|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------------|

| J/Ttest  | 323             | 373      | 423      | 473      | 523      | 573      | 623         | 373                                                                                                                                                                                            | 423                                                                                                                                                           | 473                                                                                                                          | 523                                                                                         | 573                                                        | 623                       |

| 1.00E+09 | T-void          | 1.55E+10 | IMMORT   | IMMORT   | IMMORT   | IMMORT   | IMMORT      | R <rcrit< td=""><td>IMMORT</td><td>IMMORT</td><td>IMMORT</td><td>IMMORT</td><td>IMMORT</td></rcrit<>                                                                                           | IMMORT                                                                                                                                                        | IMMORT                                                                                                                       | IMMORT                                                                                      | IMMORT                                                     | IMMORT                    |

| 2.00E+09 | T-void          | 6.98E+09 | 7.09E+08 | IMMORT   | IMMORT   | IMMORT   | IMMORT      | R <rcrit< td=""><td>R<rcrit< td=""><td>IMMORT</td><td>IMMORT</td><td>IMMORT</td><td>IMMORT</td></rcrit<></td></rcrit<>                                                                         | R <rcrit< td=""><td>IMMORT</td><td>IMMORT</td><td>IMMORT</td><td>IMMORT</td></rcrit<>                                                                         | IMMORT                                                                                                                       | IMMORT                                                                                      | IMMORT                                                     | IMMORT                    |

| 3.00E+09 | T-void          | 4.51E+09 | 3.52E+08 | 3.85E+07 | IMMORT   | IMMORT   | IMMORT      | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>IMMORT</td><td>IMMORT</td><td>IMMORT</td></rcrit<></td></rcrit<></td></rcrit<>                                                       | R <rcrit< td=""><td>R<rcrit< td=""><td>IMMORT</td><td>IMMORT</td><td>IMMORT</td></rcrit<></td></rcrit<>                                                       | R <rcrit< td=""><td>IMMORT</td><td>IMMORT</td><td>IMMORT</td></rcrit<>                                                       | IMMORT                                                                                      | IMMORT                                                     | IMMORT                    |

| 4.00E+09 | T-void          | 3.33E+09 | 2.38E+08 | 1.87E+07 | 4.16E+06 | IMMORT   | IMMORT      | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>IMMORT</td><td>IMMORT</td></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<>                                     | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>IMMORT</td><td>IMMORT</td></rcrit<></td></rcrit<></td></rcrit<>                                     | R <rcrit< td=""><td>R<rcrit< td=""><td>IMMORT</td><td>IMMORT</td></rcrit<></td></rcrit<>                                     | R <rcrit< td=""><td>IMMORT</td><td>IMMORT</td></rcrit<>                                     | IMMORT                                                     | IMMORT                    |

| 5.00E+09 | T-void          | 2.64E+09 | 1.80E+08 | 1.29E+07 | 1.63E+06 | IMMORT   | IMMORT      | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>IMMORT</td><td>IMMORT</td></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<>                                     | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>IMMORT</td><td>IMMORT</td></rcrit<></td></rcrit<></td></rcrit<>                                     | R <rcrit< td=""><td>R<rcrit< td=""><td>IMMORT</td><td>IMMORT</td></rcrit<></td></rcrit<>                                     | R <rcrit< td=""><td>IMMORT</td><td>IMMORT</td></rcrit<>                                     | IMMORT                                                     | IMMORT                    |

| 6.00E+09 | T-void          | 2.19E+09 | 1.45E+08 | 9.93E+06 | 1.13E+06 | 2.19E+05 | IMMORT      | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>IMMORT</td></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<>                   | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>IMMORT</td></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<>                   | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>IMMORT</td></rcrit<></td></rcrit<></td></rcrit<>                   | R <rcrit< td=""><td>R<rcrit< td=""><td>IMMORT</td></rcrit<></td></rcrit<>                   | R <rcrit< td=""><td>IMMORT</td></rcrit<>                   | IMMORT                    |

| 7.00E+09 | T-void          | 1.87E+09 | 1.22E+08 | 8.09E+06 | 8.76E+05 | 1.49E+05 | 3.98E+04    | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<> | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<> | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<> | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<></td></rcrit<> | R <rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<> | R <rcrit< td=""></rcrit<> |

| 8.00E+09 | T-void          | 1.63E+09 | 1.05E+08 | 6.84E+06 | 7.18E+05 | 1.16E+05 | 2.65E+04    | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<> | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<> | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<> | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<></td></rcrit<> | R <rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<> | R <rcrit< td=""></rcrit<> |

| 9.00E+09 | T-void          | 1.45E+09 | 9.21E+07 | 5.92E+06 | 6.10E+05 | 9.52E+04 | 2.06E+04    | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<> | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<> | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<> | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<></td></rcrit<> | R <rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<> | R <rcrit< td=""></rcrit<> |

| 1.00E+10 | T-void          | 1.30E+09 | 8.21E+07 | 5.22E+06 | 5.31E+05 | 8.11E+04 | 1.69E+04    | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<> | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<> | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<> | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<></td></rcrit<> | R <rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<> | R <rcrit< td=""></rcrit<> |

| 1.10E+10 | T-void          | 1.18E+09 | 7.40E+07 | 4.68E+06 | 4.70E+05 | 7.08E+04 | 1.45E+04    | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<> | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<> | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<> | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<></td></rcrit<> | R <rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<> | R <rcrit< td=""></rcrit<> |

| 1.20E+10 | T-void          | 1.08E+09 | 6.74E+07 | 4.23E+06 | 4.22E+05 | 6.29E+04 | 1.27E+04    | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<> | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<> | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<></td></rcrit<></td></rcrit<> | R <rcrit< td=""><td>R<rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<></td></rcrit<> | R <rcrit< td=""><td>R<rcrit< td=""></rcrit<></td></rcrit<> | R <rcrit< td=""></rcrit<> |

| 3.00E+10 | T-void          | 4.28E+08 | 2.59E+07 | 1.57E+06 | 1.49E+05 | 2.11E+04 | 4.00E+03    | 9.09E+09                                                                                                                                                                                       | 1.19E+08                                                                                                                                                      | 3.93E+06                                                                                                                     | 2.53E+05                                                                                    | 2.66E+04                                                   | 4.01E+03                  |

| 5.00E+10 | T-void          | 2.56E+08 | 1.54E+07 | 9.21E+05 | 8.71E+04 | 1.22E+04 | 2.29E+03    | 4.81E+09                                                                                                                                                                                       | 6.27E+07                                                                                                                                                      | 2.08E+06                                                                                                                     | 1.34E+05                                                                                    | 1.41E+04                                                   | 2.12E+03                  |

| 7.00E+10 | T-void          | 1.83E+08 | 1.09E+07 | 6.53E+05 | 6.15E+04 | 8.57E+03 | 1.60E+03    | 3.28E+09                                                                                                                                                                                       | 4.27E+07                                                                                                                                                      | 1.42E+06                                                                                                                     | 9.14E+04                                                                                    | 9.60E+03                                                   | 1.44E+03                  |

| 9.00E+10 | T-void          | 1.42E+08 | 8.48E+06 | 5.05E+05 | 4.75E+04 | 6.61E+03 | 1.23E+03    | 2.49E+09                                                                                                                                                                                       | 3.24E+07                                                                                                                                                      | 1.08E+06                                                                                                                     | 6.93E+04                                                                                    | 7.29E+03                                                   | 1.10E+03                  |

$\sigma_{\scriptscriptstyle rit}$

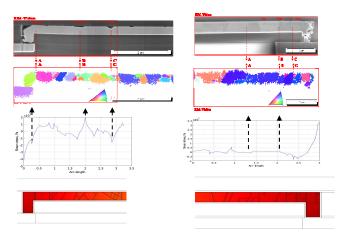

Extraction of the current density exponent, (a), and the apparent activation energy, (b), based on the calculated  $t_{nuc}$ .

Extracted dependencies of *n* on  $T_{test}$  (a), and  $E_a$  on *j* (b) for Sim. 1 ( $T_{ZS}$ =653 K,  $s_{crit}$ =500MPa) and Sim. 2 ( $T_{ZS}$ =723 K,  $s_{crit}$ =600MPa) vs. experimental data.

> © 2010 Mentor Graphics Corp. www.mentor.com

jL

FCMN2015, Dresden

### **EM-induced supply voltage degradation**

### **EM Assessment Results in IBM Benchmarks**

Current source values are modified to ensure initial IR drop of any node is smaller than the threshold value

#### USING BLACK'S EQUATION AND PROPOSED MODEL Time to Failure (yrs) CPU time Power Grid Black's Equation Proposed of Our Name Nodes Series Mesh model Method IBMPG2 61797 7.82 10.67 15.66 54.66min. IBMPG3 19.95 19.61hr. 407279 15.77 27.61 **IBMPG4** 474836 12.58 23.68 29.20 19.93hr. 23.05 54.87min. IBMPG5 497658 6.34 11.1 IBMPG6 807825 9.53 13.97 17.80 32.52hr. **IBMPGNEW1** 17.50 22.48 6.89hr. 715022 13.64 IBMPGNEW2 715022 12.44 18.77 20.12 5.99hr.

TABLE: COMPARISON OF POWER GRID MTTF

Both Black's equation based series and Mesh models  $\diamond$ lead to pessimistic predictions

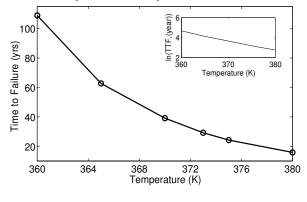

- EM effect is sensitive to temperature  $\diamond$

- TTF exponentially relates to temperature (the same as Black's equation)

- Initial voltage drop final voltage drop (a) Voltage drop (V) distribution and (b) Initial steady state EM hydrostatic stress (Pa)distribution predicted by initial current density in IBMPG2 largest voltage drop 0.14 first failed node 0.12

- In this work, the first failure is most likely to happen at  $\diamond$ the nodes where the initial hydrostatic stress is large

Voltage at the first failed node over time

© 2010 Mentor Graphics Corp. www.mentor.com

X. Huang, T. Yu, V. Sukharev, and S. X.-D. Tan, "Physics-based

electromigration assessment for power grid networks," in Design

Automation Conference (DAC), 2014, 51th ACM/EDAC/IEEE, 2014.

FCMN2015, Dresden

$\diamond$

### EXAMPLE OF IR-DROP EM ASSESSMENT

CHIP-SCALE EM ASSESSMENT CONSIDERING THE IMPACT OF TEMPERATURE AND CPI STRESS VARIATIONS

FCMN2015, Dresder

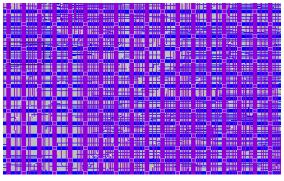

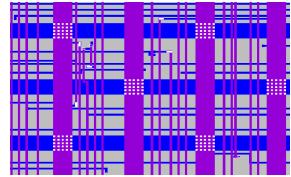

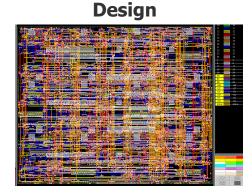

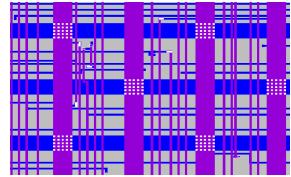

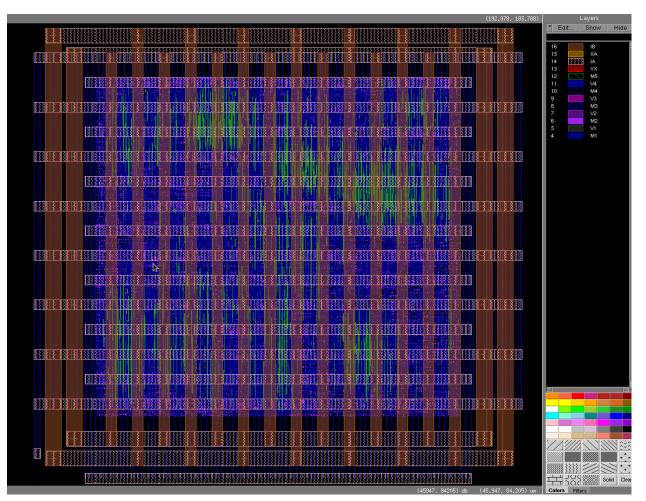

### Layout

- Design:

- 7-metal layer

- 32nm

- Dimension:184um × 184um

| Layer<br>number | Name        |

|-----------------|-------------|

| 3               | Contact     |

| 4               | M1          |

| 5               | V1          |

| 6               | M2          |

| 7               | V2          |

| 8               | M3          |

| 9               | V3          |

| 10              | M4          |

| 11              | V4          |

| 12              | M5          |

| 13              | YX(V5)      |

| 14              | IA(M6 wide) |

| 15              | XA(V6)      |

| 16              | IB(M7 wide) |

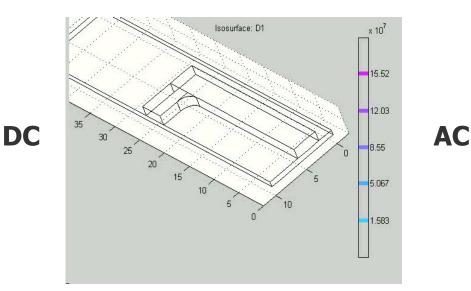

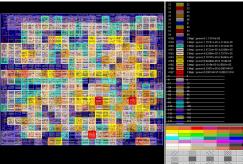

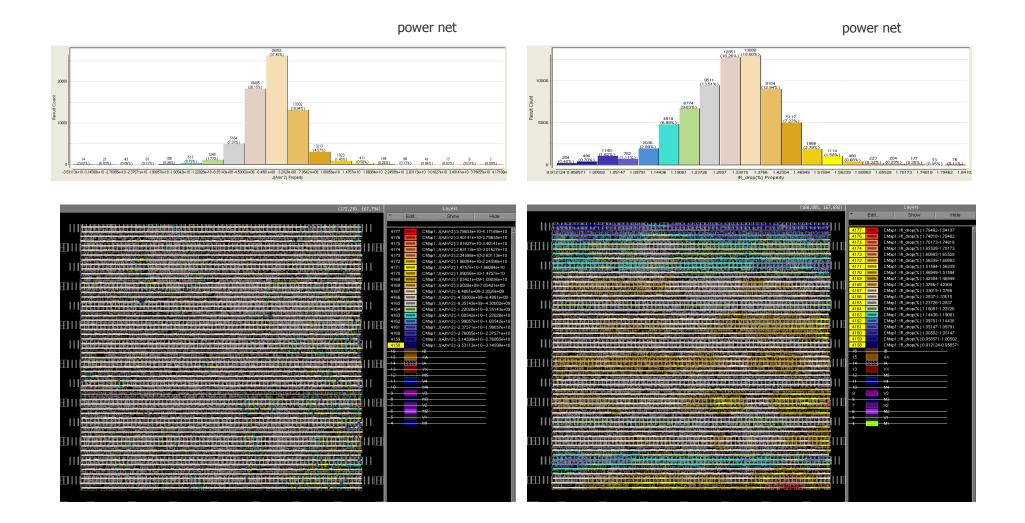

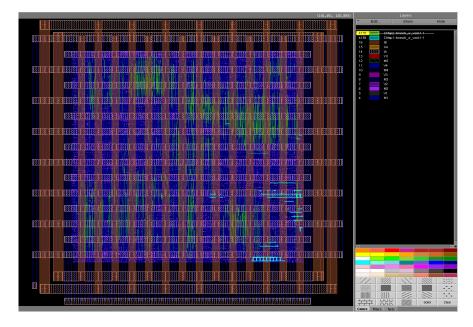

### **Initial current density and initial IR-drop**

-power net, M1 layer

### **Temperature distribution**

M. Chew, A. Aslyan, J.-H. Choy, X. Huang, "Accurate Full-Chip Estimation of Power Map, Current Densities and Temperature for EM Assessment", in *Computer-Aided Design (ICCAD), 2014 IEEE/ACM International Conference on*, pp. 440–445, 2014. FCMN2015, Dresden

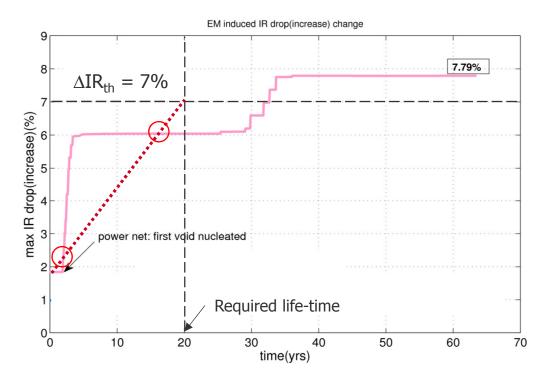

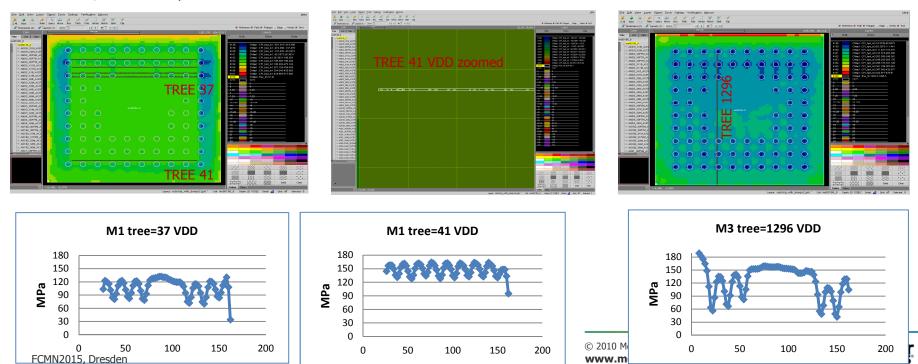

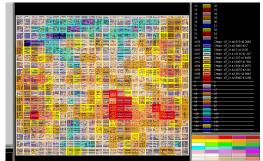

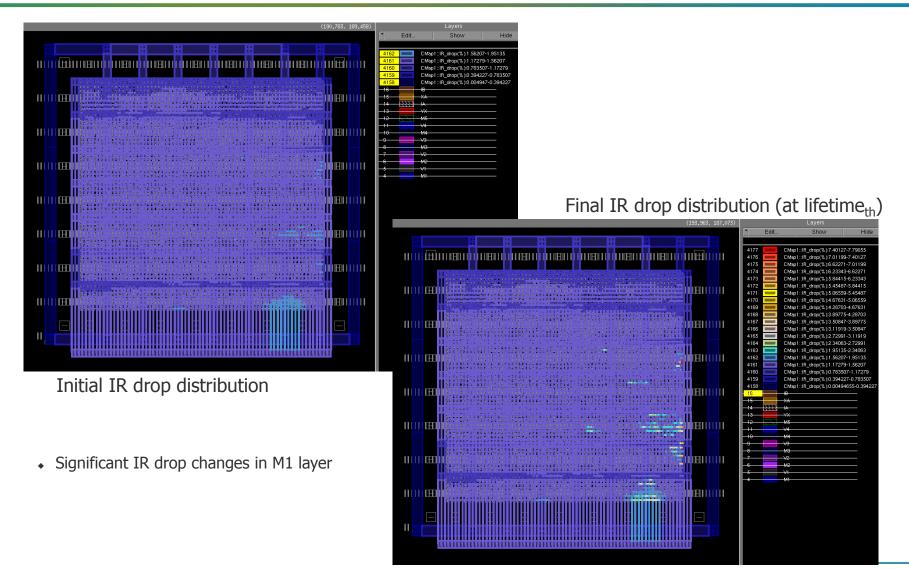

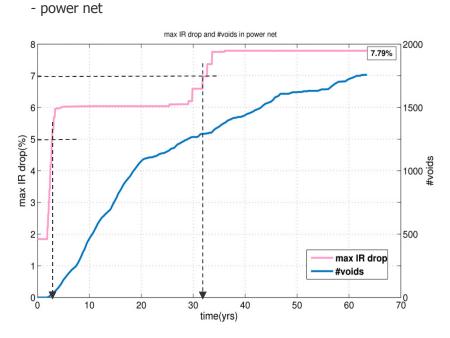

### **EM induced IR drop change**

- power net

© 2010 Mentor Graphics Corp. www.mentor.com

FCMN2015, Dresden

### **EM induced IR drop change**

- power net

#### **Branches with voids**

- power net

Voids mainly locate in M1 layer, some voids locate in M3 layer

#### **EM induced IR drop change**

Chip fails when the maximum IR drop > threshold level

### **CALIBRATION/VALIDATION**

### How to calibrate/validate verification tools?

- Both types of tools predicting the effect of CPI on chip performance and chip reliability need as inputs:

- Measured foundry and process dependent thermal-mechanical properties of the involved materials.

- Calibrated compact models employed for calculation of the stresses and temperature across a device layer and across the whole chip.

- Calibrated models for calculating effective thermal-mechanical properties of all composite layers (BEoL and RDL interconnects, underfill with C4 and u-bumps, silicon bulk with TSVs, etc.).

- Both types of tools need to be validated by a direct comparison between the predicted characteristics and measured:

- Comparing the measured characteristics of individual transistors and predicted by verification tools is a validation of the CPI effect on chip performance.

- What kind of test-structures should be used to validate the effect of CPI on chip reliability (EM as an example)?

# **Calibration of the models for effective thermal-mechanical properties**

- New approach to determine CTE for Cu/ULK for a partially de-processed 3DIC, by combination of FIB cutting and SEM (heating stage holder).

- isolate a bar

- separate into two bars of same length, and measure the gap in the middle as a function of temperature up to 250° C

- □ Layout file (GDSII & Oasis) allows to calculate all three components of the effective CTE for different bin sizes.

- □ Following FEA simulation could allow to calibrate the effective CTE model.

- Similar approach can be employed for calibration of the models for effective Young's modulus and Poisson factor.

- There is a need in experimental methodology for calibrating the models for thermal properties of on-chip interconnects and other composite layers.

R. Radojcic, E. Zschech, V. Sukharev, "Managing the Effects of Mechanical Stress on Performance of Modern SoCS", iMAPS 2013, Hand-out for Tutorial T7.

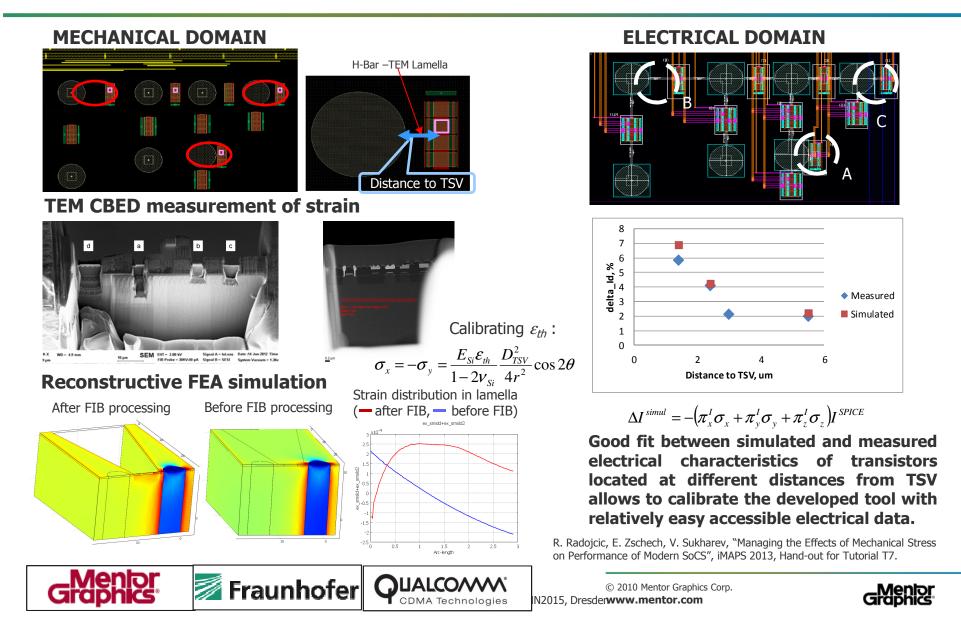

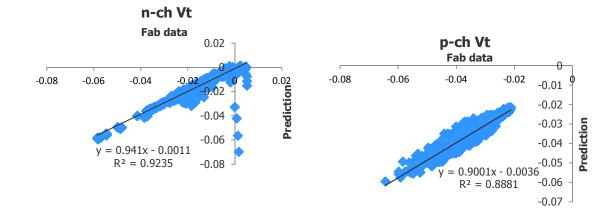

### **Proof Electrical vs. Mechanical**

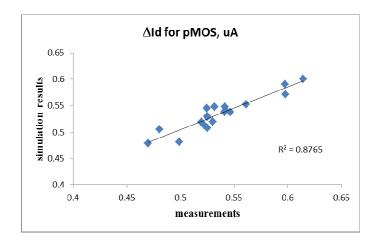

### Validation with the Foundry calibrated Model

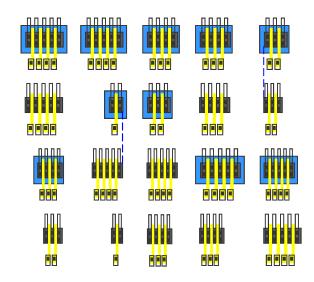

#### Calibration was performed on ~100 gates Prediction was made for all (~4000) gates

#### Test-chip segment

V. Sukharev et al., "Multi-scale simulation methodology for stress assessment in 3D IC: effect of die stacking on device performance," J. Electron. Test. 28(1), 63–72 (2012).

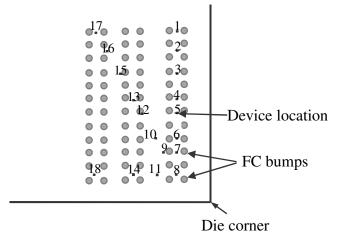

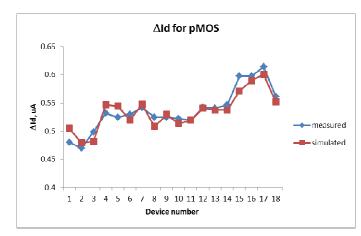

### Die Corner Array: Test-chip 28nm node

Schematics of the test structures used for model calibration: die corner

R. Radojcic, E. Zschech, V. Sukharev, "Managing the Effects of Mechanical Stress on Performance of Modern SoCS", iMAPS 2013, Hand-out for Tutorial T7.

- How can we validate the predicted stress distribution inside the interconnect metal of the die stacked by 3D IC technology?

- How can we validate the distribution of the EM- or SM-induced voids inside BEoL interconnect?

- How can we monitor the accelerated kinetics of IRdrop degradation? What kind of test-structures should be developed?

- Test-chips with the temperature sensors?

- Itc., etc.

### CONCLUSIONS

A NOVEL METHODOLOGY FOR FULL-CHIP POWER/GROUND NETS REDUNDANCY-AWARE EM ASSESSMENT BASED ON IR-DROP ANALYSIS WAS DEVELOPED.

PHYSICS-BASED MODEL FOR TEMPERATURE- AND RESIDUAL STRESS-AWARE VOID NUCLEATION AND GROWTH WAS DEVELOPED AND IMPLEMENTED IN THE FLOW.

A DEVELOPED TECHNIQUE FOR CALCULATING THE HYDROSTATIC STRESS DISTRIBUTION INSIDE A MULTI BRANCH INTERCONNECT TREE ALLOWS TO AVOID OVER OPTIMISTIC PREDICTION OF THE TIME TO FAILURE MADE WITH THE BLECH-BLACK ANALYSIS OF INDIVIDUAL BRANCHES OF INTERCONNECT SEGMENT.