2005 International Conference on Characterization and Metrology for ULSI Technology Dallas, TX March 15, 2005

#### MOSFET Scaling Trends, Challenges, and Potential Solutions Through the End of the Roadmap: A 2005 Perspective

Peter M. Zeitzoff Howard R. Huff

Accelerating the next technology revolution.

### Outline

#### > Introduction

- MOSFET scaling and its impact

- Front-end approaches and solutions

- Non-classical CMOS

- Summary

#### Introduction

- IC Logic technology: following Moore's Law by rapidly scaling into deep submicron regime

- Increased speed and function density

- Lower power dissipation and cost per function

- But the scaling results in major MOSFET and process integration issues, including

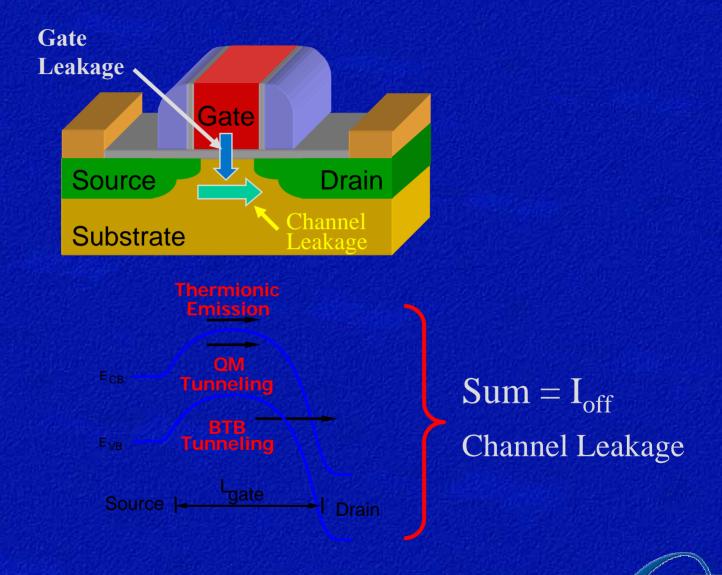

- Simultaneously maintaining satisfactory I<sub>on</sub> (drive current) and I<sub>leak</sub>

- High gate leakage current for very thin gate dielectrics

- Control of short channel effects for very small transistors

- Etc.

- Potential solutions & approaches

- Material and process (front end): high-k gate dielectric, metal gate electrodes, strained Si, ...

- Structural: non-classical CMOS device structures

- This talk gives an updated perspective from the 2003 International Technology Roadmap for Semiconductors (ITRS)

Accelerating the next technology revolution.

# **Metrology and Characterization Issues**

- Dimensional scaling: meeting metrology requirements for accuracy and precision becomes increasingly challenging

- Example: electrical and physical measurement of Tox < 1.2 nm</li>

- Another example: CD measurement

- Line edge (and width) roughness is increasingly critical

Potential solutions (high-k, metal gate electrodes, strained Si, non-classical CMOS) raise significant metrology and characterization challenges

#### Key Overall Chip Parameters for High-Performance Logic, from 2003 ITRS

| Year of<br>Production<br>MPU<br>Physical<br>Gate<br>Length<br>(nm)<br>On-chip<br>local clock | 2003<br>45<br>2,976 | 37  |     | 28  | 25  | 2008<br>22<br>10,972 | 2009<br>20<br>12,369 | 2010<br>18<br>15,079 | 14    | 13    | 2015<br>10<br>33,403 | 2016<br>9<br>39,683 | 2018<br>7<br>53,207 |

|----------------------------------------------------------------------------------------------|---------------------|-----|-----|-----|-----|----------------------|----------------------|----------------------|-------|-------|----------------------|---------------------|---------------------|

| Allowable<br>Maximum<br>Power                                                                |                     |     |     |     |     |                      |                      |                      |       |       |                      |                     |                     |

| High-<br>performance<br>with heatsink<br>(W)                                                 | 149                 | 158 | 167 | 180 | 189 | 200                  | 210                  | 218                  | 240   | 251   | 270                  | 288                 | 300                 |

| Cost-<br>performance<br>(W)                                                                  | 80                  | 84  | 91  | 98  | 104 | 109                  | 114                  | 120                  | 131   | 138   | 148                  | 158                 | 168                 |

| Functions<br>per chip at<br>production<br>(million<br>transistors<br>[Mtransisto<br>rs])     | 153                 | 193 | 243 | 307 | 386 | 487                  | 614                  | 773                  | 1,227 | 1,546 | 2,454                | 3,092               | 4,908               |

- -Rapid scaling of L<sub>g</sub> is driven by need to improve transistor speed

- Clock frequency, functions per chip (density) scale rapidly, but allowable power dissipation rises slowly with scaling

Accelerating the next ischnology revolution.

### Outline

#### Introduction

#### > MOSFET scaling and its impact

- Front-end approaches and solutions

- Non-classical CMOS

- Summary

# **Device Scaling Approach: 2003 ITRS**

- Simple models capturing essential MOSFET physics

→ embedded in a spreadsheet

- Room T, nominal devices assumed

- Key parameters include: L<sub>g</sub>, T<sub>ox</sub>, V<sub>dd</sub>, V<sub>t</sub>, series parasitic resistance, drive current, leakage current, gate capacitance, subthreshold slope, etc.

- Using spreadsheet, MOSFET parameters are iteratively varied to meet ITRS targets for either

Scaling of transistor speed OR

Scaling for specific, low levels of leakage current

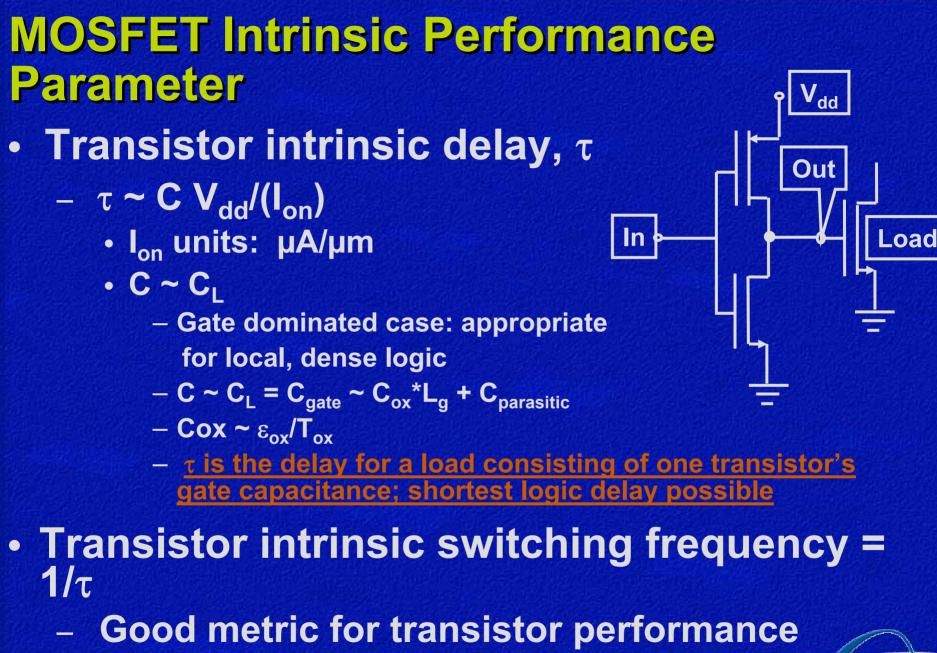

<u>To maximize 1/τ, maximize I<sub>or</sub></u>

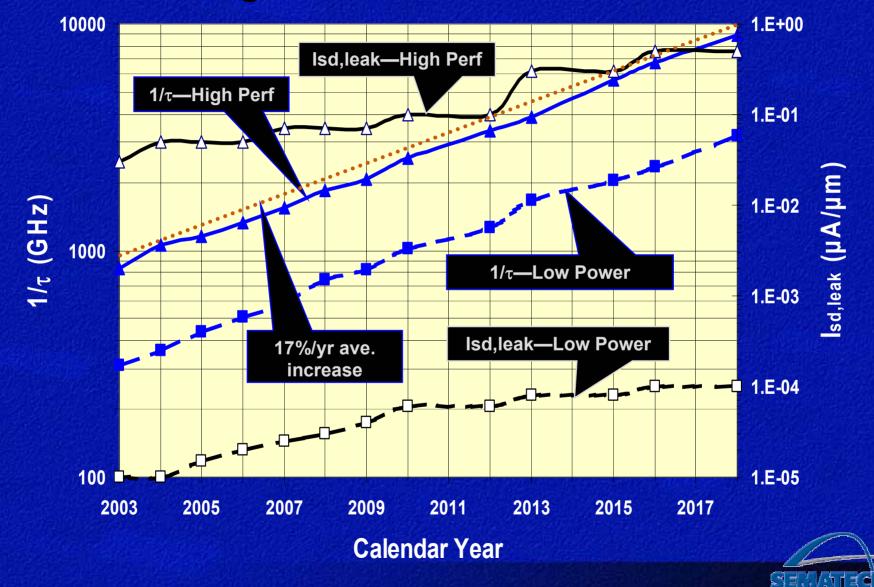

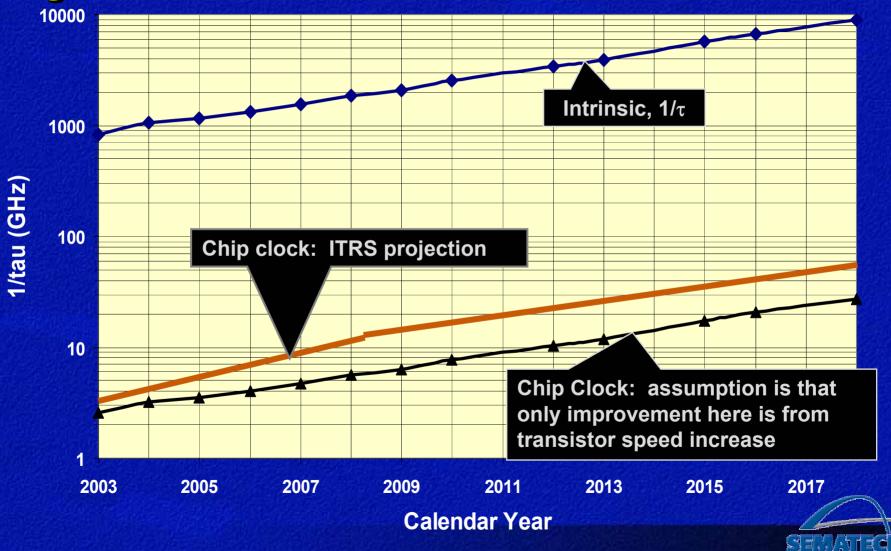

#### Different Applications -> Different ITRS Drivers

- High-performance chips (MPU, for example)

- Driver: maximize chip speed → maximize transistor performance

- Goal of ITRS scaling: 1/τ increases at ~ 17% per year, historical rate

- Must maximize I<sub>on</sub>

- Consequently, I<sub>leak</sub> is relatively high

- Low-power chips (mobile applications)

- Driver: minimize chip power (to maximize battery life) → minimize I<sub>leak</sub>

- Goal of ITRS scaling: specific, low level of I<sub>leak</sub>

- Consequently,  $1/\tau$  is considerably less than for high-performance logic

# 1/τ and Isd,leak scaling for High-Performance and Low-Power Logic. Data from 2003 ITRS.

Accelerating the next technology resolution.

### Outline

- Introduction

- MOSFET scaling and its impact

- > Front-end material and processing approaches and solutions

- Non-classical CMOS

- Summary

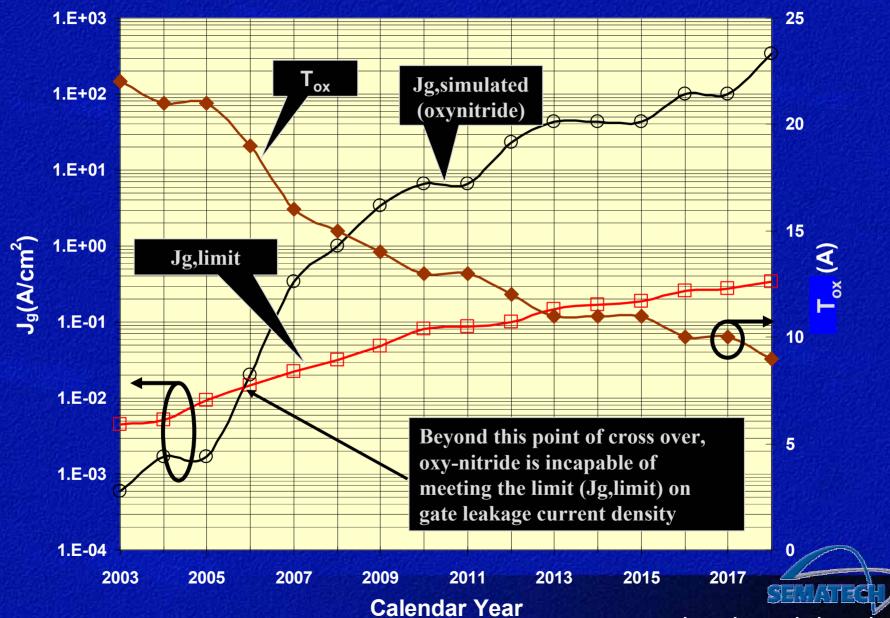

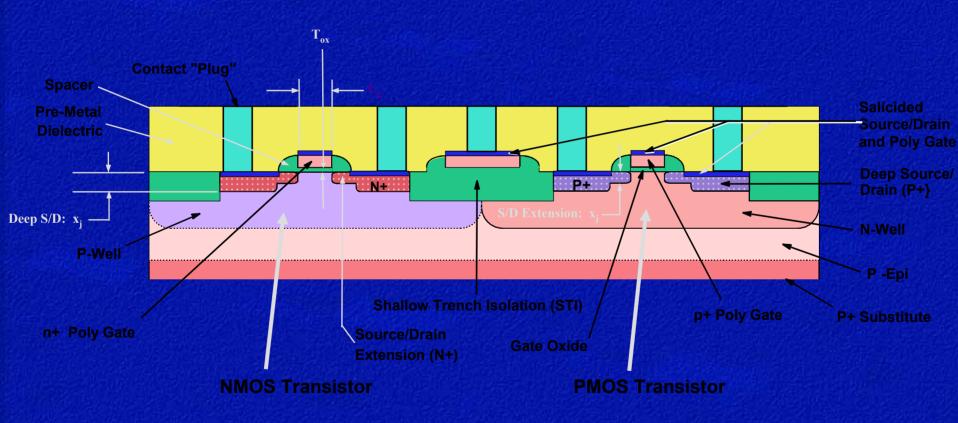

#### **Difficult Transistor Scaling Issues**

- Previously discussed scaling results involve determining the required transistor characteristics and performance to meet key scaling targets

- Assumption: highly scaled MOSFETs with required characteristics can be successfully fabricated

- With scaling, increasing difficulty in meeting transistor requirements without significant technology innovations

- High gate leakage

- Direct tunneling increases rapidly as  $T_{ox}$  is reduced

- Potential solution: high-k gate dielectric

- Polysilicon depletion in gate electrode → increased effective  $T_{ox}$ , reduced  $I_{on}$

- Need for enhanced channel mobility

- Etc.

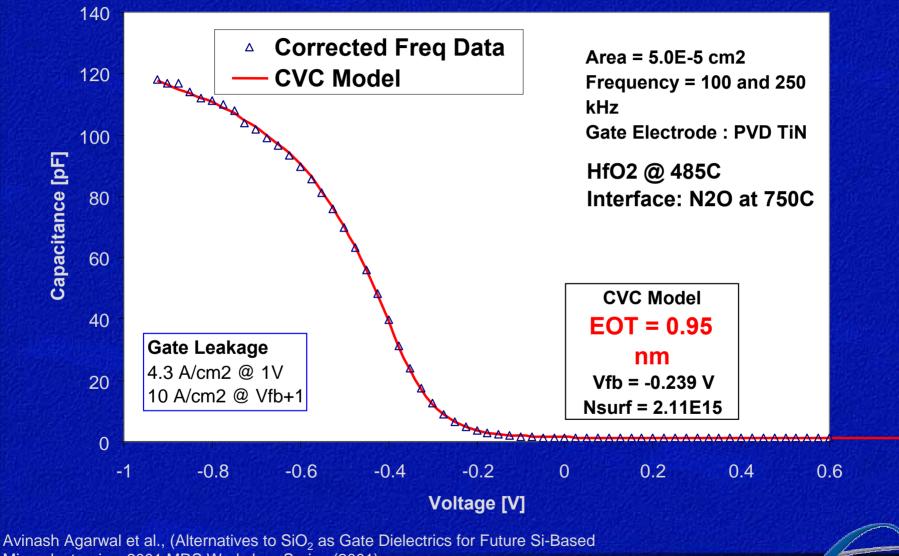

For Low-Power Logic, Gate Leakage Current Density Limit Versus Simulated Gate Leakage due to Direct Tunneling. Data from 2003 ITRS.

Asselerating the next technology revolution.

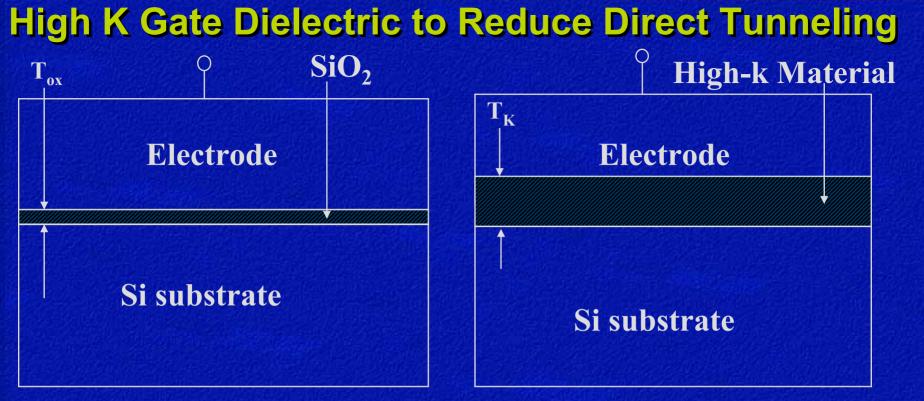

- Equivalent Oxide Thickness = EOT =  $T_{ex} = T_{K} * (3.9/K)$ , where 3.9 is relative dielectric constant of SiO<sub>2</sub> and K is relative dielectric constant of high K material

- $C = Cox = \varepsilon_{ox}/T_{ox}$

- To first order, MOSFET characteristics with high-k are same as for SiO2

- Because  $T_K > T_{ox}$ , direct tunneling leakage much reduced with high K

- If energy barrier is high enough

- Candidate materials: LaO<sub>2</sub>/HfO<sub>2</sub>/ZrO<sub>2</sub>(K~15 30); Hf, Zr-SiO<sub>4</sub> (K~12 16); others

- Major materials, process, integration issues to solve

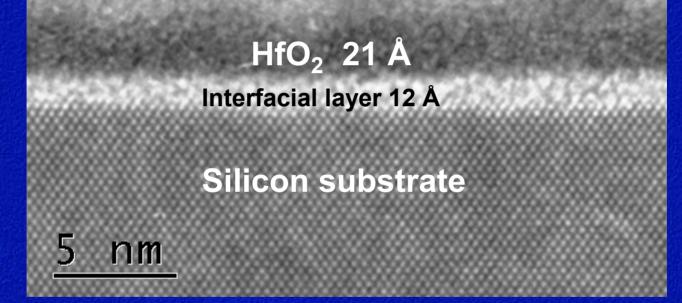

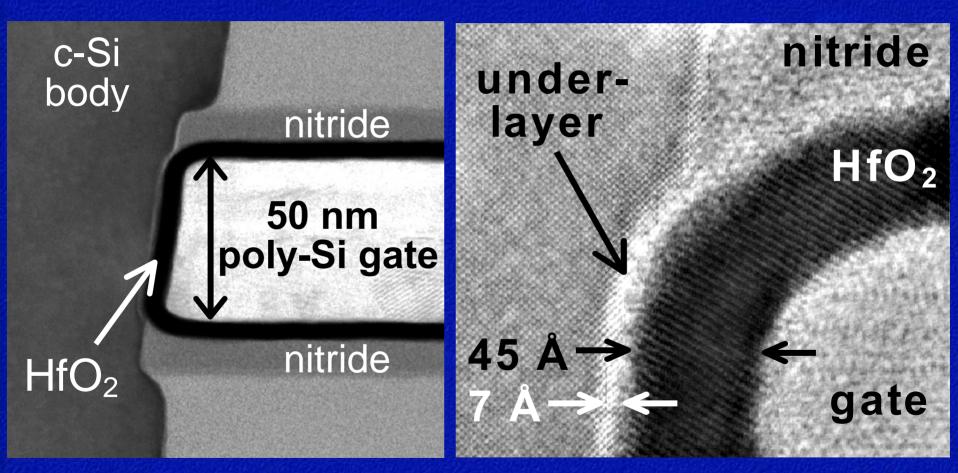

#### MOCVD HfO2 TEM (EOT = 0.95 nm) (HfO2 on HF-last, N2O-750°C Pre-Deposition Anneal)

• Effective k for above dielectric stack  $\approx$  13.5

k for interfacial layer could be significantly greater than SiO<sub>2</sub> indicating reaction or intermixing of HfO<sub>2</sub> film with interfacial SiO<sub>2</sub>

Avinash Agarwal et al., Alternatives to SiO<sub>2</sub> as Gate Dielectrics for Future Si-Based Microelectronics, 2001 MRS Workshop Series (2001) p.16

Accelerating the next technology revolution.

### **Difficult Transistor Scaling Issues**

- With scaling, increasing difficulty in meeting transistor requirements without significant technology innovations

- High gate leakage

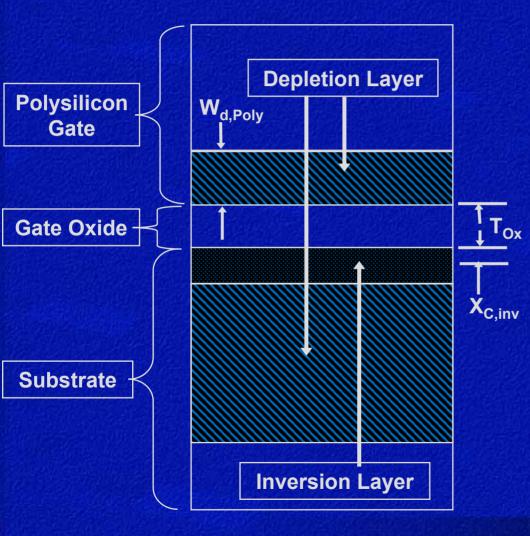

- Direct tunneling increases rapidly as T<sub>ox</sub> is reduced

- Polysilicon depletion in gate electrode → increased effective electrical T<sub>ox</sub>, reduced I<sub>on</sub>

- Potential solution: metal gate electrodes

- Need for enhanced channel mobility

- Etc.

# Polysilicon Depletion and SubstrateQuantum Effects•Tox,electric = Tox + (Kox/Ksi)\*

(W<sub>d,Polv</sub>+X<sub>C,inv</sub>)  $-K_{ox} = 3.9$  $-K_{ei} = 11.9$ • $T_{ox,electric} = T_{ox} + (0.33)^* (W_{d,Poly})$ +X<sub>C,inv</sub>) -W<sub>d,Poly</sub>~1/(poly doping)<sup>0.5</sup> →increase poly doping to reduce W<sub>d.Poly</sub> with scaling -But max. poly doping is limited→can't reduce W<sub>d.Polv</sub> too much -Fermi Level pinning with highk •Poly depletion and X<sub>C.inv</sub> become more critical with Tox scaling -Eventually, poly will reach its limit of effectiveness

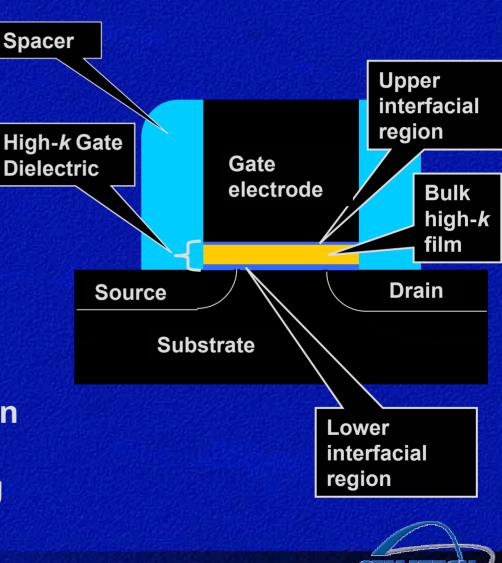

## **Metal Gate Electrodes**

- Metal gate electrodes are a potential solution when poly "runs out of steam": probably implemented at 65 nm tech. generation (2007) or beyond

- No depletion, very low resistance gate, no boron penetration, compatibility with high-k

- Issues

- Different work functions needed for PMOS and NMOS==>2 different metals may be needed

- Process complexity, process integration problems, cost

- Etching of metal electrodes

- New materials: major challenge

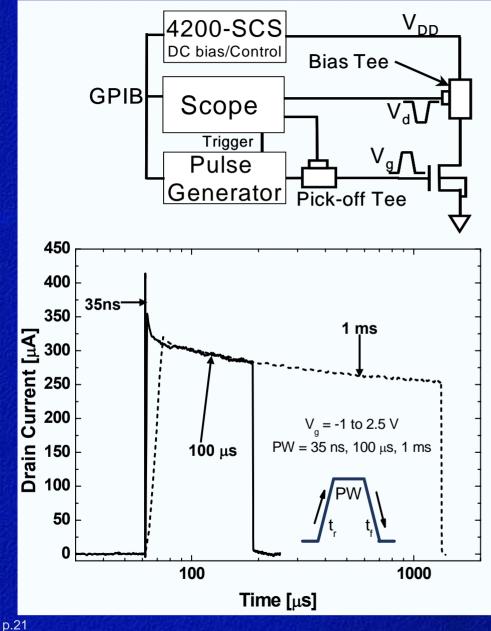

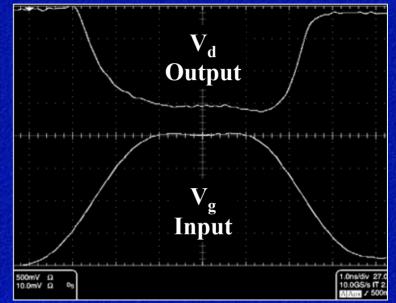

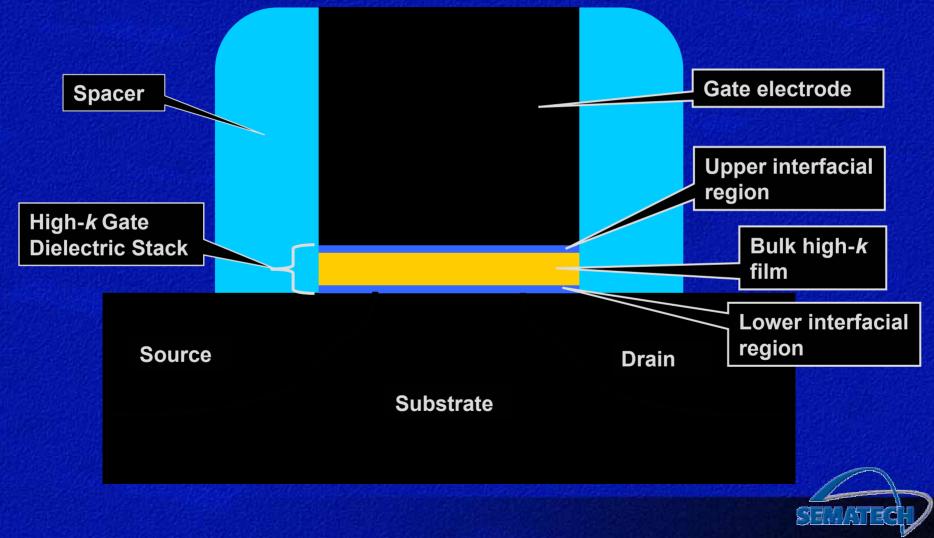

### Advanced Gate Stack: Key Metrology and Characterization Challenges

- Transient charge trapping

in high-k bulk

- Characterizing charge trapping

- Extracting mobility: μ<sub>eff</sub>=(LI<sub>d</sub>)/(WQ<sub>inv</sub>V<sub>d</sub>)

- Determining V<sub>t</sub>, V<sub>FB</sub> from C-V

- Fast pulse measurements help

- Charge in high-k & Interaction between metal gate and high-k: unambiguous determination of  $\phi_m$

- Gate leakage → determining EOT from C-V

Accelerations the next technology rest

# Example: Fast Transient Electron Trapping with Pulse Measurements on High-k Gate Dielectric

Significant trapping occurs within few µsec

C. Young, SSDM 2004

Accelerating the next technology revolution

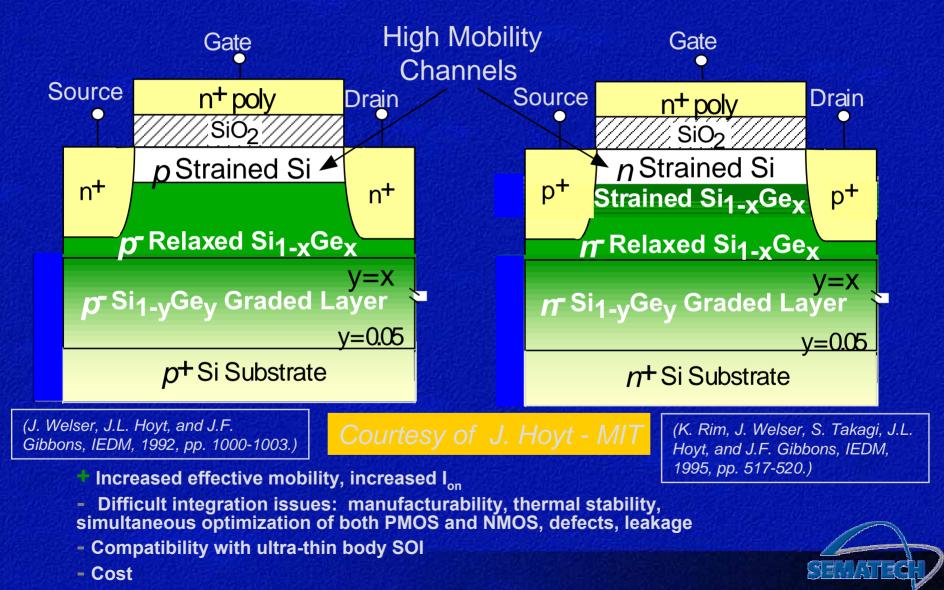

#### **Difficult Transistor Scaling Issues**

- With scaling, increasing difficulty in meeting transistor requirements

- High gate leakage

- Direct tunneling increases rapidly as  $T_{\text{ox}}$  is reduced

- Polysilicon depletion in gate electrode → increased effective  $T_{ox}$ , reduced  $I_{on}$

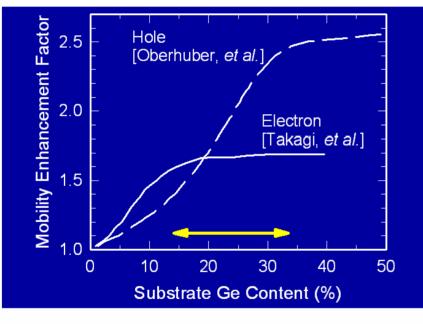

- Need for enhanced channel mobility

- Potential solution: strained Si channels

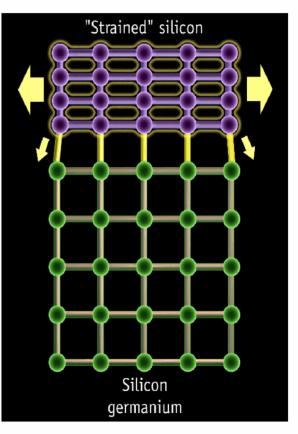

#### Band Engineered MOSFETs: Strained MOSFET Structures

Accelerating the next technology resolution.

#### **Strained Si Device Structures**

Courtesy of Patricia Mooney (IBM Corp.) From P. M. Mooney et al., presented at the American Physics Society Meeting, Austin, TX, March 3-7, 2003.

modified band structure of Si under biaxial tensile strain ==> enhanced mobility

need relaxed  $Si_{1-x}Ge_x$  with 0.15<x<0.35

Strained Si on SiGe

Accelerating the next technology revolution.

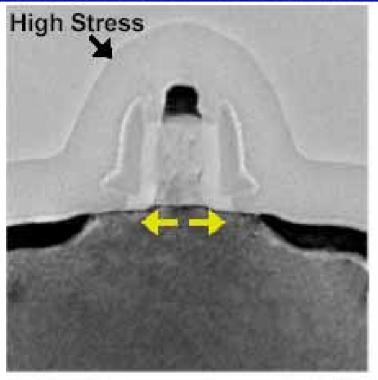

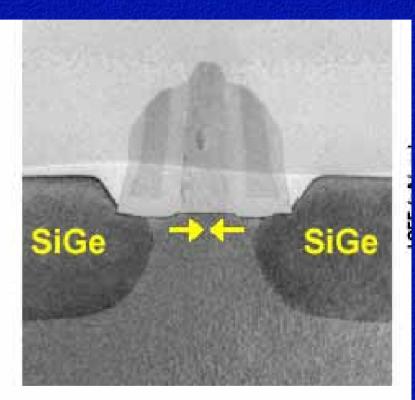

#### Alternate Approach: Uniaxial Process Induced Stress

NMOS: uniaxial tensile stress from stressed SiN film

Fig. 3 TEM of NMOS transistor showing high tensile stress nitride overlayer. PMOS: uniaxial compressive stress from sel. SiGe in S/D

Fig. 4 TEM of PMOS showing SiGe heteroepitaxial S/D inducing uniaxial strain.

From K. Mistry et al., "Delaying Forever: Uniaxial Strained Silicon Transistors in a 90nm CMOS Technology," 2004 VLSI Technology Symposium, pp. 50-51.

p.25

# **Strained Si: Metrology and Characterization Challenges**

- Measuring strain distribution with high spatial resolution in deep sub-micron structures

- Possible approaches

- X-ray diffraction (XRD)

- Raman spectroscopy

- Convergence Beam Electron Diffraction (CBED)

- Electron Diffraction Contrast (EDC)

### Outline

- Introduction

- Scaling and its impact

- Front end approaches and solutions

- > Non-classical CMOS

- Summary

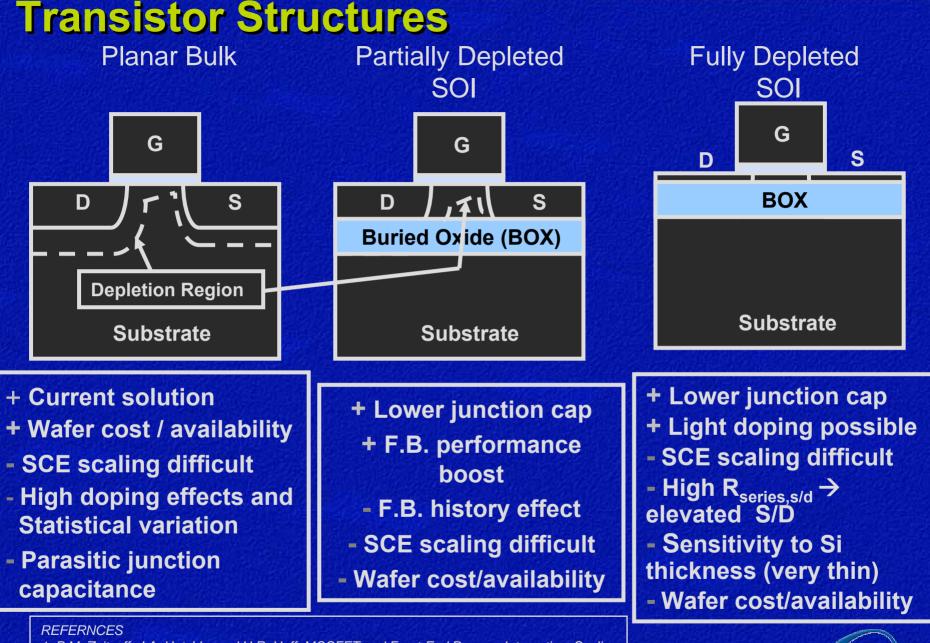

## Limits of Scaling Planar, Bulk MOSFETs

- 65 nm tech. generation (2007,  $L_g = 25nm$ ) and beyond: increased difficulty in meeting all device requirements with classical planar, bulk CMOS (even with material and process solutions: high K, metal electrodes, ....)

- Control of SCE

- Impact of quantum effects and statistical variation

- Impact of high substrate doping

- Control of series S/D resistance (R<sub>series.s/d</sub>)

- Others

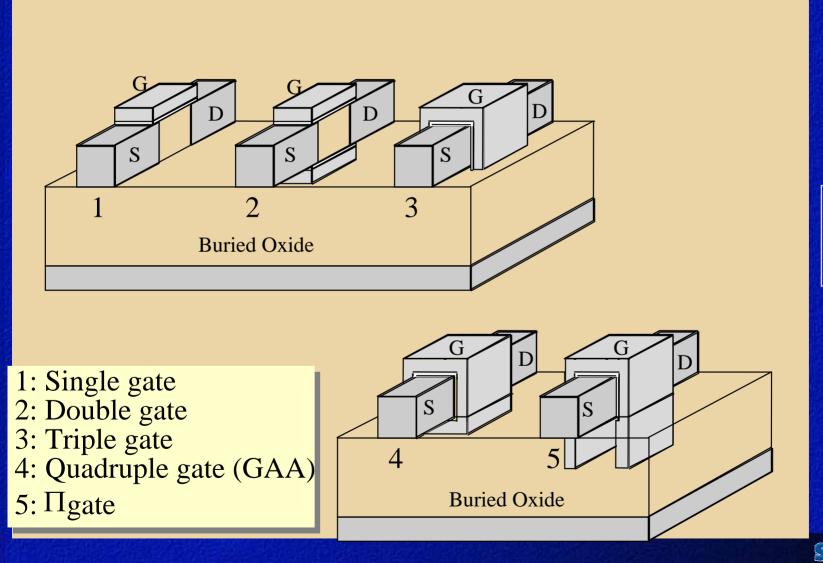

Alternative device structures (<u>non-classical CMOS</u>) may be utilized

Ultra thin body, fully depleted: single-gate SOI and multiple-gate transistors

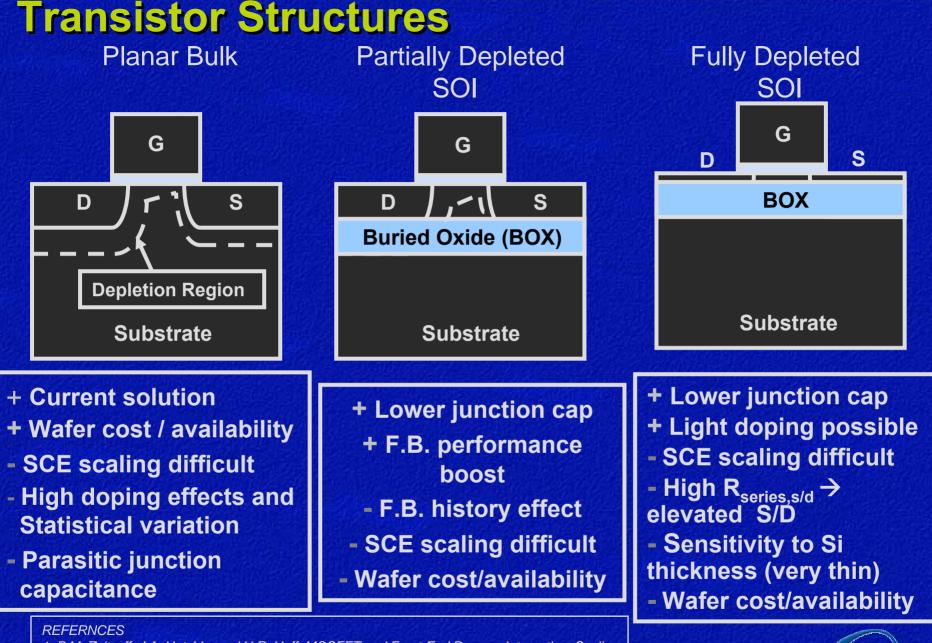

#### **Transistor Structures**

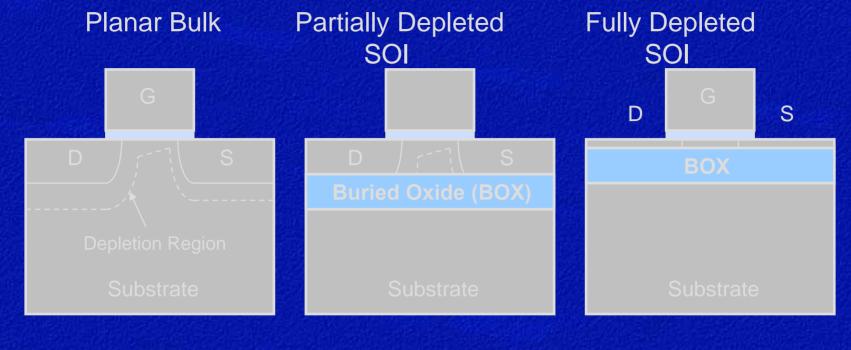

#### Planar Bulk **Partially Depleted** SOI G G D S D **Buried Oxide (BOX) Depletion Region Substrate Substrate** + Current solution + Lower junction cap + Wafer cost / availability + F.B. performance - SCE scaling difficult boost - High doping effects and - F.B. history effect **Statistical variation** - SCE scaling difficult - Parasitic junction - Wafer cost/availability capacitance

#### REFERNCES

1. P.M. Zeitzoff, J.A. Hutchby and H.R. Huff, MOSFET and Front-End Process Integration: Scaling Trends, Challenges, and Potential Solutions Through The End of The Roadmap, International Journal of High-Speed Electronics and Systems, 12, 267-293 (2002). 2. Mark Bohr, ECS Meeting PV 2001-2, Spring, 2001.

Accelerating the next technology rate

S

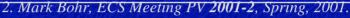

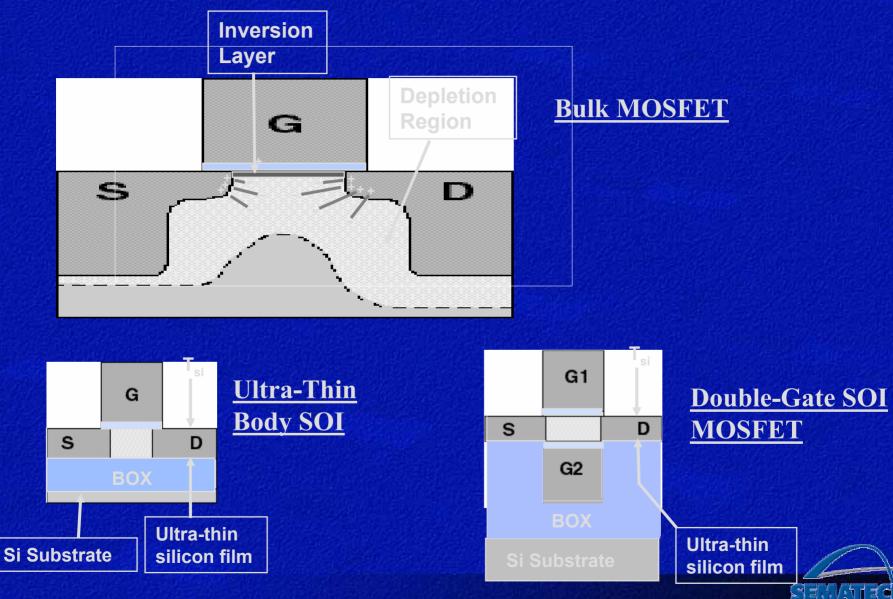

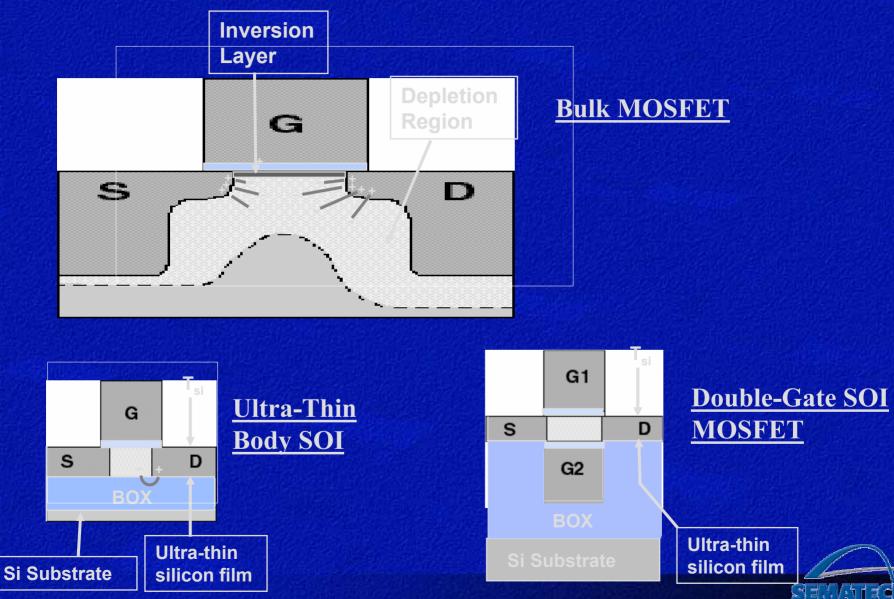

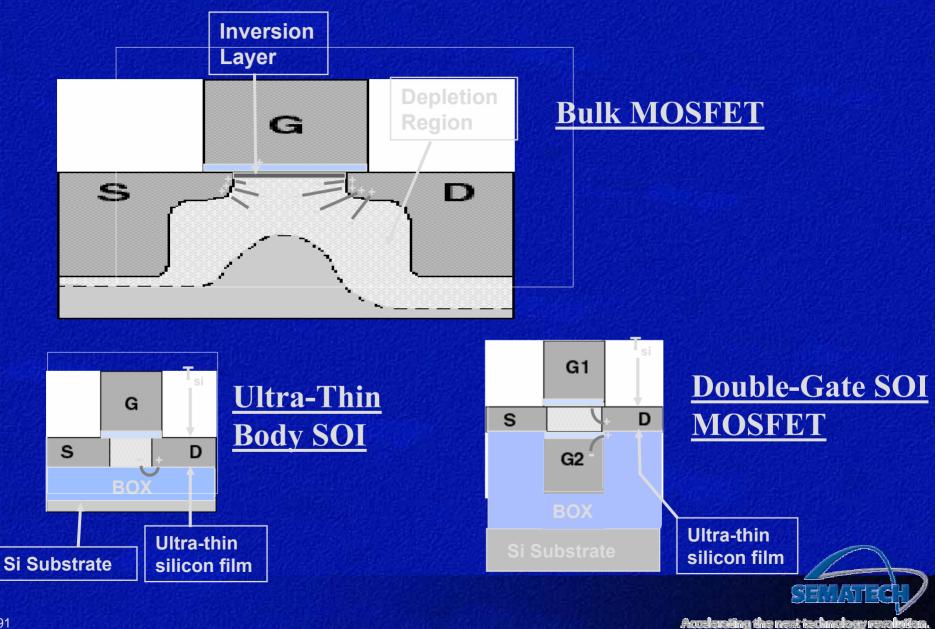

# Schematic cross section of planar bulk, UTB SOI, and DG SOI MOSFET

Inversion Layer

#### **Bulk MOSFET**

1. P.M. Zeitzoff, J.A. Hutchby and H.R. Huff, MOSFET and Front-End Process Integration: Scaling Trends, Challenges, and Potential Solutions Through The End of The Roadmap, International Journal of High-Speed Electronics and Systems, **12**, 267-293 (2002).

2. Mark Bohr, ECS Meeting PV 2001-2, Spring, 2001.

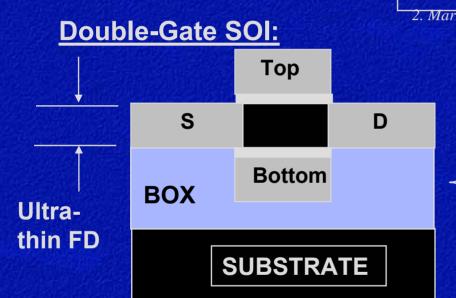

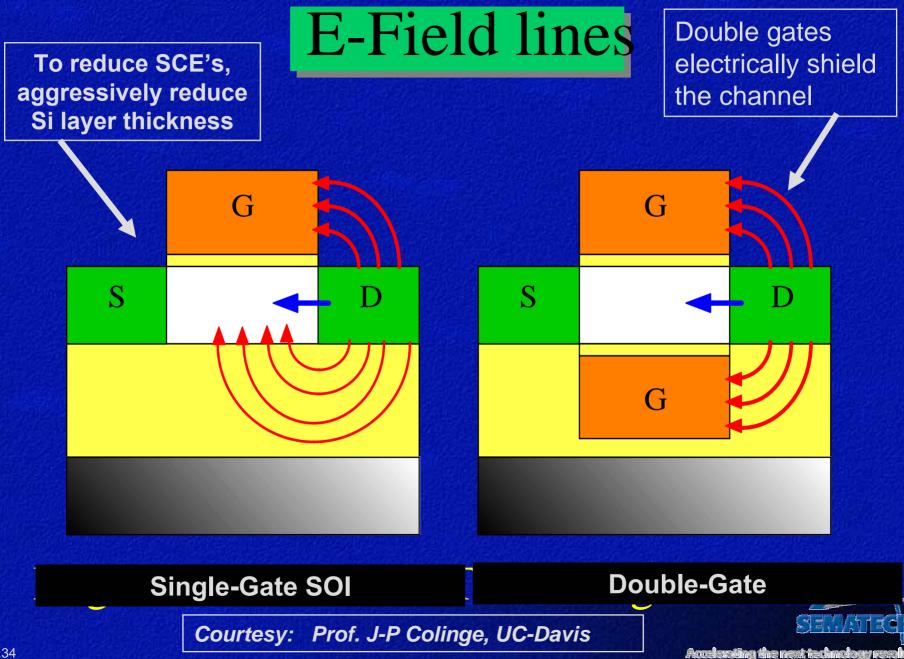

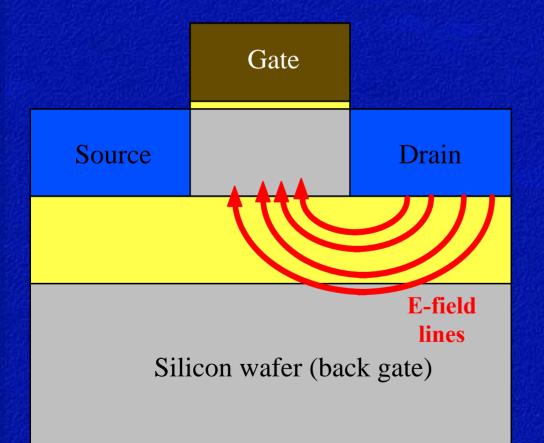

# Field Lines for Single and Double-Gate MOSFETs E-Field lines

D

To reduce SCE's, aggressively reduce Si layer thickness

S

**Single-Gate SOI**

G

Courtesy: Prof. J-P Colinge, UC-Davis

#### **Double Gate Transistors**

1. P.M. Zeitzoff, J.A. Hutchby and H.R. Huff, MOSFET and Front-End Process Integration: Scaling Trends, Challenges, and Potential Solutions Through The End of The Roadmap, International Journal of High-Speed Electronics and Systems, **12**, 267-293 (2002).

- (+ Enhanced scalability

- + Lower junction capacitance

- + Light doping possible, with near-midgap metal gate

- + ~2x drive current

- ~2x gate capacitance

- High R<sub>series,s/d</sub>→raised S/D \_- Complex process

Summary: more advanced, optimal device structure, but difficult to fabricate, particularly in this SOI configuration

#### Field Lines for Single and Double-Gate MOSFETs

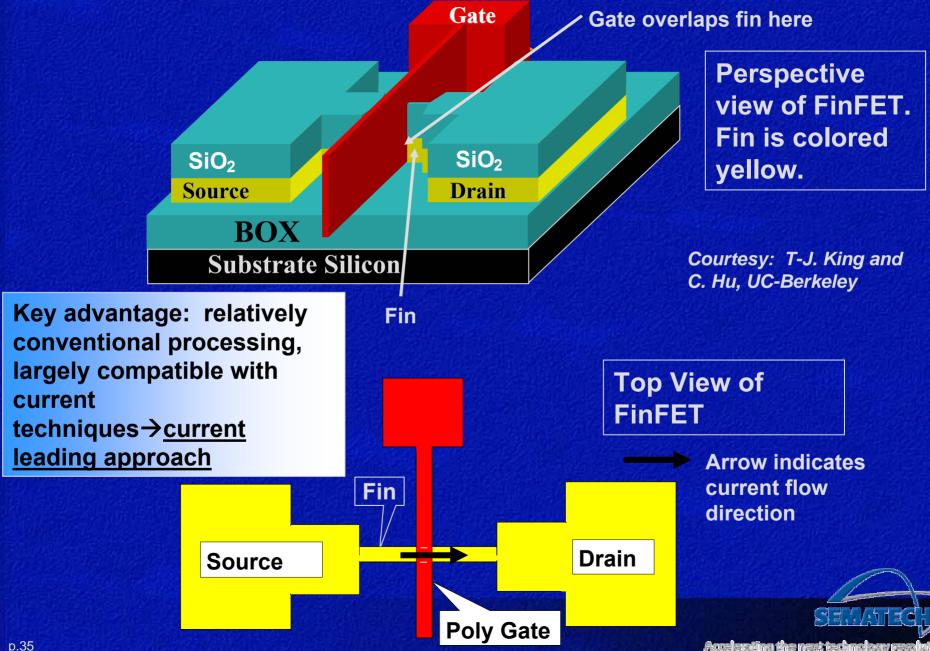

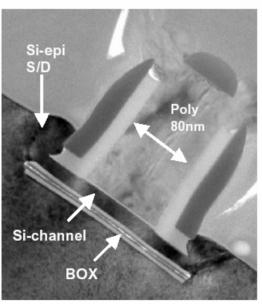

#### Other Double-Gate Transistor Structures (FinFET)

## **Types of Multiple-Gate Devices**

Courtesy: Prof. J-P Colinge, UC-Davis

## Metrology and Characterization Challenges for Non-Classical CMOS

- C-V measurements for thin, fully-depleted Si

- Single-gate SOI: measurement of very thin body thickness, 10 nm and less

- Multiple-gate

- Measurement of fin height and width, high AR

- Measuring roughness of vertical fin edges

- Measuring high- k film thickness on vertical fin edges

- Measuring 2D and 3D doping profiles in thin fins

## Outline

- Introduction

- Scaling and its impact

- Front end approaches and solutions

- Non-classical CMOS

- > Summary

#### Summary

- Rapid transistor scaling will continue through the end of the Roadmap

- Transistor performance will improve rapidly, but leakage will be hard to control

- Many technology innovations will be needed in relatively short time to enable this rapid scaling

- Front-end potential solutions include high-k gate dielectric, metal gate electrodes, and enhanced mobility through strained silicon

- High-k needed first for low-power (mobile) chips in ~ 2006

- Structural potential solutions: non-classical CMOS

- The technology innovations will raise significant challenges for metrology and characterization

- Non-classical CMOS and front-end solutions being pursued in parallel, and will likely be combined in the ultimate, end-of-Roadmap device

- L<sub>g</sub> < 10nm MOSFETs expected by the end of the Roadmap in 2018

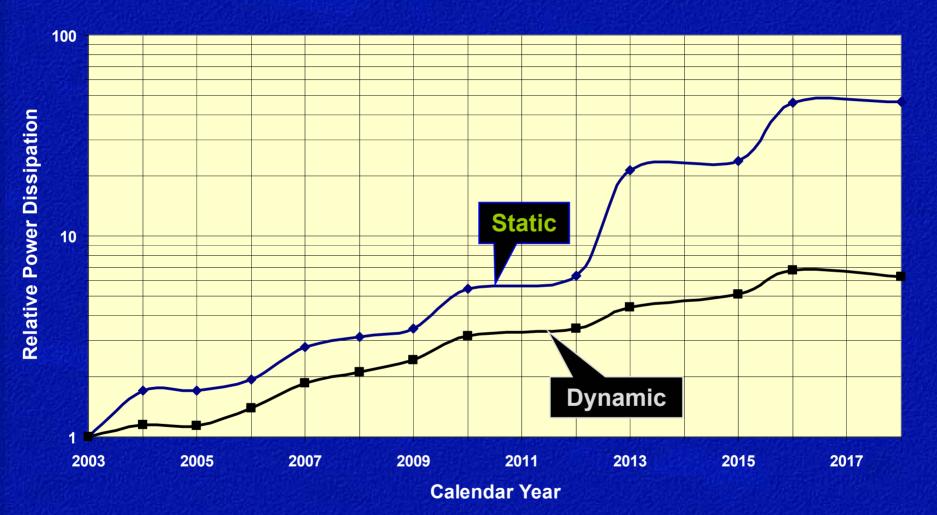

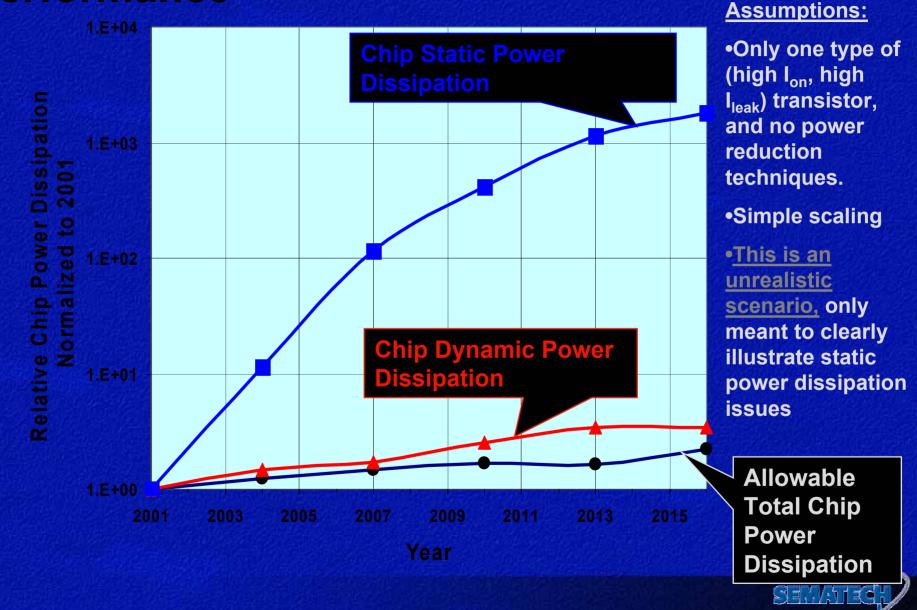

#### Potential Solutions for Power Dissipation Problems, High-Performance Logic

- Due to high leakage, static power dissipation is a special challenge

- Increasingly common approach: multiple transistor types on a chip→multi-Vt, multi-Tox, etc.

- Only utilize high-performance, high-leakage transistors in critical paths—lower leakage transistors everywhere else

- Improves flexibility for SOC

- Electrical or dynamically adjustable V<sub>t</sub> devices (future possibility)

- Circuit and architectural techniques: pass gates, power down circuit blocks, etc.

- Improved heat removal, electro-thermal modeling and design

## Timeline of Projected Key Technology Innovations from '03 ITRS, PIDS Section This timeline is from PIDS evaluation for the 2003 ITRS

|                                        |                   |                      |               |        |         | 10000                 |                           |                   |              |                      | 07.2015   | 1.775772 | 0.570   |           |          |         |

|----------------------------------------|-------------------|----------------------|---------------|--------|---------|-----------------------|---------------------------|-------------------|--------------|----------------------|-----------|----------|---------|-----------|----------|---------|

|                                        | 2003              | 2004                 | 2005          | 2006   | 2007    | 2008                  | 2009                      | 2010              | 2011         | 2012                 | 2013      | 2014     | 2015    | 2016      | 2017     | 2018    |

| Strained SiHP                          |                   | Pro                  | duction       |        |         |                       |                           |                   |              |                      |           |          |         |           | 2-117-15 |         |

| 1221月第三次第三次第三次第三次                      |                   | 82 323               | D BAY         |        | 12.70   | S11-75                | (INSTRACT                 | 11372             | U PES        |                      | 32534     |          | STRATE: | 125.75    |          | AL GEL  |

| High-k (Low Power)                     |                   |                      |               | Pro    | duction | Constant of           |                           |                   | 10001010     |                      |           |          |         |           | -70-5-02 |         |

| Elevated S/D                           |                   |                      |               |        |         | Product               | ion                       |                   |              |                      |           |          |         |           |          |         |

| High-k (HP)                            |                   | 141002)<br>2081 (Jer |               |        | Pro     | oduction              |                           | 100 A 190         |              | 2003111              |           | 4896770  |         | MICRU/AS  |          |         |

| Metal Gate (HP, dual                   | gate)             |                      |               |        | Pro     | duction               |                           |                   |              |                      | 2.340     | 11.57    |         |           |          |         |

| Metal Gate (Low Pow                    | ver, du <u>al</u> | gate)                |               |        |         | Pro                   | oduction                  | 4433              |              | ·新福州                 |           |          | +       |           | 12.94-22 |         |

| Strengen A Martin                      |                   |                      | Signal        |        | 2-34-2  |                       | $02/2$ $\lambda_{\rm ex}$ |                   |              |                      |           |          |         | a des se  |          |         |

| Ultra-thin Body                        | <u>y (UTE</u>     | <u>8) SOI</u>        | <u>, sing</u> | le gat | te (HP  | ) Pro                 | oduction                  | 21.775            | 69560        |                      | 100 febre |          |         | 11125778  |          | 22311-2 |

| Metal gate (ne                         | ar mid            | lgap f               | or UT         | BSOI   | )       | Pro                   | oduction                  |                   |              |                      |           |          |         |           |          |         |

| Strained Si (Low Pov                   | ver)              |                      |               |        |         | Pr                    | oduction                  |                   | <u>iedie</u> | NUR S                |           |          |         |           |          |         |

|                                        |                   |                      |               |        | 347 0   | States - 1            |                           |                   |              | (1)                  | Entit     | 2.20     | 22180   | E de la   |          |         |

| Multiple Gate (                        | <u>HP)</u>        |                      |               |        |         |                       |                           | Pr                | oductior     | 1                    |           |          |         |           |          |         |

| Ultra-thin Body (UTB) SOI, single gate |                   |                      |               |        | te (Lo  | Low power) Production |                           |                   |              |                      |           |          |         |           |          |         |

|                                        |                   |                      |               | 語いば    |         |                       |                           |                   |              |                      |           |          | Da      |           |          |         |

| Multiple Gate (                        | LOWF              | ower                 |               |        |         |                       | 174537270<br>175555 11    | Constant<br>Maria |              | 2357-291<br>321-2410 |           |          | Pr      | oduction  | 17.1X-71 |         |

| Quasi-ballistic                        | trans             | port (               | HP)           |        |         | O <sup>B</sup>        |                           |                   |              |                      | Pro       | duction  |         | and and a |          |         |

| Quasi-ballistic                        | trans             | port (               | LOP)          |        |         |                       |                           |                   |              |                      |           |          | Pro     | oduction  |          |         |

Accelerating the next technology result

## International Technology Roadmap for Semiconductors (ITRS)

- Industry-wide, fully international effort to map IC technology generations for the next 15 years

- For each technology generation

- Projects targets for technology characteristics and requirements

- Assesses key needs and gaps

- Lists potential solutions

- Provides common reference for semiconductor industry: device manufacturers, equipment and materials vendors, researchers

- Useful for planning

- Focus: stimulating needed R&D, not intended to restrict research

- Enabling factor in continuing to follow Moore's Law

- Much of this talk is based on the 2003 ITRS (formally presented in Dec., 2003)

## Typical Technology Requirements Table: High-Performance Logic. Data from 2003 ITRS.

| Year in Production                                                               | Units     | 2003     | 2004     | 2005     | 2006     | 2         |

|----------------------------------------------------------------------------------|-----------|----------|----------|----------|----------|-----------|

| Physical Lgate (High Performance)                                                | nm        | 45       | 37       | 32       | 28       |           |

| EOT (Equivalent Oxide Thickness)                                                 | А         | 13       | 12       | 11       | 10       | 1023      |

| Gate Poly Depletion & Inversion-Layer<br>Thickness                               | А         | 8        | 8        | 7        | 7        |           |

| Inversion Gate Dielectric Thickness<br>Value                                     | А         | 21       | 20       | 18       | 17       |           |

| Maximum Gate Leakage Limit                                                       | A/cm^2    | 2.2E+02  | 4.5E+02  | 5.2E+02  | 6.0E+02  | 9.3       |

| Power Supply Voltage                                                             | V         | 1.2      | 1.2      | 1.1      | 1.1      | cherry of |

| Saturation Threshold Voltage                                                     | V         | 0.21     | 0.20     | 0.20     | 0.21     | (         |

| Source/Drain Subthreshold Off-State<br>Leakage Drain Current                     | uA/um     | 0.03     | 0.05     | 0.05     | 0.05     | (         |

| Effective NMOS Current Drive                                                     | uA/um     | 980      | 1110     | 1090     | 1170     | 1         |

| Sub-threshold Slope Adjustment Factor<br>(Full Depletion/Dual-Gate Effects)(0-1) |           | 1        | 1        | 1        | 1        |           |

| Mobility Enhancement Factor                                                      |           | 1        | 1.3      | 1.3      | 1.4      |           |

| Effective Saturation Carrier Velocity<br>Enhancement Factor                      |           | 1        | 1        | 1        | 1        |           |

| Effective Parasitic Rsd                                                          | ohm-um    | 180      | 180      | 180      | 171      |           |

| Ideal NMOS Device Gate Capacitance                                               | F/um      | 7.4E-16  | 6.4E-16  | 6.1E-16  | 5.7E-16  | 6.0       |

| Parasitic Fringe/Overlap Capacitance                                             | F/um      | 2.4E-16  | 2.4E-16  | 2.4E-16  | 2.3E-16  | 2.2       |

| NMOS Device Time Constant                                                        | ps        | 1.20     | 0.95     | 0.86     | 0.75     | (         |

| Relative Performance Improvement (compared to 2003)                              |           | 1.00     | 1.26     | 1.39     | 1.60     |           |

| Nominal Gate Delay (NAND Gate)                                                   | ps        | 30.24    | 23.94    | 21.72    | 18.92    | 1         |

| NMOS Device Static Power Dissipation due to Drain & Gate Leakage                 | Watts/um  | 3.96E-07 | 6.60E-07 | 6.05E-07 | 6.05E-07 | 8.4       |

| NMOS Device Power Delay Product                                                  | Joules/um | 1.41E-15 | 1.27E-15 | 1.03E-15 | 9.66E-16 |           |

Asselerating the next technology revolution.

Accelerating the next technology revolution

# ITRS Projections of $V_{dd}$ and $V_t$ Scaling. Data from 2003 ITRS.

Accelerating the next technology resolution.

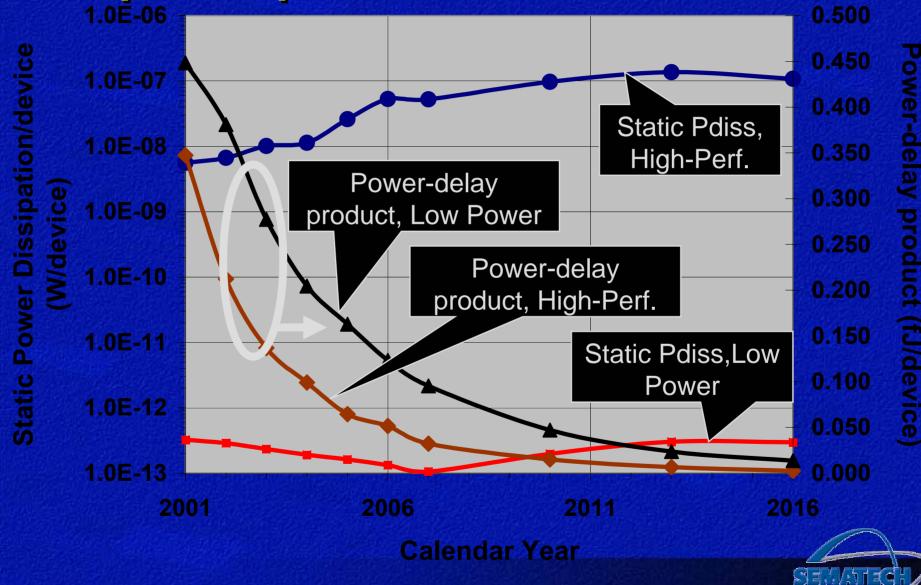

#### Key MOSFET Scaling Results, 2003 ITRS: Performance and Leakage

- High-performance logic

- Average 17%/yr improvement in  $1/\tau$  is attained

- <u>I<sub>sd,leak</sub> is high</u>, particularly for 2007 and beyond → <u>chip</u>

static power dissipation scaling is an issue

- Low-power logic

- Very low I<sub>sd,leak</sub> target is met

- I<sub>gate,leak</sub> is also very low: difficult to meet this <u>>drives</u> need for high-k gate dielectric

- $1/\tau$  is considerably lower than for high-performance, but close to 17%/yr improvement in  $1/\tau$  is still attained

- ITRS MOSFET targets are chosen to drive the technology scaling → pretty aggressive

icelerating the next technology resolution.

#### Frequency scaling: Transistor Intrinsic, Fanout-3 NAND Gate, Chip Clock for High-Performance Logic. Data from 2003 ITRS.

## **Hierarchy of IC Requirements and Choices**

Overall Circuit Requirements and Choices

Chip Power

Chip Speed

Functional Density

Chip Cost

Architecture

Etc.

•V<sub>dd</sub> •MOSFET Leakage

•MOSFET Drive current

•Parasitic series resistance

•Transistor size

•V<sub>t</sub> control

Reliability

•Etc.

T<sub>ox</sub>, L<sub>g</sub>, x<sub>j</sub>, R<sub>s</sub>

Channel engineering

•Oxynitride or High K gate dielec.

•Classical Planar Bulk or Nonclassical CMOS Structures

•Etc.

•Thermal processing

•Overall process flow

•Process modules

•Material properties

•Boron penetration

•Etc.

#### Key Overall Chip Parameters for High-Performance Logic, from 2001 ITRS

|                                                    |                         |            | Near Term |      |           |      |      |           |           |           | Long Term |  |  |

|----------------------------------------------------|-------------------------|------------|-----------|------|-----------|------|------|-----------|-----------|-----------|-----------|--|--|

| Calendar Year                                      |                         | 2001       | 2002      | 2003 | 2004      | 2005 | 2006 | 2007      | 2010      | 2013      | 2016      |  |  |

| DRAM Half Pitch                                    | nm                      | <u>130</u> | 115       | 100  | <u>90</u> | 80   | 70   | <u>65</u> | <u>45</u> | <u>35</u> | <u>22</u> |  |  |

| Physical Gate Length, L <sub>g</sub>               | nm                      | 65         | 53        | 45   | 37        | 32   | 28   | 25        |           |           |           |  |  |

| Nominal Power Supply Voltage (Vdd)                 | V                       | 1.2        | 1.1       | 1.0  | 1.0       | 0.9  | 0.9  | 0.7       | 0.6       | 0.5       | 0.4       |  |  |

| Maximum on-chip local clock frequency              | GHz                     | 1.7        | 2.3       | 3.1  | 4.0       | 5.2  | 5.6  | 6.7       | 11.5      | 19.4      | 28.8      |  |  |

| Allowable maximum power dissipation, with heatsink | w                       | 130        | 140       | 150  | 160       | 170  | 180  | 190       | 218       | 215       | 288       |  |  |

| Number of transistors per chip                     | Millions of transistors | 276        | 348       | 439  | 553       | 697  | 878  | 1106      | 2212      | 4424      | 8848      |  |  |

•The DRAM half pitch and L<sub>g</sub> are drivers of IC technology scaling, including lithography

•Technology generations (in red) defined by DRAM half pitch

•This is a dense feature: drives functional density and Litho. and Etch

–Reduction factor of 0.7X ~  $1/\sqrt{2}$  between generations (130nm in 2001, 90nm in 2004, 65nm in 2007, etc.)

-Three years between generations

–Gate length ( $L_g$ )  $\leq$  0.5 X DRAM half pitch

-These are isolated features

-Rapid scaling of L<sub>q</sub> is driven by need to improve transistor speed

## V<sub>dd</sub> and V<sub>t</sub> Device Scaling Issues

- We need to scale V<sub>dd</sub> down rapidly with the technology generations

- To keep dynamic power dissipation (~V<sub>dd</sub><sup>2</sup>) within acceptable bounds

- For reliability, control of short channel effects (SCE), general device scaling

- 1/I<sub>sd,leak</sub> exp. dependent on V<sub>t</sub>

- I<sub>on</sub> strongly dependent on gate overdrive, (V<sub>dd</sub>-V<sub>t</sub>)

- Also,  $V_{dd} \ge 2 V_t$  for circuit functionality

Scaling requires key tradeoffs between I<sub>on</sub> and I<sub>sd,leak</sub>, V<sub>dd</sub> and V<sub>t</sub>

-Tradeoff choices driven by application needs

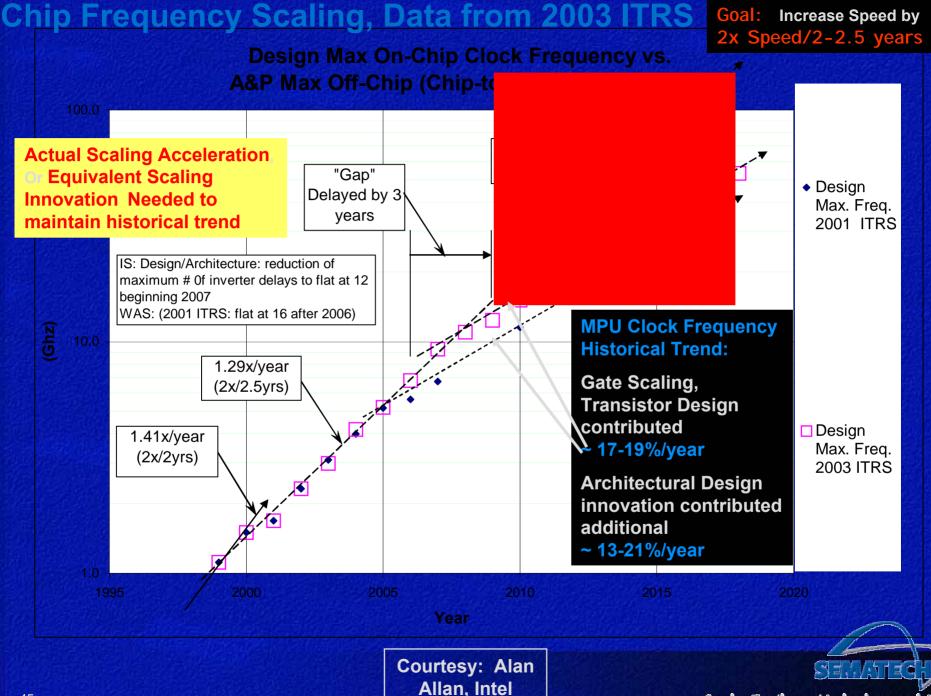

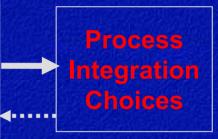

#### Historical Data and 2001 ITRS Projections for Chip Clock Frequency, High-Performance Logic

Actual Scaling Acceleration, Or Equivalent Innovation Needed to maintain historical trend

MPU Clock Frequency Historical Trend:

<u>Transistor</u> <u>scaling has</u> <u>contributed</u> <u>~ 17-19%/year</u>

Architectural Design innovation contributed additional ~ 21-13%/year

Accelerating the next technology resolution.

#### **Potential Problem with Static Power Dissipation Scaling: High-Performance Logic**

Assumption, to make a point re P<sub>static</sub>: all transistors are high performance, low V<sub>t</sub> type

Accelerating the next technology resolution

#### Relative Chip Power Dissipation, High Performance

Accelerating the next technology resolution.

## **ITRS Projected Scaling of Power Dissipation per Device**

fJ/device

Accelerating the next technology reso

#### Impact of Key MOSFET Parameters on Chip Power Dissipation

- $P_{total} = P_{dynamic} + P_{static}$

- $-\mathbf{P}_{dynamic} = \mathbf{C}_{active} \, \mathbf{V}_{dd}^2 \, \mathbf{f}_{clock}$

- With scaling,  $C_{active}$  and  $f_{clock}$  increase rapidly

- <u>To keep P<sub>dynamic</sub> within tolerable limits, reduce</u>

<u>V<sub>dd</sub> with scaling</u>

- Reduce V<sub>dd</sub> for reliability, SCE, general device scaling reasons, also

- $-\mathbf{P}_{\text{static}} = \mathbf{N}_{\text{off}} \mathbf{W} \mathbf{I}_{\text{leak}} \mathbf{V}_{\text{dd}}$

- With scaling,  $N_{\text{off}}$  increases rapidly, but  $V_{\text{dd}}$  and W scale down

- <u>To keep P<sub>static</sub> within tolerable limits</u>, <u>constrain increase of I<sub>leak</sub> with scaling</u>

#### Solutions for Power Dissipation Problems, High-Performance Logic

- Increasingly common approach: multiple transistor types on a chip $\rightarrow$ multi-V<sub>t</sub>, multi-T<sub>ox</sub>

- Only utilize high-performance, high-leakage transistors in critical paths—lower leakage transistors everywhere else

- Improves flexibility for SOC

- Electrical or dynamically adjustable V<sub>t</sub> devices (future possibility)

- Circuit and architectural techniques: pass gates, power down circuit blocks, etc.

## Summary: MOSFET Scaling MOSFET scaling is the "raw material" for designers to improve chip performance, control

- power dissipation

- MOSFET scaling projected to scale at historical ~17% per year in "raw" speed improvement for highperformance logic

- Design and architectural innovation has contributed about as much, but is expected to slow down in the future: continued MOSFET speed improvement is critically important

- MOSFET scaling goals are critically important

- High-performance logic emphasizes speed at the expense of high leakage and static power dissipation

- Low-power logic emphasizes low leakage at the expense of speed

- Static power dissipation is a growing problem for high-performance logic, and there are numerous approaches to dealing with it

## **High-K Issues**

- Process integration

- Thermal stability of high-k material

- Retain high-k performance with planar CMOS flow (S/D anneal, etc.,) challenge

- Chemical, electrical compatibility with polysilicon

- Boron penetration

- PMOS V<sub>t</sub>

- Metal electrode may be required

- Interface with Si substrate and gate electrode

- Deposition / post process anneals  $\Rightarrow$  thin SiO<sub>2</sub>-like layer

- Interface properties: D<sub>it</sub>, Q<sub>f</sub>, μ = μ(interfacial "SiO<sub>2</sub>")

- Charges and charge trapping in high-k: V<sub>t</sub> control and instability

- Mobility degradation

- Leakage, reliability

- •... New material: major challenge

## **Polysilicon Limitations**

- Polysilicon depletion

- Increases effective electrical T<sub>ox</sub> → reduces inversion charge & I<sub>on</sub>

- More of a problem as T<sub>ox</sub> is scaled → Poly doping must increase with scaling

- PMOSFETs: B penetration through very thin oxides

- Oxy-nitrides & reduction of DT effective now

- Compatibility with high-k

- Gate resistance of very thin gates (even with silicide)

1. P.M. Zeitzoff, J.A. Hutchby and H.R. Huff, MOSFET and Front-End Process Integration: Scaling Trends, Challenges, and Potential Solutions Through The End of The Roadmap, International Journal of High-Speed Electronics and Systems, **12**, 267-293 (2002).

2. Mark Bohr, ECS Meeting PV 2001-2, Spring, 2001.

## **Non-Classical CMOS Summary**

- Below L<sub>g</sub> = 25nm or so, planar bulk CMOS may not scale effectively

- Ultra-thin body, single-gate SOI and (eventually) multiple-gate, ultra-thin body MOSFETs are more optimal from a device point of view than planar bulk CMOS. Key issues:

- Effectiveness of planar bulk CMOS scaling in this regime

- Working but suboptimal 8nm devices reported in literature

- Finding effective solutions to difficult processing issues for SOI and multiple-gate

- Ultimate MOSFET (Lg < 10nm) likely to be multiple-gate with high-k, metal gate electrodes, strained Si, etc.

- Such devices will require metal electrodes with nearmidgap work functions

- Tuning of work function of single metal gate material may be feasible

**High-k Gate Dielectric Candidates and Key Issues** Modest k (<10) • Al<sub>2</sub>O<sub>3</sub> Negative charge, complicated defect structure Medium k (10-25) • Group IV Oxides - ZrO<sub>2</sub>, HfO<sub>2</sub> Low crystallization temperature • Group III Oxides - Y<sub>2</sub>O<sub>3</sub>, La<sub>2</sub>O<sub>3</sub>,... Charge • Silicates - (Zr, Hf, La, Y, ..) SiO<sub>4</sub> Lower k if too dilute • Aluminates - (Zr, Hf, La, Y, ..)•Al<sub>2</sub>O<sub>3</sub> Charge issue, complicated defect structure High k (≥ 25) •  $Ta_2O_5$ ,  $TiO_2$  Low-barrier height C. M. Osburn and H.R. Huff, Spring ECS abst. # 366

## $MOCVD HfO_2 CV Curve (EOT = 0.95 nm)$

Microelectronics, 2001 MRS Workshop Series (2001)

Accelerating the next technology resolution.

## **Difficult Transistor Scaling Issues**

- With scaling, increasing difficulty in meeting transistor requirements

- High gate leakage

- Direct tunneling increases rapidly as  $T_{ox}$  is reduced

- Potential solution: high-k gate dielectric

- Poly depletion in gate electrode → increased effective T<sub>ox</sub>, reduced I<sub>on</sub>

- Potential solution: metal gate electrode

- Need for enhanced channel mobility

- Potential solution: strained Si channels

## **Other Structures of Interest**

Silicon on Nothing (SON): localized buried oxide (BOX)

REF: S. Monfray et al., '01 IEDM, p. 645.

**STM '01**

Accelerating the next technology resolution.

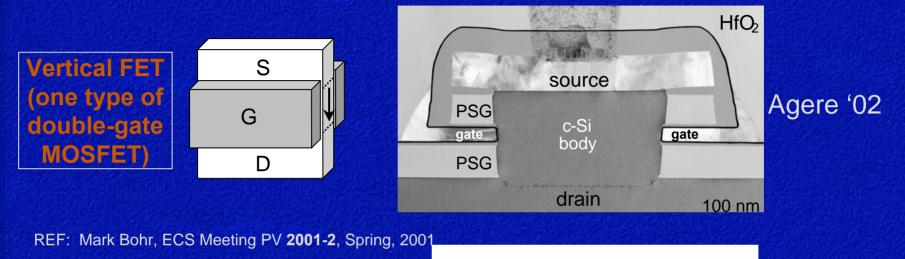

#### Vertical Transistor Structure with High-k (Agere '02 IEDM)

Jack Hergenrother et. al., 50 nm Vertical Replacement-Gate (VRG) nMOSFETs with ALD HfO<sub>2</sub> Gate Dielectrics, *Semiconductor Silicon/2002*, ECS **PV 2002-2**, 929-942 (2002) Reproduced by permission of The Electrochemical Society, Inc.

Accelerating the next technology resolution.

## **Assumptions for All Logic Types**

- All modeling is done for nominal devices, room T

- Models are simplified (spreadsheet-based), assume basic transistor functioning doesn't change

- No dynamic Vt

- S=85 mV/decade

- EOT<sub>electrical</sub> = EOT + 0.8 nm/0.4nm→0.8 nm for poly gate, 0.4 nm for metal gate (in 2007 or beyond)

- Log(I<sub>sd,leak</sub>)~-Vt/S

- Gate leakage and junction leakage are related to I<sub>sd,leak</sub>

- Id,sat~g<sub>m,eff</sub> (Vdd-Vt)

- Cideal =  $\varepsilon ox/(EOT_{electrical})$ ; Cgate = Cideal + Cparasitic

- <u>τ=(Cgate Vdd)/(Id,sat)= intrinsic transistor delay</u>

- Parasitic Rs,d is included (20-30% of Vdd/ld,sat = Ron)

- PMOS is like NMOS, except PMOS Id,sat is 40-50% of NMOS Id,sat

- **D**.68 S/D junction capacitance is ignored in calculating the second

#### Simplified Cross-Section of High K Gate Dielectric Stack

Asselerating the next technology revolution.

#### **Process - Structure - Property Relation**

- Crystallinity / polycrystallinity

- Phase structure

- Epitaxial alignment to substrate

- Stoichiometry

- Bond coordination

- Morphology

- Interfacial microroughness

- Retention of amorphicity by doping

- Mixed oxide phase separation

- Spatial inhomogeneity / periodicity in energy gap(s)

#### Why High-K (Dielectric Constant)?

- Direct tunneling current depends on film physical thickness and barrier height (φ)

- $I_{DT} \propto [exp \sqrt{[(2m*q \phi / (h/2\pi)^2]}]$

- Transistor drive current depends on film electrical thickness

- $I_{DSAT} = (w/2I) (3.9K_oA) (T_{EOT,INV})^{-1} \mu (V_G V_T)^2; V_G \Rightarrow V_{DD}$

- $T_{EOT} = T_{phys} \times (k_{SiO_2}/k_{high k})$

- $k_{SiO_2} = 3.92; k_{high k} \approx 15 25$

- Increasing k increases I<sub>dsat</sub> without increasing I<sub>DT</sub>

- Transistor performance improves or thickness may be increased (with increased k) to reduce gate leakage (direct tunneling) current without loss of transistor performance

- High-k gate dielectric proposed to obviate IC power concern while still achieving required gate electrode capacitive coupling with silicon

High-k introduces new set of design constraints

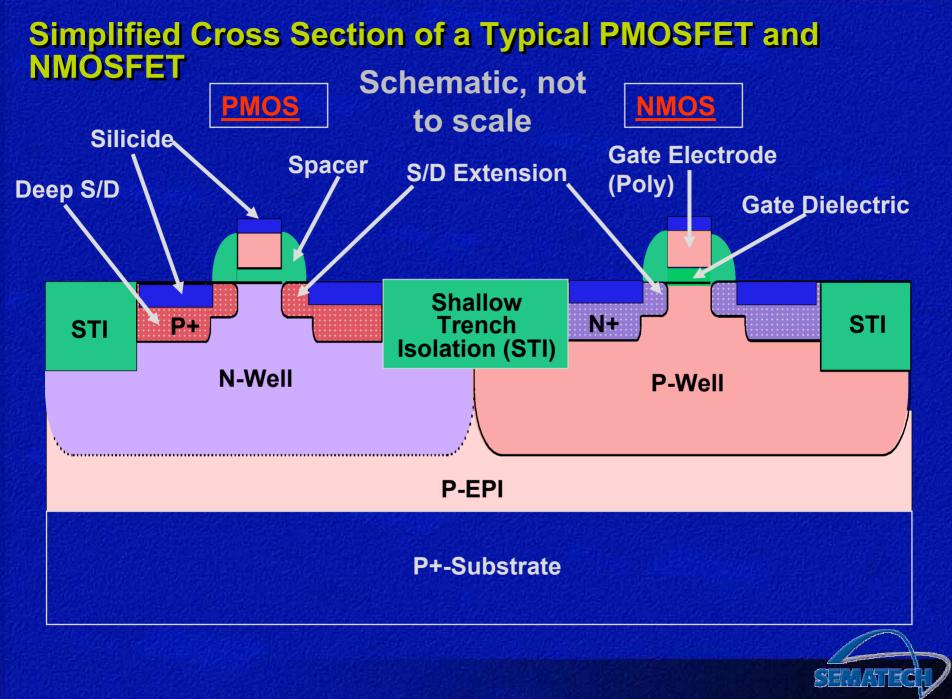

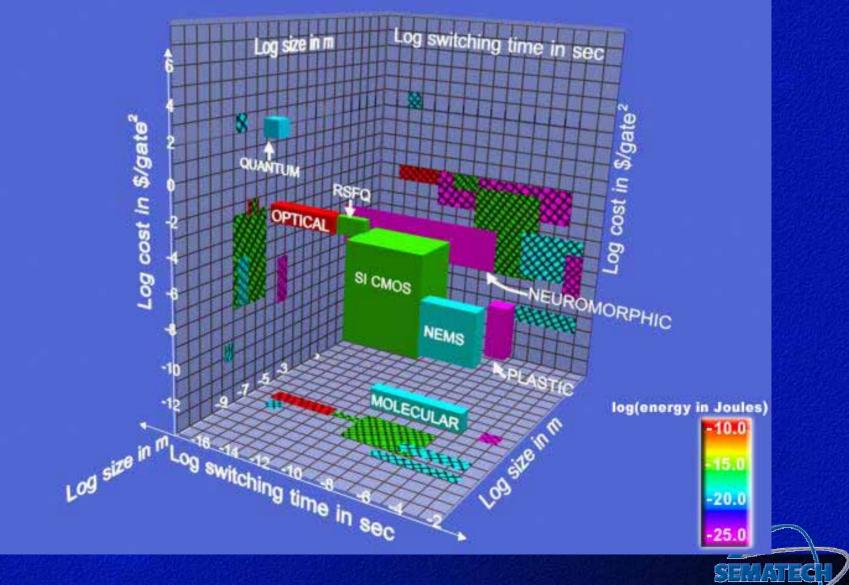

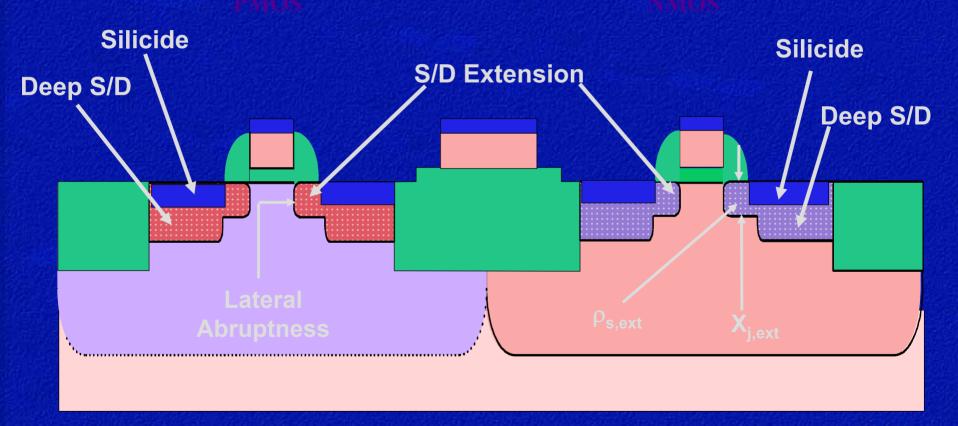

# Simplified Cross Section of a Typical PMOSFET and NMOSFET

#### (Not to scale)

# **S/D Extension Issues**

Schematic, not to scale

# S/D Extension Issues

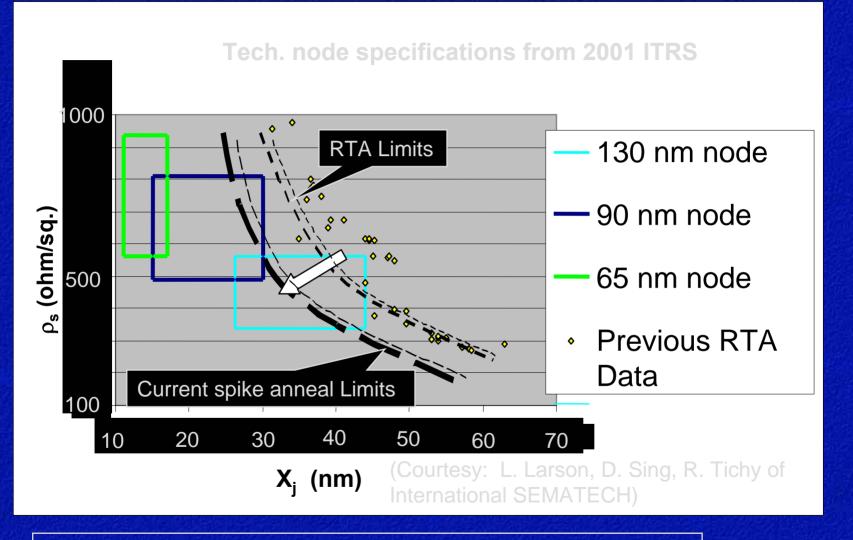

Increasingly abrupt, shallow, heavily doped profiles required for successively scaled technologies - Needed for optimal devices, esp. to control short channel effects (SCE) – Difficult ρ<sub>s</sub>-x<sub>j,ext</sub> tradeoffs, esp. for PMOS (B)→ difficult to control R<sub>S/D,series</sub>

#### S/D Extension Solutions

65 nm node and beyond: may require novel doping and annealing techniques

p.77

# **S/D Extension Potential Solutions**

- Shorter range

- Ultra-low energy implants (< 1 KeV, B)</li>

- Rapid Thermal Processing (RTP) and spike anneal: reduces DT & TED

- Increase dose as much as possible==>reduced R<sub>series,s/d</sub>

- Beyond 90 nm technology generation

- Laser thermal annealing

- Doped, selective epi

- Co-implant

- Others

Accelerating the next isolatelogy resolution.

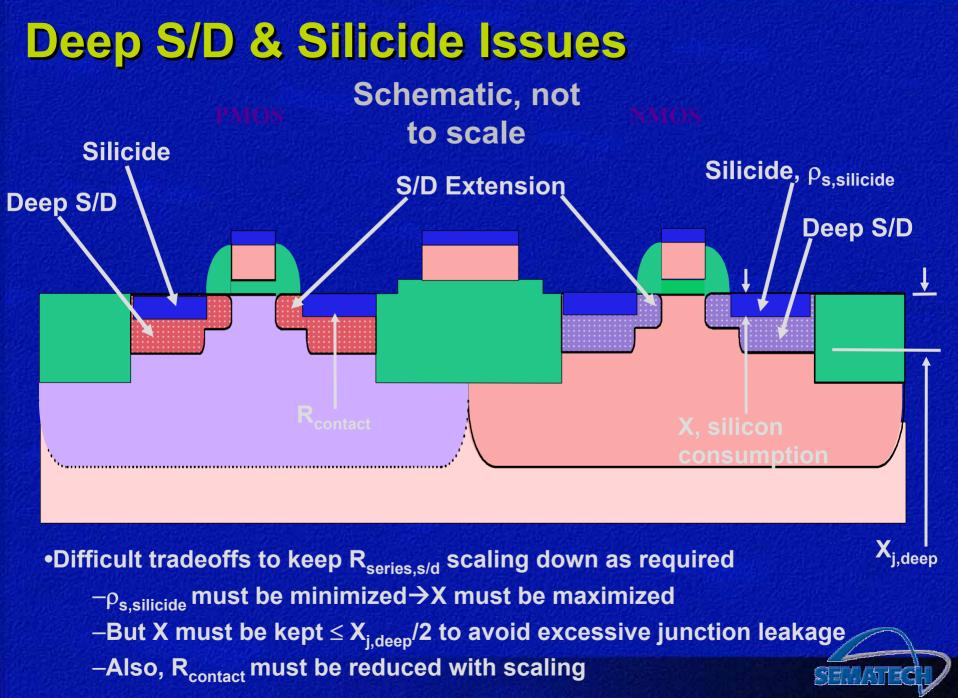

Deep S/D & Silicide Potential Solutions

Through 90 or 65 nm generation, tradeoffs to get acceptable R<sub>series,s/d</sub> are possible

- Change silicide to get better ρ<sub>s,silicide</sub>- X tradeoff: TiSi<sub>2</sub>→CoSi<sub>2</sub>→NiSi

- Potential long-range solutions

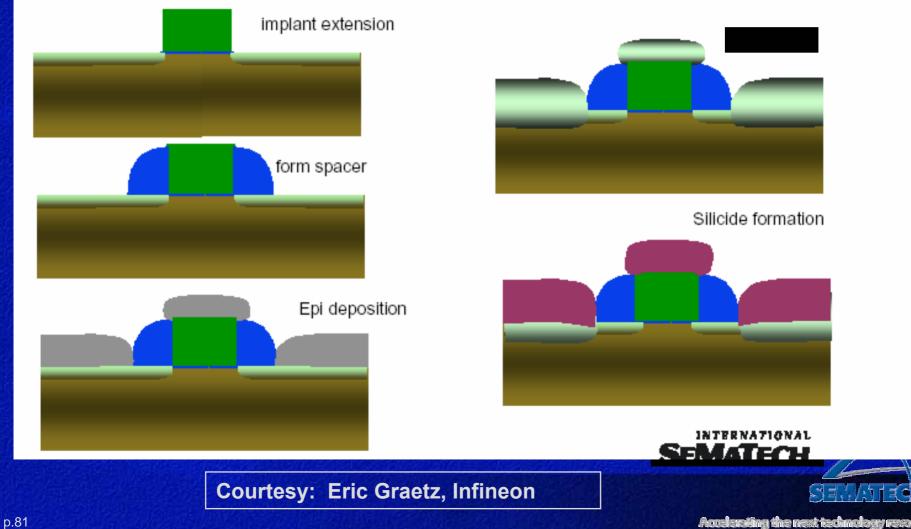

- Elevated S/D: doped, selective epi

- Reduced R<sub>contact</sub>

- Selective CVD silicide tailor Schottky energy barrier

- Selective deposited metal

# **Elevated S/D**

Elevated S/D with Selective (Epitaxial) Silicon and Post Implant

#### **Device Metrics**

Power

•  $P_{dynamic} = f_{clock} C_{load} V_{DD}^2 and P_{static} = N_{tr} W I_{leak} V_{DD}$

- Intrinsic transistor gate delay (speed)

- $\tau = \mathbf{C}_{\mathsf{load}} \mathbf{V}_{\mathsf{DD}} / \mathbf{I}_{\mathsf{DSAT}}$

- Maximum saturated drain current (I<sub>DSAT</sub>): ideal, long-channel device

- $I_{DSAT} = (W/2L_{phys}) (3.9K_oA) (T_{EOT,INV})^{-1} \mu_{eff} (V_G V_T)^2$

- » W and  $L_{phys}$  device width and physical gate length

- » T<sub>EOT,INV</sub> = equivalent oxide thickness in inversion

- »  $\mu_{eff}$  = mobility, generally determined for a long-channel device (g<sub>m</sub>)

- »  $V_G V_T =$  gate overdrive, where  $V_G$  is supply voltage ( $V_{DD}$ ) applied to gate ( $V_G \Rightarrow V_{DD}$ ) and  $V_T$  is threshold voltage

- $C_{load} \sim (3.9K_oA) (T_{EOT,INV})^{-1} = \varepsilon_{ox} / T_{EOT,INV}$

- Transconductance

- $g_m = (W/L_{phys}) (3.9K_oA) (T_{EOT,INV})^{-1} \mu_{eff} V_{DD}$

- $T_{EOT} = (k_{high k} / k_{SiO2}) T_{phys}$

- S = Sub-threshold swing  $\Rightarrow$  Inverse slope of log I<sub>D</sub> versus V

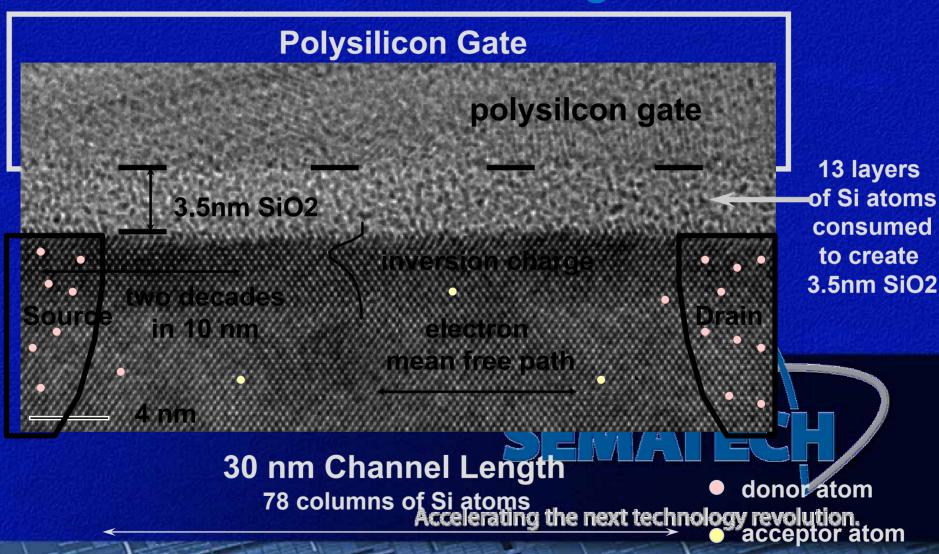

#### High Resolution TEM Showing 30 nm Channel Length

Courtesy of Yoshi Nishi / Dick Chapman

Mar 25, 2003 2003 International Conference on Characterization and Metrology for ULSI Technology

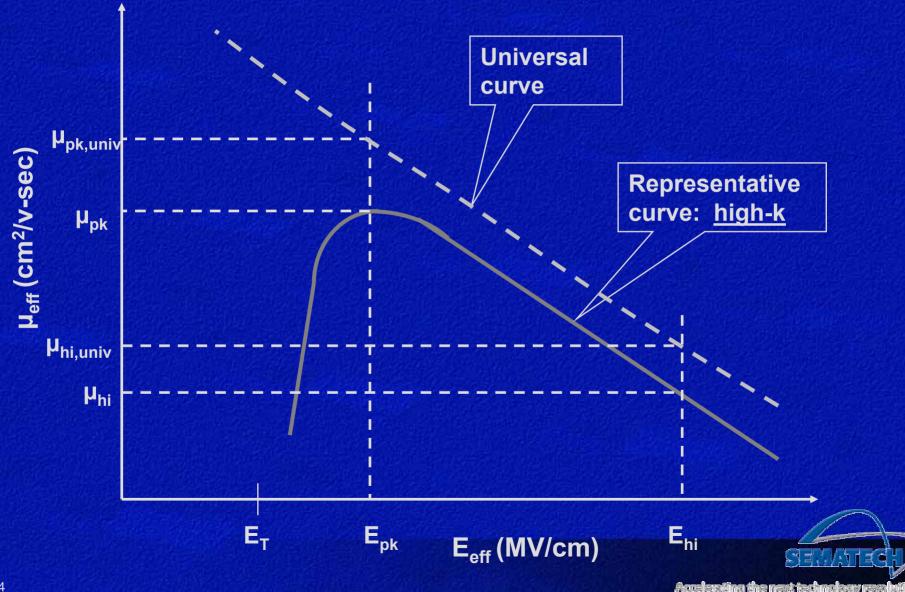

#### Representative Theoretical and Universal Mobility Curve

### **Mobility Considerations**

#### Theoretical

- Low electric field

- Unscreened (by inversion layer free carriers) ionized dopant scattering centers in silicon

- High electric field

- Acoustic phonons

- Surface microroughness

- H x L (where *H* is height of surface undulation and L is undulation correlation length)

- Remote scattering due to high-k phonons

- Experimental adders (not presently theoretically **modeled**

- Interfacial and high-k bulk traps

- N, AI and other elemental scatterers

- Crystalline inclusions in amorphous high k gate dielec

- Remote scattering due to gate electrode

- Universal curve only considers high electric field • contributions (extends to low electric field)

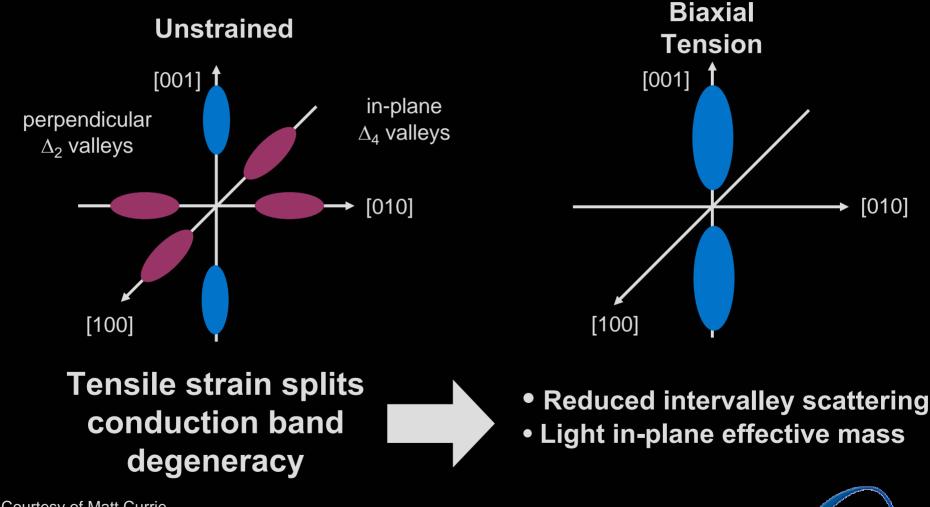

### **Electron Transport in εMOS™**

Courtesy of Matt Currie AmberWave Systems Corp. SEMATEGY Accelerating the next technology revolution.

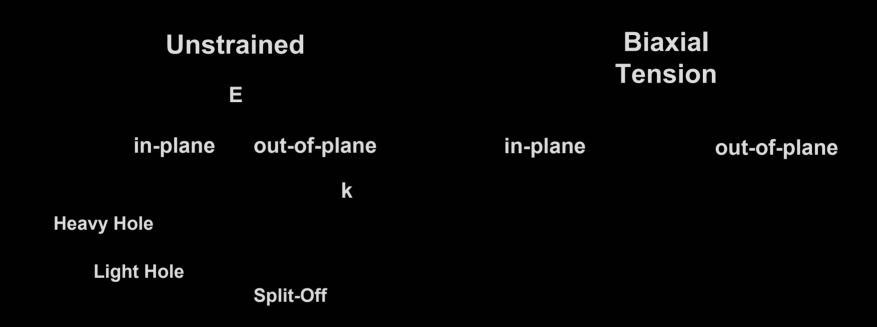

### **Hole Transport** in εMOS<sup>™</sup>

#### Tensile strain splits valence band degeneracy

Courtesy of Matt Currie AmberWave Systems Corp.

- Reduced intervalley scattering

- Light in-plane effective mass

#### **Transistor Structures**

- + Wafer cost / availability

- SCE scaling difficult

- High doping effects and Statistical variation

- Parasitic junction capacitance

- + Lower junction cap

- + F.B. performance boost

- F.B. history effect

- SCE scaling difficult

- Wafer cost/availability

- + Lower junction cap

- SCE scaling difficult

- High R<sub>series,s/d</sub>→raised S/D

- Sensitivity to Si thickness (very thin)

Wafer cost/availability

#### **References:**

1. P. Zeitzoff, J. Hutchby and H. Huff, to be pub. in Internat. Jour. Of High Speed Electronics and Systems

2. Mark Bohr, ECS Meeting PV 2001-2, Spring, 2001

# Schematic cross section of planar bulk, UTB SOI, and DG SOI MOSFET

Asselscripting the next technology resolution

# Schematic cross section of planar bulk, UTB SOI, and DG SOI MOSFET

#### Schematic cross section of planar bulk, UTB SOI and DG SOI MOSFET

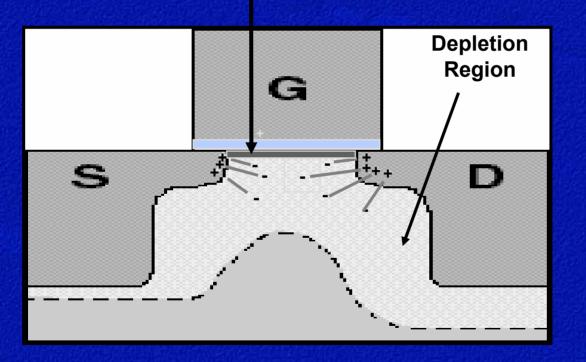

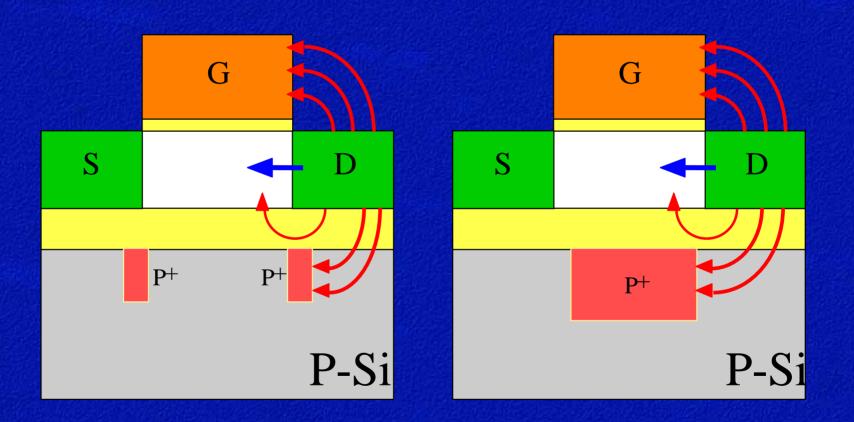

# Short-channel MOSFET: DIBL

#### or: Drain-Induced Barrier Lowering

**Electric field lines** from the drain encroach on the channel region. Any increase of drain voltage decreases the threshold voltage (the "NPN" potential barrier between source and drain is low

### **Ground-plane SOI MOSFETs**

Accelerating the next technology resolution.

SELVATES

#### **Electrostatic Scaling - Channel Leakage (I<sub>off</sub>)**

Jim Hutchby

Accelerating the next technology revolution.

ਿੰਸ ਤੋ