# From The Lab to The Fab: Transistors to Integrated Circuits

#### Howard R. Huff International SEMATECH Austin, TX 78741

Mar 25, 2003

2003 International Conference on Characterization and Metrology for ULSI Technology

# Agenda

- Introduction

- Threshold events

- Transistor Fabrication

- Point-contact

- Grown-junction

- Alloy formation

- Diffusion

- Mesa and planar advances

- Integrated circuit beginnings

- Bipolar and DRAM IC Issues

- (1960-1980's)

- Prognosis

- Acknowledgements

Mar 25, 2003

2003 International Conference on Characterization and Metrology for ULSI Technology

## **Transistors to Integrated Circuits**

Used with permission of the Estate of John Bardeen

Reproduced by Permission of the IEEE, Inc.

Reproduced by Permission of the IEEE, Inc SEMATECH Courtesy of Texas Instruments, Inc. 2003 International Conference on Characterization and Metrology for ULSI Technology

## **Nevill Mott**

Courtesy of Fred Seitz

## **Walter Schottky**

Courtesy of Fred Seitz

## Hans Bethe (Ann Arbor, 1935)

Courtesy of Lillian Hoddeson

## Fabrication of Metallurgical Grade Ge and Si

- Conversion of Ge and Si ores to metallurgicalgrade material and their subsequent purification by Fred Seitz in conjunction with Dupont

- Zn + SiCl<sub>4</sub>  $\Rightarrow$  Si + ZnCl<sub>4</sub> (vapor phase reaction)

- Purity to about 1 part in 10<sup>5</sup>

### **Fred Seitz**

H.R.Huff,J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

SEMATECH 8

## **C. Marcus Olson (center)**

Courtesy of Fred Seitz

INTERNATIONAL SEMATECH 9

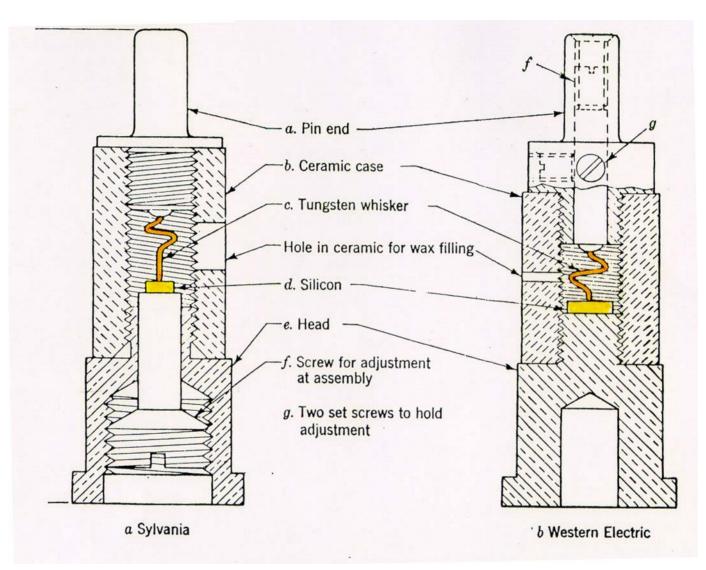

## **Crystal Rectifiers For Radar in WW II**

After Michael Riordan (Torrey and Whitmer)

## **Mervin Kelly**

Courtesy of Fred Seitz

### **John Bardeen**

Courtesy of Lillian Hoddeson

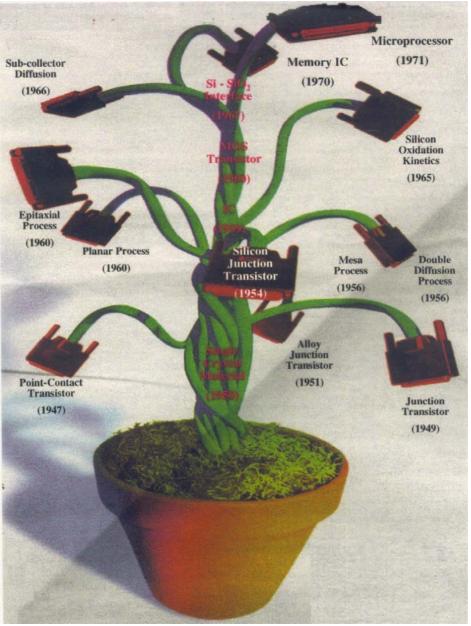

## **Tree of Growth**

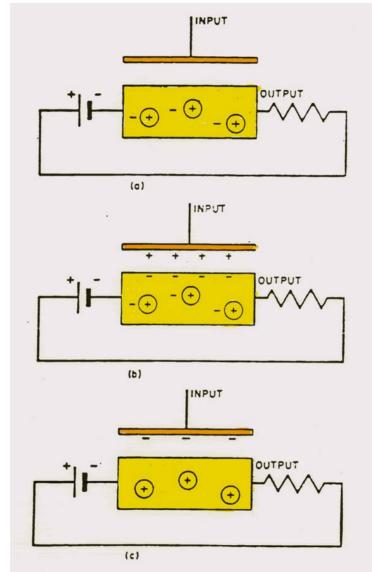

#### **Shockley's Field-Effect Experiment**

After W. Shockley, *Path to The Conception of The Junction Transistor*, IEEE Trans. Electron Devices, **ED-23**, 597-620 (1976), reprinted in **ED-31**, 1523-1546 (1984) © 1984 IEEE

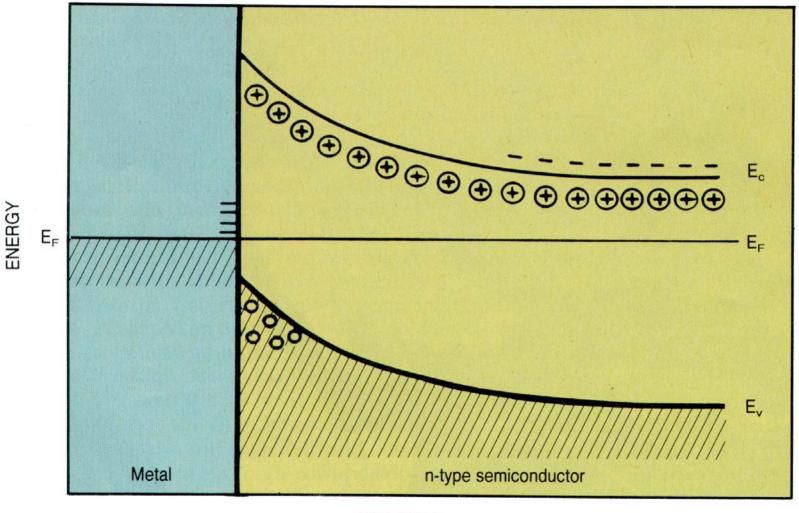

#### Energy -Level Diagram For Metal / N-Type Semiconductor With Surface States

DISTANCE

After NICK HOIONYAK

Mar 25, 2003

2003 International Conference on Characterization and Metrology for ULSI Technology

INTERNATIONAL

15

### Historic Day: December 16, 1947 (con't)

Used with permission of the Estate of John Bardeen

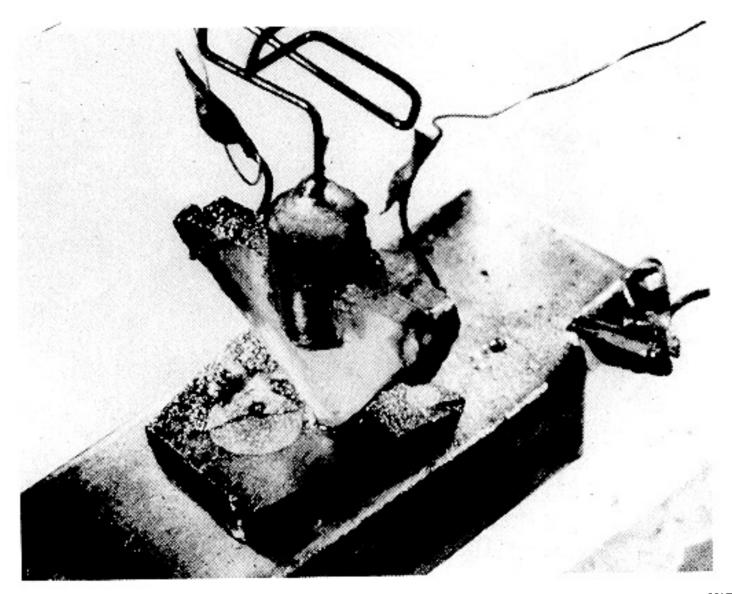

#### The Press Announcement - July 1, 1948

After Michael Riordan

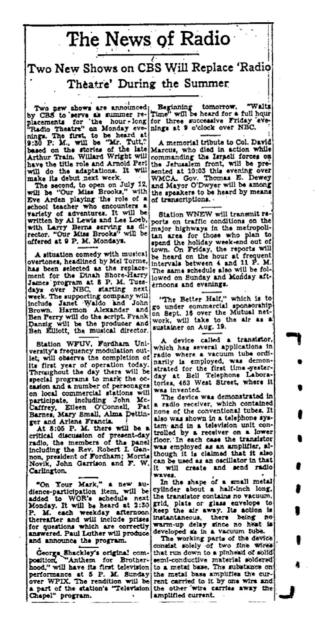

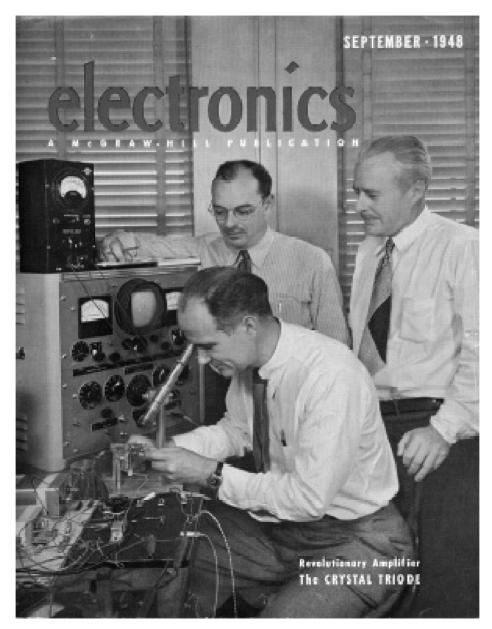

#### **The Famous Picture**

Courtesy of Lillian Hoddeson

## **Brattain, Shockley and Bardeen**

Courtesy of Lillian Hoddeson

Mar 25, 2003

2003 International Conference on Characterization and Metrology for ULSI Technology

INTERNATIONAL SEMATECH 19

## **The Famous Picture (25 Years Later)**

Courtesy of Lillian Hoddeson

- Recapitulation Serendipity Factors

Solid-state amplifier invented by Bardeen and Brattain "completely different in principle and function from fieldeffect transistor proposed by Shockley [envisioned as majority carrier device] but served original goal as triode amplifier"

- "Failure of Shockley's original field-effect transistor device"

- "Bardeen's focus on surface states and inversion layer unexpectedly generated point-contact transistor configuration"

- "Switch from Si to Ge"

- Utilization of two whiskers "close" together

- Brattain's accidental destruction (in his mind) of GeO<sub>2</sub> film (subsequently realized not present)

- "Results ... obtained by admixture of accident, brilliant insight and luck .... The fact results were reverse of what they expected initially ... namely that minority, rather than majority carriers, were modulated is irrelevant. Accident had favored their prepared minds! They were amply prepared to understand and exploit the breakthrough...."

- "Bardeen & Brattain's attentiveness to pick up implications of their invention"

21

### **Purdue Team**

Courtesy of Fred Seitz

Mar 25, 2003 2003 International Conference on Characterization and Metrology for ULSI Technology

INTERNATIONAL SEMATECH 22

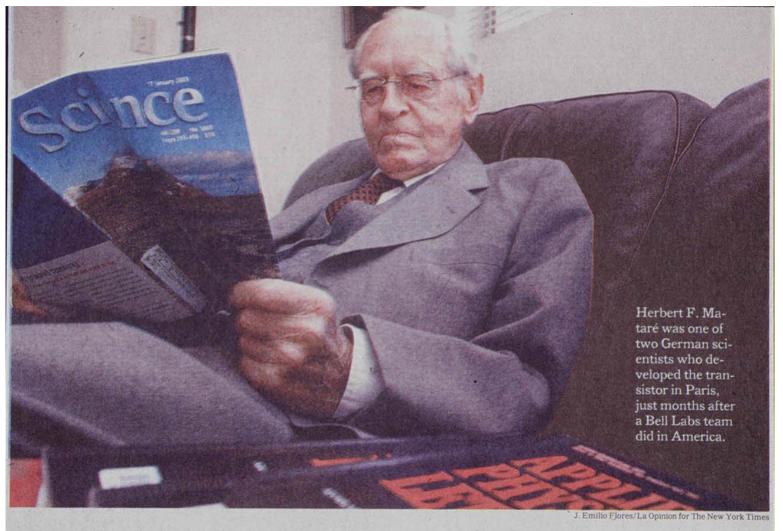

### **Herbert Matare**

#### A Parallel Inventor of the Transistor Has His Moment

Courtesy of Fred Seitz

## **Patents**

- Original patent application applied by BTL included Shockley's field-effect transistor, albeit effect was extremely small

- AT&T attorneys, however, found previous patents awarded for rather similar field-effect amplifiers to Lilienfeld (as early as 1930) and Heil

- Sah has noted neither Lilienfeld nor Heil recognized necessity of inversion layer for operation of their proposed devices

INTERNATIONAL

24

SFMA

- Shockley not included in point-contact patent application

- Severe disappointment became major impetus for spurring Shockley's subsequent seminal contributions

- Injection over barrier

- P-n junction theory

- P-n junction transistor

### **J.E. Lilienfeld**

Courtesy of Fred Seitz, Reprinted with permission from *Physics Today* [May 1988]:87 © 1988 American Institute of Physics.)

## **Summary**

- "..... Nearly all present-day field-effect transistors make use of controlling flow in an inversion layer of opposite conductivity type adjacent to surface (such as n-type inversion layer on p-type silicon.) *I [Bardeen] have basic patent on use of inversion layer to confine flow. Presentday bipolar transistors are of junction type and based on patented structure Shockley invented* while planning experiments to elucidate dynamics of point-contact transistor.

- Bell Laboratories patent department was unable to obtain patent on Shockley's field-effect invention because of Lilienfeld's patents and others." (Bardeen)

- "It seems likely that many inventions unforeseen at present will be made based on the principles of carrier injection, the field effect, the Suhl effect, and the properties of rectifying junctions. It is quite probable that other new physical principles will also be utilized to practical ends as the art develops." (Shockley)

26

### Summary (con't)

"This book [Electrons and Holes in Semiconductors] had its origins in a series of lectures given at Bell Telephone Laboratories in connection with the growth of the transistor program. It thus owes its existence basically to the *invention of the transistor by J. Bardeen and W.H. Brattain."* (Shockley)

### Summary (con't)

John Bardeen, co-inventor of the pointcontact transistor and inventor of the MOS transistor, may rightly be called the

## father of modern electronics

### Bardeen / Schottky / Brattain - Pretzfeld, 1954

After Erhard Sirtl

INTERNATIONAL SEMATECH 29

# Agenda

- Introduction

- Threshold events

- Transistor Fabrication

- Point-contact

- Grown-junction

- Alloy formation

- Diffusion

- Mesa and planar advances

- Integrated circuit beginnings

- Bipolar DRAM IC Issues

- (1960-1980's)

- Prognosis

- Acknowledgements

Mar 25, 2003

2003 International Conference on Characterization and Metrology for ULSI Technology

# **Single-Crystal Growth**

- Polycrystalline Ge and Si materials utilized at BTL and elsewhere for transistor R&D in late '40s and early '50s

- Utilization of single crystals of Ge and Si extremely controversial

- Shockley opposed work on Ge single crystals because he had publicly stated that transistor science could be elicited from small specimens of polycrystalline masses of material

- Teal believed criticality of single-crystals for electronics era, recognizing Shockley's bipolar junction characteristics in single crystal Ge and Si would be substantially better and more reproducible than polycrystalline material

- Teal believed fundamental property of crystalline semiconductor was easily controllable and spatially variable concentration, type and mobility of free carriers

- Technologically important to ensure many complex units to be identical, close performance tolerances, high yields and low cost

NTERNATIONAL

## Single-Crystal Growth (con't)

- Teal reasoned essential to have high-perfection, high-purity controlled composition to achieve separation of various available electron and hole conduction processes, which was not appreciated for semiconductor applications

- Required to to analyze and understand operation of devices and achieve optimum functional usage

- To produce conducting medium in which a high degree of lattice perfection, of uniformity of structure and chemical purity attained

- To build into this highly perfect medium in controlled way required resistivities and electrical boundaries to give a variety of device possibilities by control of chemical composition (i.e., donor and acceptor concentration) along direction of single crystal growth

INTERNATIONAL

32

SEN

## **Gordon Teal**

H.R.Huff,J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

## **Dopants in Silicon**

- Jack Scaff / Greiner contributed to comprehension of n- and p-type dopants in Ge and Si

- Dopants occupied substitutional sites in equilibrium

- Ground states approximately 40-50 meV from appropriate band edge in Si

## Single-Crystal Growth (con't)

- Crystalline materials facilitated experimental verification of many quantum theoretical concepts of electrons and holes

- Effective mass

- Drift and conductivity mobility

- Carrier lifetime

- Tunneling

- P-n junction phenomena

- By early '50s all investigators of semiconductor properties & p-n junction studies of Ge/Si utilized pulled single crystals

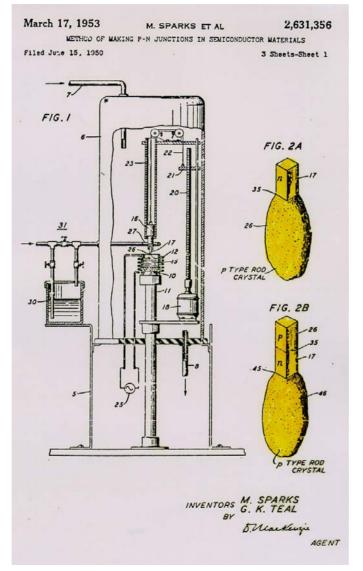

- Teal filed p-n junction patent in single-crystal Ge in '50

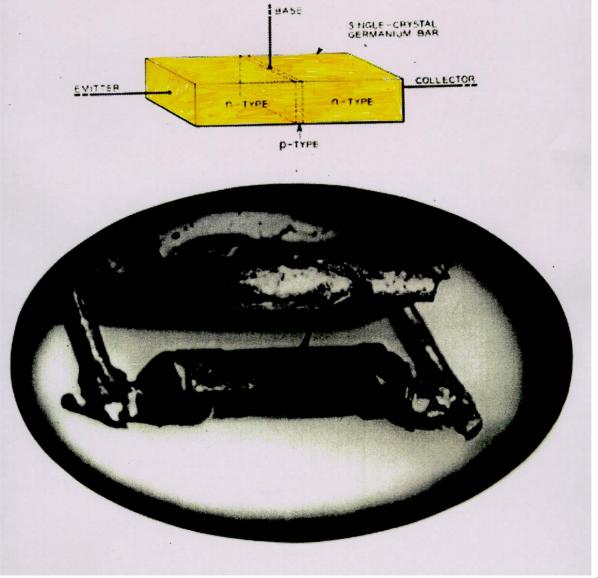

- First bipolar junction transistor (n-p-n) achieved in single crystal Ge (grown-junction technique) by Shockley, Sparks and Teal in '51 – three years after discovery of transistor action by Bardeen and Brattain

35

#### **Bipolar Junction Transistor (Implementation)**

- Jun 26 '48 Shockley's p-n junction / p-n junction transistor theoretical analysis ("347" patent filed)

- Apr 7 '49 Sparks / Mikulyak "existence proof" Ge p-n-p (non-colinear) transistor (power gain ≤ 16)

- Jul '49 Shockley's extended p-n junction / p-n junction transistor theory published (Bell Syst. Tech. J.)

- Apr '50 Teal/Buehler/Sparks single crystal research and fabrication of grown p-n junction and (double-doping) n-p-n largearea junction transistor (10-15 watts audio power ≤ 20 Kc)

- Jan '51 Korean war stimulated fabrication of n-p-n microwatt junction transistor (proximity fuse)

- Jul '51 Shockley, Sparks and Teal microwatt n-p-n junction transistor published (Phys. Rev.)

SFMATEC

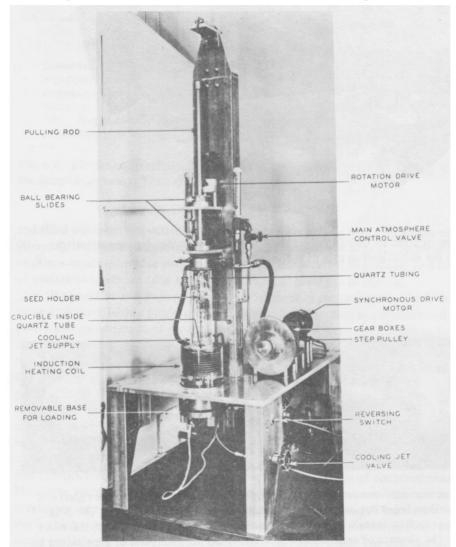

#### Type II Crystal-Pulling Machine Designed and Made by Teal and Little (ca 1950)

Materials and Processes: Part A: Materials, 3<sup>rd</sup> ed.,(edited by J.F. Young and R.S. Shane,1985) Reprinted with permission of Marcel Dekker, Inc.

#### **Bipolar Junction Transistor (Implementation)**

#### **Double-Doping Growth: N-P-N Large Area Junction Transistor**

After Morgan Sparks et al. (courtesy Michael Riordan)

#### **Bipolar Junction Transistor (Implementation) Microwatt Junction Transistor (July 4, 1951)**

After Michael Riordan

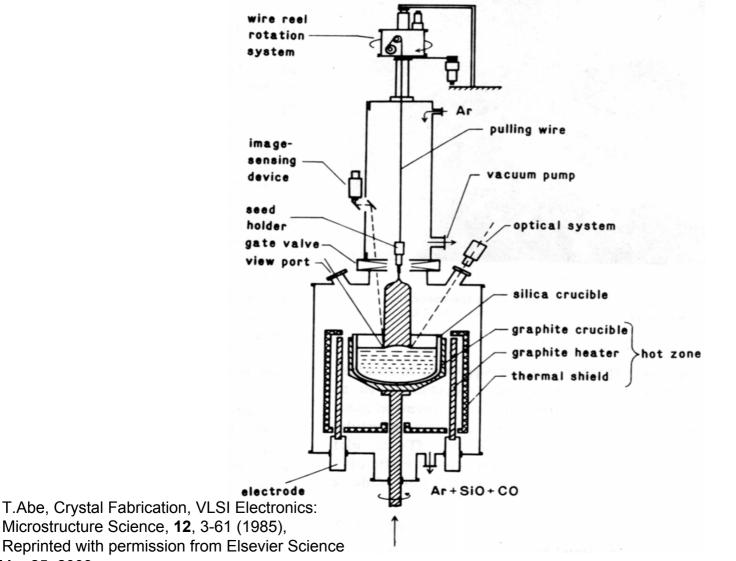

#### Schematic Illustration of Typical Czochralski Puller With Hot Zone, Automatic Optical and Image Sensing Diameter Controls and Wire Reeling System

INTERNATIONAL

40

SeMa1

#### Single- Crystal Pulled From Melt (150 mm Diameter, {100} Orientation)

Courtesy of Gerry Moore

#### **Ken Benson**

#### Takao Abe

Mar 25, 2003

2003 International Conference on Characterization and Metrology for ULSI Technology

### Wilfred von Ammon

Mar 25, 2003

2003 International Conference on Characterization and Metrology for ULSI Technology

# **Bob Falster (I) and Vladimir Voronkov (r)**

INTERNATIONAL SEMATECH 45

### **Bob Brown**

### Dopant Distribution During Single-Crystal Growth

- Normal freezing described by zone-refining technique

- $-C_{s}(g) = k_{e}C_{I}(1-g)^{[ke(dl/ds)-1]}$

- Bill Pfann 1952

- $-k_e = k_o [k_o + (1-k_o) exp (-f \delta / D)]^{-1}$

- Burton-Prim-Slichter 1953

- k<sub>o</sub>, equilibrium distribution coefficient, related to effective distribution coefficient, k<sub>e</sub>, dependent on particulars of equipment and pulling specifics

- Kenji Morizane, Gus Witt and Harry Gatos later realized the crystal growth rate, *f*, was microscopic crystal growth rate

- Extensive summary of k<sub>o</sub> and equilibrium solubilities in Ge and Si tabulated by Forrest Trumbore

### **Bill Pfann**

H.R.Huff,J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

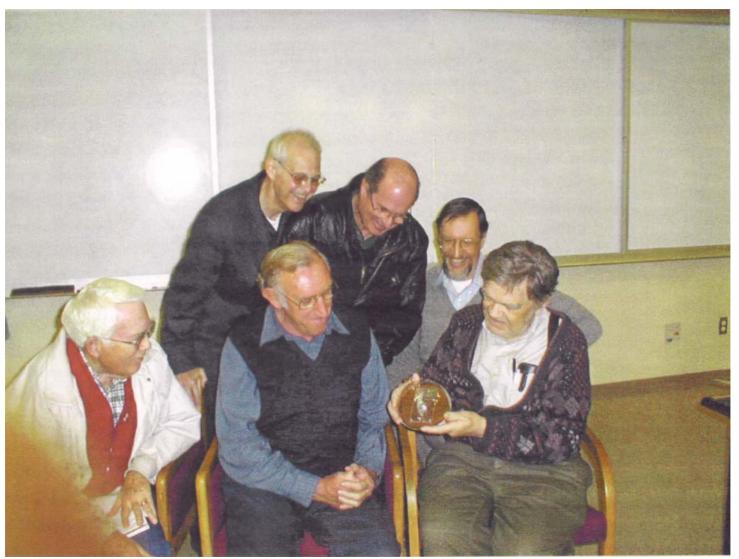

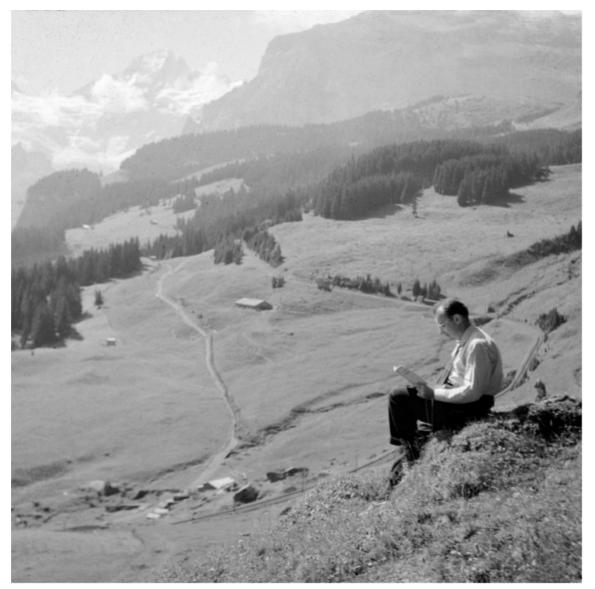

#### Harry Gatos (leading chamber-music quartet)

H.R.Huff,J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

INTERNATIONAL SEMATECH 49

### Walt Runyan

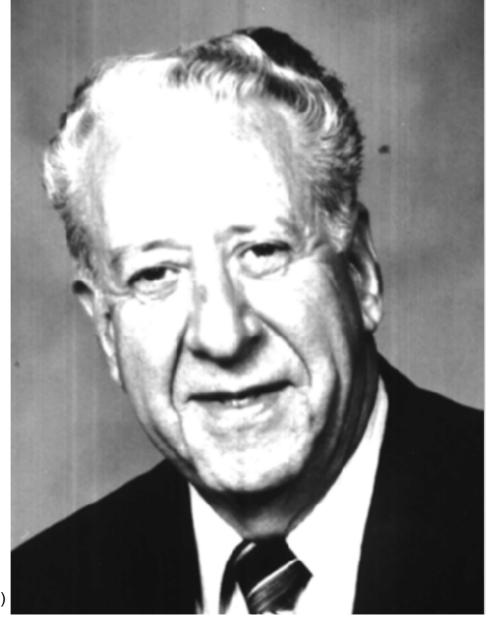

### **Forrest Trumbore**

H.R.Huff,J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

Mar 25, 2003

2003 International Conference on Characterization and Metrology for ULSI Technology

# **Oxygen in Silicon**

- Innocuous observation that silicon crystals grown by Teal-Little, pulled (or inappropriately, but conventionally the CZ technique after Jan Czochralski) contains ppma concentrations of oxygen

- Dissolution of quartz crucible by molten silicon

- Resulted in extensive scientific literature and gettering methodologies for denuded zone formation

- Optimize device performance, yield and reliability

### **Bruce Hannay**

H.R.Huff,J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

### **Ron Newman**

INTERNATIONAL SEMATECH 54

Mar 25, 2003

2003 International Conference on Characterization and Metrology for ULSI Technology

# Agenda

- Introduction

- Threshold events

- Transistor Fabrication

- Point-contact

- Grown-junction

- Alloy formation

- Diffusion

- Mesa and planar advances

- Integrated circuit beginnings

- Bipolar and DRAM IC Issues

- (1960-1980's)

- Prognosis

- Acknowledgements

Mar 25, 2003

2003 International Conference on Characterization and Metrology for ULSI Technology

# **Double-Doping Technique (1951)**

- Pellets of Ga and Sb were sequentially (and rapidly) added to melt during growth of n-type Ge (Teal et al. - 1951)

- Rate-growth technique of Hall introduced in 1952 and Bridgers and Kolb - 1955

- Based on variation of incorporation of acceptor or donor impurities into solidifying Ge crystal with crystal growth rate, forming both p-n junctions and n-p-n transistors

- Commercially grown-junction Si transistor introduced by Teal in 1954, subsequently described by Adcock in conjunction with Jones and colleagues

- Experimental Si transistor previously announced in 1950 by BTL

- Tannenbaum and co-workers reported in 1955 additions of Ga and Sb dopants for growth of Si crystals containing up to five n-p-n regions suitable for production of grown-junction Si transistors

INTERNATIONAL

SEMA

### **Bob Hall**

H.R.Huff,J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

### **Willis Adcock**

H.R.Huff,J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

#### **Point-Contact vs Grown-Junction Transistors**

- Grown-junction Ge transistors improvements overtook point-contact transistors in early fifties

- Larger current handling capability

- Less junction noise

- Improved techniques to control base width

- Resulted in increased frequency response

- Eventually, Si replaced Ge

- Higher temperature operation (300°C)

- Lower reverse current

- Increased power output

- Stable oxidized surface of Si compared to Ge

- Si small-area diodes replaced Ge point-contact by about 1960

- Si diodes first reported in 1952 by Pearson in conjunction with Sawyer and Foy via Al doped (p-type) wire alloyed to n-type Si material

SEN

59

#### Celebrating the Point-Contact Transistor - 2000 (Gerald Pearson's 1973 Replica of 1947 Structure)

Courtesy of Jim Harris Mar 25, 2003 2003 International Conference on Characterization and Metrology for ULSI Technology

## **Alloy Transistors**

- Saby developed Ge alloy transistor in 1952 as did Law and colleagues, building on Hall's research

- Process described, in retrospect, as crystal dissolution and regrowth at 600°C on {111} (local liquid phase epitaxy)

- Recrystallized Ge incorporated In thereby converting to p-type

- Achievement of precise and narrow width difficult due to precise control of temperature and diffusion from both surfaces

- Maximum cut-off frequency of alloy Ge p-n-p transistor typically 10 MHz while point-contact Ge transistor typically up to 50 MHz

- Nevertheless, Ge alloying (because of its presumed simplicity) readily implemented as manufacturable process and became widely utilized compared to more uncontrollable base widths for grown-junction devices for transistors in Ge and Si for many years

- Si n-p-n alloy transistor quite difficult to fabricate due to process variability and never commanded significant market position

- {111} surface preferred for alloy bipolar transistor gave way to {100}surface for MOS transistor in 1968 due to lower concentration of Si- SiO<sub>2</sub> interface states

61

Mar 25, 2003

2003 International Conference on Characterization and Metrology for ULSI Technology

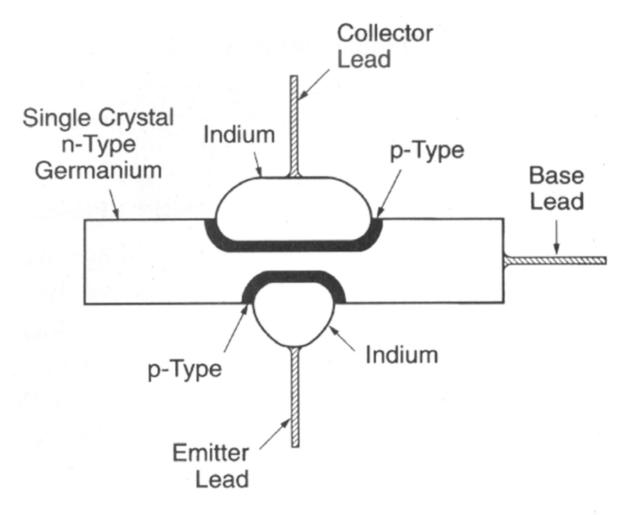

#### **Schematic Illustration of Alloy Transistor**

p-n-p Alloyed Germanium Junction Transistor

Ian M. Ross, *The Invention of the Transistor*, Proc. IEEE, **86**, 7-28 (1998) Reproduced by permission of the IEEE, Inc.

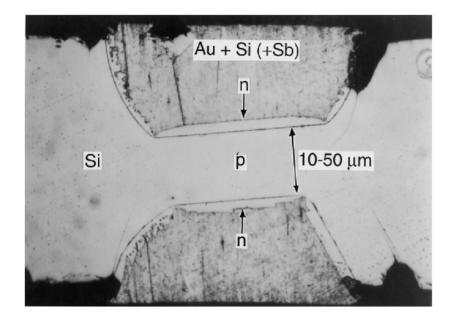

# **Alloy Transistors**

Silicon n-p-n alloyed transistor (1954) made with Au(+Sb) alloyed emitter and collector regions (D.K. Wilson, BTL, 1954). N-type emitter and collector regions regrown from Au +Si (+Sb) alloy marked with arrows. Note large base (p-type) thickness, hard to control from two sides – two references

N. Holonyak, ULSI Process Integration III, ECS PV 2003-06 (2003)

Au + Si (+Sb)

Magnified view of alloyed n-p-n transistor showing base thickness of  $\approx$  2.5  $\mu$ m, which, because of two reference surfaces (top and bottom and thick crystal and thick alloy) is difficult to achieve and to reproduce.

# Alloy Transistors (con't)

- Alloy junctions exhibit abrupt emitter-base step junction while grown-junction are graded

- Ge alloy transistors thereby exhibited higher alpha cutoff frequency (f<sub>c</sub>) range (5-10 MHz) compared to grownjunction transistors (1-10 MHz)

- Abrupt base-collector junction for alloy transistor, however, resulted in higher capacitance per unit area, tending to limit high-frequency response

- Although point-contact Ge transistor  $f_c \Rightarrow 50$  MHz, grown-junction and alloy-junction devices dominated mass production into late 1950's

INTERNATIONAL

### **Diffused Bipolar Transistors**

- Double-doping and rate-growth crystal techniques critical to proving out junction transistor theory

- Junctions physically inside crystal and p-type base layer thicker and less uniform than desired

- Solid-state diffusion ( $\sqrt{Dt}$ ) patent filed by Theurerer in 1951

- Implemented in 1954 by Pearson and Fuller

- In-diffusion of impurities in controlled ambient over whole semiconductor wafer (≈ 1 inch diameter)

- Fuller described donors and acceptors in Ge (1952) and Fuller and Ditzenberger – donors and acceptors in Si (1954)

- Solid-state-diffusion processes fabricated in mesa structure for n-p-n and p-n-p transistors in mid-1950's

- Tannenbaum and Thomas utilized simultaneous diffusion of both acceptor (base) and donor (emitter) in fabrication of Si transistor in 1956

### **Diffusion Issues**

- Advent of diffusion process transferred f<sub>c</sub> limitation from base to collector

- Higher collector resistivity, compared to emitter and base, led to significant collector series resistance, coupled with collector capacitance, limited frequency response

- Reduced collector resistivity increased base-junction capacitance and lowered breakdown voltage inasmuch as base resistivity also decreased to reduce base resistance

- Small base width required to reduce transit time

- Early's concept of p-n-i-p design modification suggested f<sub>c</sub> values as high as 3 GHz, with experimental values of 95 MHz realized, although diffusion from both surfaces resurrected control of base width

- Early also introduced concept of heavily-doped thin base such that portion of reversed base-collector space charge penetrated into base, thereby reducing transistor transit time

SEMAT

### **Epitaxial Fabrication**

- Solution to p-n-i-p or n-p-i-n structure obtained by fabrication of lightly doped layer of silicon on heavily doped silicon substrate (epitaxial fabrication)

- Theurerer and colleagues (1960) expanded Murphy's localized, high-concentration sub-collector diffusion in lightly doped Si substrate

### Ken Bean

H.R.Huff,J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

### Technology Evolution For Controlled Base Width Transistors

| Technology                     | Author                               | Approximat<br>e Year | Reference |

|--------------------------------|--------------------------------------|----------------------|-----------|

|                                |                                      |                      |           |

| Double-<br>doping              | Teal                                 | 1951                 | 64        |

| Rate-grown                     | Hall                                 | 1952                 | 123-125   |

| Alloy                          | Hall                                 | 1950                 | 138,139   |

| Electroche<br>mical<br>thinned | Tiley and<br>Williams                | 1953                 | 146       |

| Diffased<br>base               | Pearson<br>and Fuller                | 1954                 | 150       |

| P-N-I-P<br>(N-P-I-N)           | Early                                | 1954                 | 163       |

| Planar<br>process              | Hoerni                               | 1960                 | 12        |

| Epitaxy                        | Teal,Sangster<br>, Mark,<br>Theuerer | 1954, 1957-1960      | 166-169   |

Mar 25, 2003

2003 International Conference on Characterization and Metrology for ULSI Technology

INTERNATIONAL

69

SEMATEC

# Agenda

- Introduction

- Threshold events

- Transistor Fabrication

- Point-contact

- Grown-junction

- Alloy formation

- Diffusion

- Mesa and planar advances

- Integrated circuit beginnings

- Bipolar and DRAM IC Issues

- (1960-1980's)

- Prognosis

- Acknowledgements

Mar 25, 2003

2003 International Conference on Characterization and Metrology for ULSI Technology

## **Frosch and Derrick**

- Holonyak's work on diffused-base alloyed emitter p-n-p transistors and p-n-p-n thryistors required redistribution "drive-in" of donor impurity typically in H<sub>2</sub> at  $\geq$  1100°C

- Wafer surface would invariably be eroded, pitted or destroyed but a colored oxide was observed by Frosch - Spring, 1955

- Holonyak converted Frosch diffused Si n-p-n into working p-n-p-n thryistor

N. Holonyak, ULSI Process Integration III, ECS PV 2003-06 (2003)

### Frosch and Derrick (con't)

- Frosch and Derrick switched from dry-gas (typically  $N_2$  or  $H_2$ ) impurity diffusion ambient to wet ambient ( $H_2$ ) vapor + carrier gas) diffusion due to exhaust  $H_2$  igniting and flashing-back into diffusion chamber (because of gas flow fluctuations), causing  $H_20$  to cover, react with and protect Si wafer with oxide

- Wet ambient created a protective oxide on Si, which could be selectively removed for gaseous diffusion into bare regions, which could then be resealed with oxide for higher temperature anneals of further diffusion

- Only Ga was found to penetrate SiO<sub>2</sub> protective oxide

- Process so flexible that planar n-type regions of any desired pattern could be prepared on p-type substrate (or vice-versa)

#### All other procedures were immediately rendered obsolete

N. Holonyak, ULSI Process Integration III, ECS PV 2003-06 (2003)

## Frosch and Derrick (con't)

#### Frosch noted

- "In addition to possibilities of process simplification, protective quartz envelope added during heating may be useful for protecting an electrical device from atmospheric conditions

- Device might prove more stable if left enclosed in such a quartz envelope

- However, may not be possible to make all necessary electrical contacts through quartz

- Some protection may be retained by removal of small area of envelope for application of contacts

INTERNATIONAL

73

SEM

N. Holonyak, ULSI Process Integration III, ECS **PV 2003-06** (2003); C.J. Frosch and L. Derick, BTL Memorandum #55-113-23 (June 14, 1955)

### **Calvin Frosch**

Courtesy of Nick Holonyak

## Moll and Holonyak at BTL (1954-1955)

- Moll and Holonyak now had available all critical elements for fabrication of Si transistors

- Oxidation

- Diffusion

- Photolithography

- Aluminum metallization

- Thermocompression bonding

N. Holonyak, ULSI Process Integration III, ECS PV 2003-06 (2003);

## John Moll

### **Nick Holonyak**

H.R.Huff,J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

## **Nick Holonyak and John Bardeen**

Courtesy of Lillian Hoddeson

### Bardeen, Kikuchi and Holonyak An Enduring Friendship

Courtesy of Lillian Hoddeson

Mar 25, 2003

2003 International Conference on Characterization and Metrology for ULSI Technology

INTERNATIONAL

SEMATECH

## Silicon – Silicon Dioxide Interface

Holonyak noted "remove the oxide, say it doesn't exist, and then what would there be? Silicon itself is, of course, the critical ingredient followed by its unique natural oxide. In some sense it could be said that Si and its technology (its oxide) "invented" the IC"

Nick Holonyak, ULSI Process Integration III, ECS PV 2003-06 (2003)

## Silicon – Silicon Dioxide Interface

Si-SiO<sub>2</sub> diffusion technology, transferred from AT&T's Bell Telephone Laboratories (BTL) to Shockley Semiconductor and, therefore, to Fairchild Semiconductor Corporation led to phenomenon of "Silicon Valley" and creation of the IC industry

Nick Holonyak, ULSI Process Integration III, ECS PV 2003-06 (2003)

## **Fairchild Semiconductor Corporation**

- Shockley Semiconductor's original goal (1955) was fabrication of double-diffused transistors before Shockley re-directed effort to p-n-p-n diodes

- Blank, Grinich, Hoerni, Kleiner, Last, Noyce, Moore and Roberts departed in 1958 from Shockley Semiconductor and formed Fairchild with goal of

- Fabrication of double-diffused transistors for commercial gain

- Major stimulus to invention of planar transistor, Silicon Valley and development of fledgling electronics industry

INTERNATIONAL

Sen

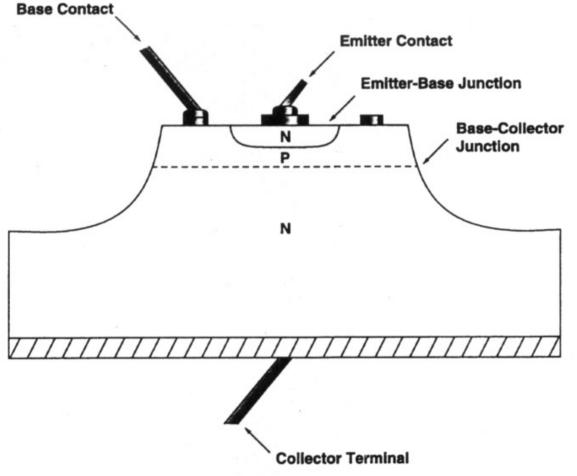

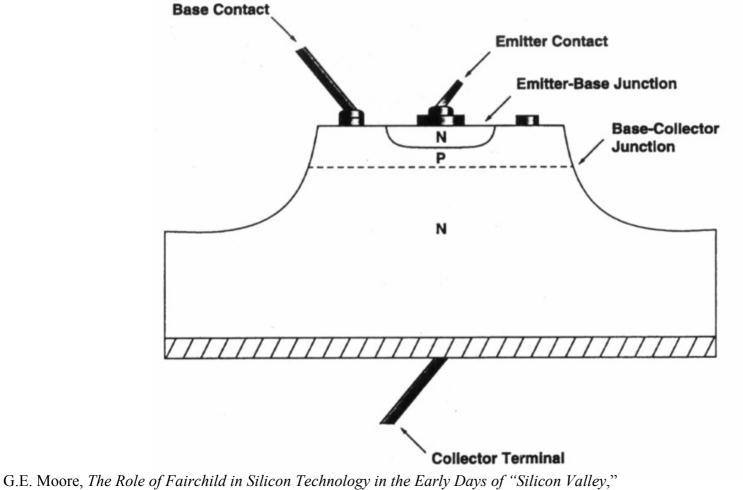

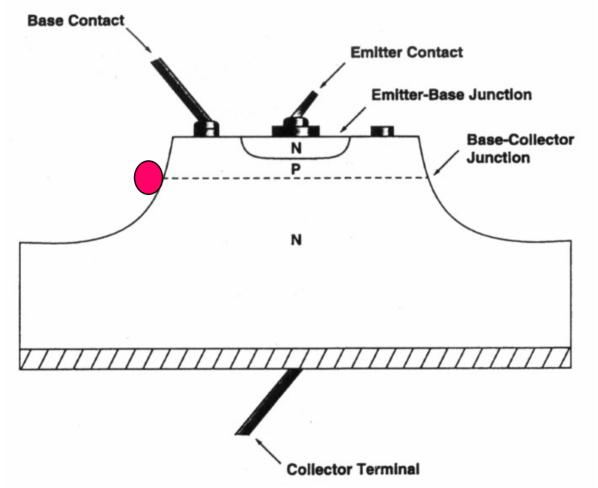

#### Schematic Cross-Section of Early Mesa Transistor Made by Fairchild Semiconductor Corporation

INTERNATIONAL

83

SEMA

G.E. Moore, *The Role of Fairchild in Silicon Technology in the Early Days of "Silicon Valley,*" Proc. IEEE, **86**, 53-62 (1998) Reproduced by permission of the IEEE, Inc.

## **Mesa Transistor**

- Utilized dopant diffusion with Frosch and Derrick's oxide masking and photolithographic technique

- Removal of portion of top of semiconductor wafer mesa structure – reduced p-n junction area and depletion capacitance and achieved desired f<sub>c</sub>

- Device fabrication at planar surface with several tenths  $\mu \textbf{m}$  base widths and increased  $\textbf{f}_{c}$

- Many devices fabricated on Ge or Si wafer concurrently with rather similar characteristics

- Less expensive to fabricate mesa transistor compared to grown-junction or alloy transistors

- Cumulative process experience (i.e., learning curve) Haggerty

INTERNATIONAL

All methods prone to excessive leakage currents

## Jean Hoerni / Fairchild

- Attala and colleagues (1959) showed that SiO<sub>2</sub> grown under clean and controlled conditions, on properly cleaned Si wafer, would lead to reduction of surface states and passivation of Si surface

- Hoerni pulled all strands together for fabrication

of planar Si transistors and diodes (1960)

- SiO<sub>2</sub> masking layer utilized for

- Fabrication of diffused Si transistors

- Left in place for passivation of p-n junctions intersecting surface for grown-junction, alloy and diffused mesa transistors, without necessity of growing passivating oxide under meticulously clean conditions

- Ensured dielectric layer for supporting metallic conductor overlayers in IC era

Silicon Dioxide: Prototypical Gate Dielectric

- Passivates silicon surface and p-n junctions intersecting surface

- $D_{it} \approx 1 3 \times 10^{10} (eV-cm^2)^{-1}$

- Patternable mask for localized diffusion of commonly utilized dopants in silicon for p-n junction fabrication

- Amorphous, blocking layer

- Insulator (9 eV)

- Affords convenient material for deposition of adherent, conducting films connecting various device components, separating metallic conductor films from silicon

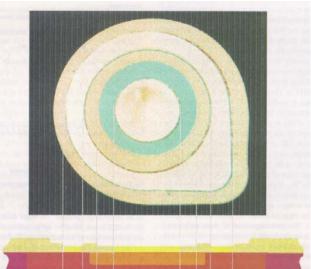

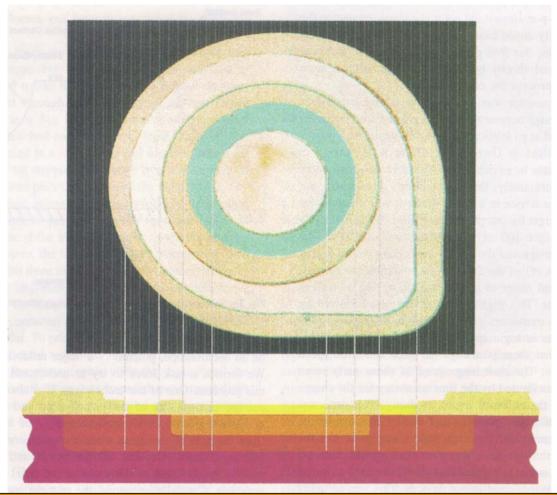

#### **Photomicrograph of First Planar Transistor**

#### • Diameter of circle forming most of outside ring is 0.030 in. Light areas are aluminum emitter and base electrodes.

(From "A Solid State of Progress," Fairchild Camera and Instrument Corporation, 1979)

G.E. Moore, *The Role of Fairchild in Silicon Technology in the Early Days of "Silicon Valley,*" Proc. IEEE, **86**, 53-62 (1998) Reproduced by permission of the IEEE, Inc.

#### Schematic Cross-Section of Early Mesa Transistor Made by Fairchild Semiconductor Corporation

Proc. IEEE, **86**, 53-62 (1998) Reproduced by permission of the IEEE, Inc.

#### Schematic Cross-Section of Early Mesa Transistor Made by Fairchild Semiconductor Corporation

Adapted from G.E. Moore, *The Role of Fairchild in Silicon Technology in the Early Days of "Silicon Valley,"* Proc. IEEE, **86**, 53-62 (1998)

## Jean Hoerni / Fairchild (con't)

- Moore noted mesa transistor configuration

- Regions of high electric field where junction comes to surface sensitive to contamination

- Emitter-base junction exposed on top surface between metal contacts decreases transistor gain

- Base-collector junction intersects mesa sides, decreases breakdown voltage and modifies leakage characteristic

- Source of low breakdown voltage correlated to localized light emission from side of mesa

- Particle observed on mesa side where light originated

- Particle believed attracted to region's high electric field where junction intersected surface, inducing premature junction breakdown

- Removal of particle restored device characteristics

## Jean Hoerni / Fairchild (con't)

- Planar process introduced extreme flexibility in fabrication of junction transistors

- "Tooling up" to fabricate different devices involved changing mask set, diffusion profiles and doping levels in conjunction with starting Si wafer's resistivity

- Planar process facilitated fabrication of doublediffused transistor essentially planar with original wafer surface, without necessity of mesa structure

- Cut-off frequences of 10 GHz achieved, ⇒ values for vacuum tubes

### Modern Silicon MOSFETs

- 1955: Ross's patent utilized ferroelectric as gate dielectric

- 1957: Wallmark FET patent ٠

- **1959: Weimer thin-film FET utilized CdS as gate** ulletdielectric

- 1959: Atalla et al. proposal of thermally grown SiO<sub>2</sub> as gate dielectric and stabilization of silicon surface

- 1960: Ligenza and Spitzer proposal of high-pressure steam oxidation of silicon

- **1960: Kahng and Atalla's description of NMOSFET in** • patents / literature

INTERN

• 1963: Hofstein and Heiman's (MOSFET) IGFET SFM^

# Agenda

- Introduction

- Threshold events

- Transistor Fabrication

- Point-contact

- Grown-junction

- Alloy formation

- Diffusion

- Mesa and planar advances

- Integrated circuit beginnings

- Bipolar and DRAM IC Issues

- (1960-1980's)

- Prognosis

- Acknowledgements

Mar 25, 2003

2003 International Conference on Characterization and Metrology for ULSI Technology

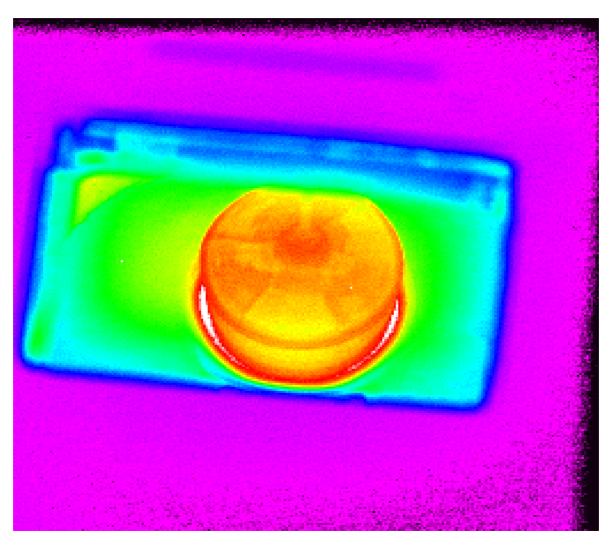

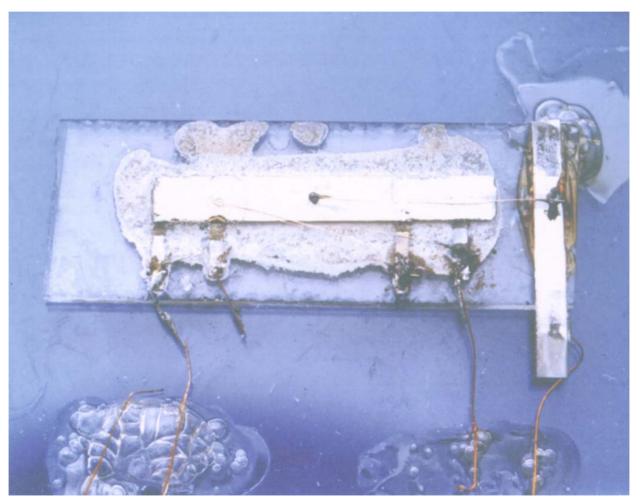

#### First Integrated Circuit, a Phase Shift Oscillator Fabricated in Ge, Using Mesa Process, Invented by Jack S. Kilby of Texas Instruments in 1958

Courtesy of Texas Instruments, Inc.

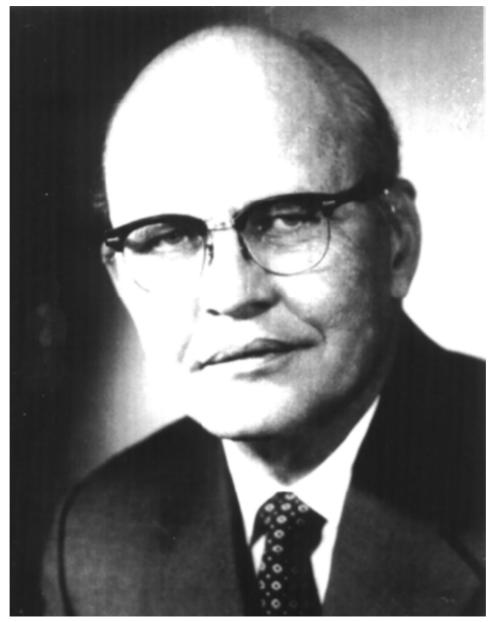

### **Jack Kilby**

2003 International Conference on Characterization and Metrology for ULSI Technology

Mar 25, 2003

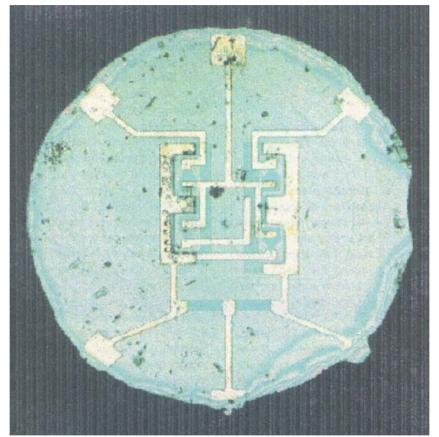

#### Photomicrograph of One of First Planar Integrated Circuits Fabricated in Si at Fairchild in 1959

Some of the aluminum interconnection metal has been damaged during etching operations to form a circular chip of silicon to plane into a transistor can modified to have more leads. (From "A Solid State of Progress," Fairchild Camera and Instrument Corporation, 1979)

G.E. Moore, *The Role of Fairchild in Silicon Technology in the Early Days of "Silicon Valley,"*Proc. IEEE, **86**, 53-62 (1998) Reproduced by permission of the IEEE, Inc.

Mar 25, 2003 International Conference on Characterization and Metrology for ULSI Technology

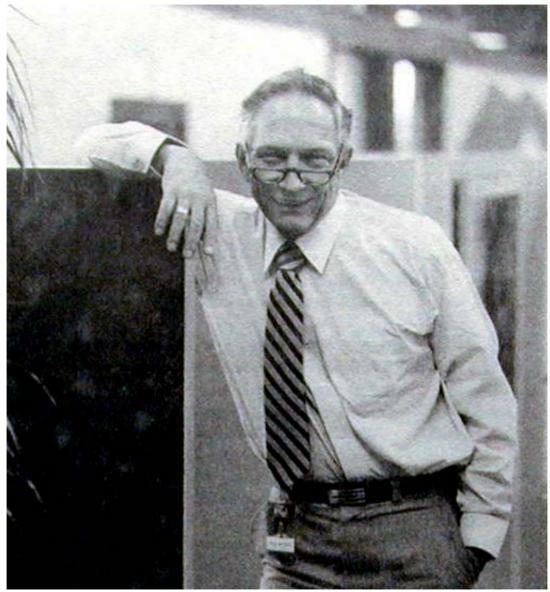

## **Bob Noyce**

Courtesy of Intel Corporation

## **Integrated Circuit Beginnings**

- Critical difference between two patents (i.e., interconnection of elements) clarified by Runyan and Bean

- Kilby noted "... electrically conducting material such as gold may then be *laid down* (italics entered by author) on the insulating material to make the necessary electrical connections"

- Noyce noted "... an electrical connection to one of said contacts comprising a conductor adherent to said layer (italics entered by author)..."

SEM

Disagreement centered around whether "laid down" was equivalent to "adherent to"

## **Integrated Circuit Beginnings (con't)**

- Probably most balanced assessment of Kilby's and Noyce's relative contributions is contained in citations of Franklin Institute's 1966 Ballantine Medal award, which Kilby and Noyce shared (Runyan and Bean)

- Kilby credited for "conceiving and constructing the first working monolithic circuit in 1958," and Noyce for 'his sophistication of the monolithic circuit for more specialized use, particularly in industry" (Runyan and Bean)

- Kilby noted great strength of IC concept was it drawed on mainstream efforts in progress for semiconductor industry

- Because of commonality with existing processes, ICs rapidly moved into production status

- MOSFET IC revolution really exploded in 1973 when IBM chose n-channel Si MOSFET instead of slower p-channel for mainframe memory computer (IBM-370/158)

SFMAT

## **Pervasiveness of Microelectronics Revolution**

- Learning curve (Haggerty)

- Market elasticity (1960's ...)

- Moore & device scaling (Dennard –1968 -1T/1C DRAM cell)

- Moore's Law

- Number of transistors per chip doubles every year (1965)

- Technology: Feature reduction

- Design: Reduction in number of transistors per memory cell from 6 (SRAM) to 1.5 (DRAM)

100

- Number of transistors per chip doubles every two years (1975)

- Technology: Feature reduction

- Design: No more reduction in transistors per memory cell possible. Benefits derived only from improvements in layout

- Industrial concern in mid '90s as regards fab economic constraints might reduce return on capital investment

- Int'l Technology Roadmap for Semiconductors (ITRS)

- Focus to ensure Moore's law by realizing the roadmap

- Expansion of economy (GWP) market elasticity (2000's) accommodates IC CAGR

## Pat Haggerty (left)

Courtesy of Fred Seitz

### **Gordon Moore**

Mar 25, 2003

2003 International Conference on Characterization and Metrology for ULSI Technology

## Agenda

- Introduction

- Threshold events

- Transistor Fabrication

- Point-contact

- Grown-junction

- Alloy formation

- Diffusion

- Mesa and planar advances

- Integrated circuit beginnings

- Bipolar and DRAM IC Issues

- (1960-1980's)

- Prognosis

- Acknowledgements

Mar 25, 2003

2003 International Conference on Characterization and Metrology for ULSI Technology

#### Partial List Bipolar and DRAM IC Issues (1960-1980's)

- **Deal and Grove** oxidation kinetics

- Hess, Irene, Massoud, Raider, Williams, Revesz, Schnable

- Snow, Grove, Deal and Sah device reliability and Na contamination in SiO<sub>2</sub>

- Balk surface state passivation

- Dalton and Dorbek Si<sub>3</sub>N<sub>4</sub> overlayer seal against Na

- Kerr and Young utilization of PSG deposited on top of SiO<sub>2</sub> to getter Na and K and stabilize SiO<sub>2</sub>

- Snow, Deal, Balk and Eldridge threshold voltage shifts induced by polarization in PSG layer could be controlled

#### **Bruce Deal**

H.R.Huff,J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

### **Dennis Hess**

H.R.Huff,J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

Mar 25, 2003

2003 International Conference on Characterization and Metrology for ULSI Technology

#### Partial List Bipolar and DRAM IC Issues (1960-1980's) (con't)

- Else Kooi LOCOS

- Kriegler gettering of Na by HCL in oxidation furnaces

- Osburn Gate oxide integrity (GOI) and reliability via CI methodologies

- Reisman VLSI laboratory proving ground

- Hu, Shiraki and Claeys oxidation induced stacking fault annihilation methodologies

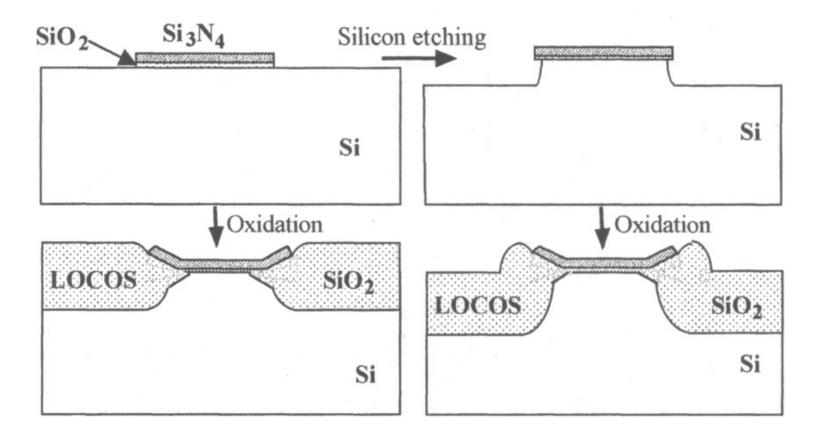

### **Conventional LOCOS Procedures**

Pad oxide (SiO<sub>2</sub>) under nitride oxidation mask relieves stress, but results in formation of "bird's beaks" at oxide edges while fully recessed oxide patterns (right) exhibit complete "bird's heads"

E. Kooi, *The History of LOCOS*, Semiconductor Silicon/1998, ECS **PV 98-1**, 200-214 (1998) Reproduced by permission of The Electrochemical Society, Inc.

## **Else Kooi**

H.R.Huff,J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

## **Carl Osburn**

H.R.Huff,J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

## **Arnie Reisman**

H.R.Huff,J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

INTERNATIONAL SEMATECH 111

# **Jimmy Hu**

Mar 25, 2003

## **Cor Claeys**

H.R.Huff,J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

ogy

#### Partial List Bipolar and DRAM IC Issues (1960-1980's) (con't)

- Moll and Termin capacitance-voltage (C-V) analysis

- Grove, Snow, Deal and Sah C-V analysis

- Nicollian and Goetzberger conductance analysis

- Zaininger and Heiman C-V for fab engineers

- Grove and Fitzgerald p-n junction description under non-equilibrium conditions

## **Ed Nicollian**

H.R.Huff,J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

#### Partial List Bipolar and DRAM IC Issues (1960-1980's) (con't)

#### Process Issues

- Wafer Cleaning

- Gold in silicon

- Carrier lifetime

- Plastic deformation

- Point defects / line defects

- Epitaxy

- Wafer design, specifications and diameter

- Gettering

- GOI and related diagnostic procedures

- Silicidation

- Lithography, plasma etch ...

## **Bill Pliskin**

## Werner Kern

H.R.Huff,J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

Mar 25, 2003

## **Marc Heyns**

## **Jerry Ruzyllo**

H.R.Huff,J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

SEMATECH 120

#### **Hans Queisser**

INTERNATIONAL SEMATECH 121

## **Gunther Schwuttke**

H.R.Huff,J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

## **Jim Amick**

H.R.Huff, J. Electrochem. Soc., 149, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

Mar 25, 2003

**SEMATECH** 2003 International Conference on Characterization and Metrology for ULSI Technology

INTERNATIONAL

123

## **Ted Kamins**

INTERNATIONAL SEMATECH 124

# **W. Murray Bullis**

H.R.Huff,J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

#### **Eicke Weber**

H.R.Huff,J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

## **Bernd Kolbesen**

## **Fumio Shimura**

#### Partial List Bipolar and DRAM IC Issues (1960-1980's) (con't)

- Tan, Gosele, Schroter, Kimerling, Plummer, Fair et al.,

- Point defects

- Line defects

- Huff / Lawrence, Takasu, Richter and colleagues

- Wafer design and gettering methodologies

## **Teh Tan**

## **Ulrich Gosele**

INTERNATIONAL SEMATECH 131

## **Wolfgang Schroter**

SEMATECH 132

Mar 25, 2003

# **Kim Kimerling**

Mar 25, 2003 2003 Inter

## **Jim Plummer**

## **Richard Fair**

H.R.Huff,J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

INTERNATIONAL SEMATECH 135

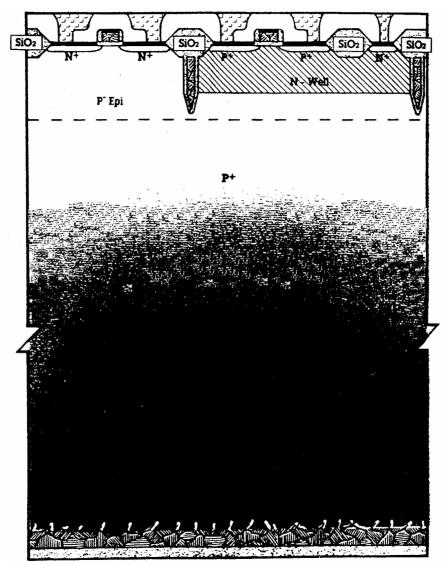

## **Multi-Zone Silicon Wafer**

H.R. Huff, *Silicon Wafer Product Design*, ECS Ext. Abstracts, Abst #775,1105-1106, Fall (1987), reprinted with permission of The Electrochemical Society, Inc.

## **Howard Huff**

H.R.Huff,J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

## Shin Takasu

H.R.Huff,J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

## **Hans Richter**

## **Geofranco Cerofolini**

## George Rozgonyi

H.R.Huff,J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

blogy

## **Phil Tobin**

## **Dieter Schroder**

## **Werner Bergholz**

### Lubek Jastrzebski

## Laszlo Fabry

### **Alain Diebold**

Partial List Bipolar and DRAM IC Issues (1960-1980's) (con't)

- Design Issues

- **Dennard Scaling**

- Design rule reduction

- -Merged 1-T DRAM cell

- -Double polysilicon gate

- -Trench and 3D DRAM storage cell configurations

- Process / design optimization

## **Bob Dennard**

### **Dennard's Generalized Scaling Approach**

| Physical Parameter              | Generalized Scaling<br>Factor    |  |  |

|---------------------------------|----------------------------------|--|--|

| Channel length, L <sub>g</sub>  | 1/α <sub>d</sub>                 |  |  |

| Gate insulator, T <sub>ox</sub> | 1/α <sub>d</sub>                 |  |  |

| Voltage, V                      | ε /α <sub>d</sub>                |  |  |

| Wiring Width                    | 1/α <sub>w</sub>                 |  |  |

| Channel Width, W                | <b>1</b> /α <sub>w</sub>         |  |  |

| Circuit Speed (goal)            | $\alpha_{d}$                     |  |  |

| Circuit Power                   | $\epsilon^2 / \alpha_d \alpha_w$ |  |  |

Following R.H. Dennard in ULSI Science and Technology,

ECS PV 97-3, 519-532 (1997)

## **AI Tasch**

H.R.Huff,J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society, Inc., reproduced with permission)

Mar 25, 2003

## **Jim Meindl**

### **DRAM Process and IC Evolution (circa 1992)**

| Parameter    | Units  | ULSI               | VLSI                 | LSI           | MSI           |

|--------------|--------|--------------------|----------------------|---------------|---------------|

|              |        |                    |                      |               |               |

| Bits/chip    | Number | $10^7 - 10^9$      | $10^5 - 10^7$        | $10^3 - 10^5$ | $10^2 - 10^3$ |

| Design Rule  | μm     | < 1                | 1 - 3                | 3 - 5         | 5 - 10        |

| Power-delay  | PJ     | < 10 <sup>-2</sup> | 10 <sup>-2</sup> - 1 | 1 - 10        | $10 - 10^2$   |

| product      |        |                    |                      |               |               |

| Mask levels  | Number | 15 - 20            | 8-15                 | 6-10          | 5-6           |

| Chip area    | $mm^2$ | 50 - 280           | 25 - 50              | 10 - 25       | 10            |

| Storage cell | (nm)   | 3.5 - 12.5         | 12.5 - 40            | 40 - 90       | 90 - 120      |

| (equivalent  |        |                    |                      |               |               |

| oxide        |        |                    |                      |               |               |

| thickness)   |        |                    |                      |               |               |

| Junction     | μm     | 0.04 - 0.2         | 0.2 - 0.5            | 0.5 - 1.2     | 1.2 - 2       |

| depth        |        |                    |                      |               |               |

Following H.R. Huff, *Silicon: Properties and Material Specifications* in *Concise Encyclopedia* of *Semiconducting Materials & Related Technologies*, edited by S. Mahajan and L.C. Kimerling, Pergamon Press (1992)

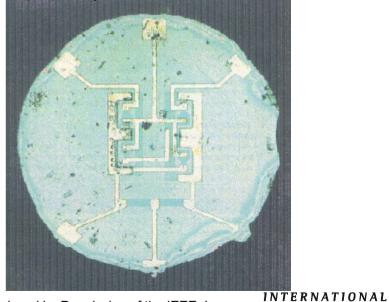

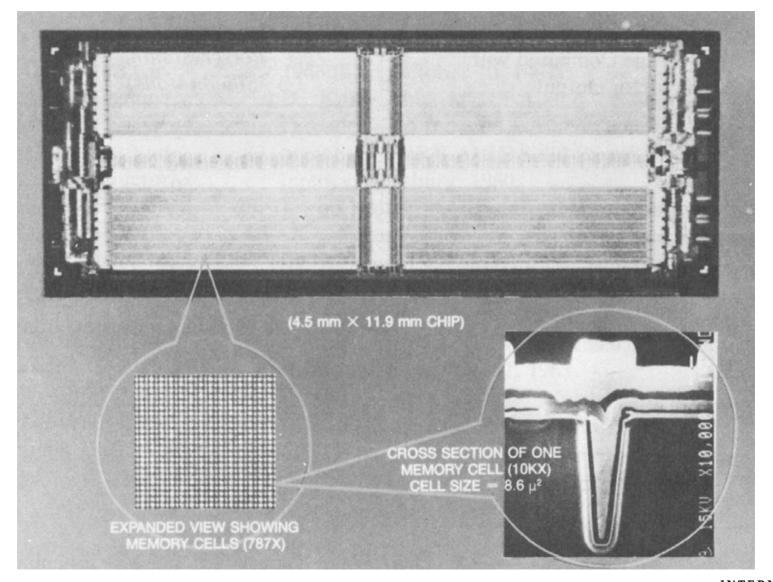

### **One Mbit CMOS DRAM Chip**

Courtesy of Texas Instruments, Inc.

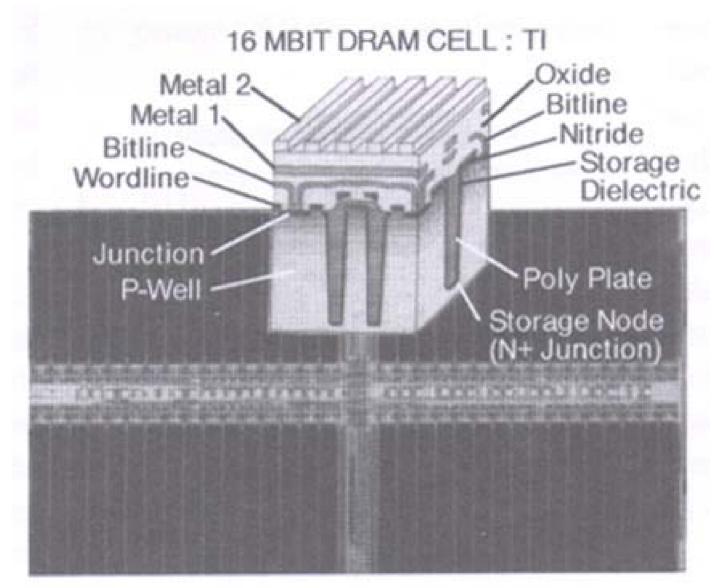

### **16 Mbit DRAM Cell**

Courtesy of Texas Instruments, Inc.

INTERNATIONAL SEMATECH 155

# Agenda

- Introduction

- Threshold events

- Transistor Fabrication

- Point-contact

- Grown-junction

- Alloy formation

- Diffusion

- Mesa and planar advances

- Integrated circuit beginnings

- Bipolar and DRAM IC Issues

- (1960-1980's)

- Prognosis

- Acknowledgements

Mar 25, 2003

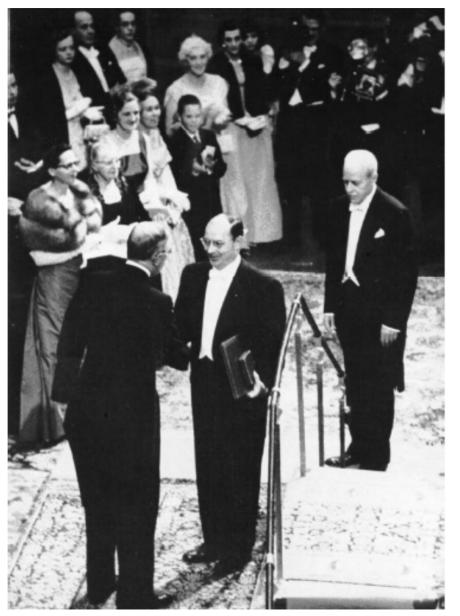

### **1956 Nobel Prize**

Courtesy of Lillian Hoddeson

Microelectronics Revolutionaries –1998 Silicon Symposium Celebrating 50<sup>th</sup> Anniversary of Commercialization of Point-Contact Transistor (Special Historical Session)

H.R. Huff, J. Electrochem. Soc., **149**, S35-S58 (2002) (© The Electrochemical Society Inc., reproduced with permission) Mar 25, 2003 2003 International Conference on Characterization and Metrology for ULSI Technology

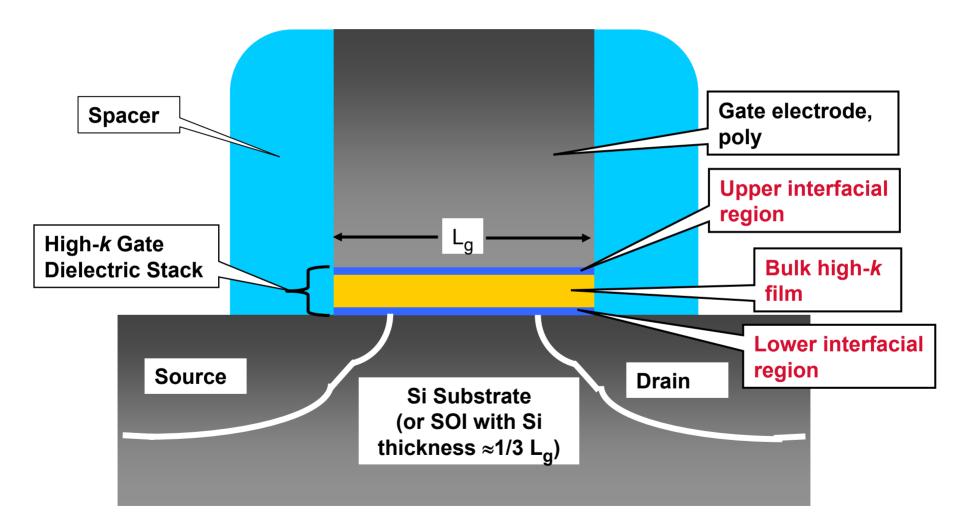

## Simplified Cross-Section of MOSFET Transistor Structure

Modified From P.M. Zeitzoff, R.W. Murto and H.R. Huff, *Solid State Technology*, July 2002

### **Integrated Circuit Historical Scaling Trends**

### • 4K DRAM (1974)

- SiO<sub>2</sub> thickness  $\approx$  75-100 nm

- Channel physical length ( $L_g$ )  $\approx$  7500 nm

- Junction depth  $\approx$  several  $\mu \textbf{m}$

- Power supply = 5 V

- High-performance MPU (2003) ITRS: 100 nm technology generation

- SiO<sub>2</sub> equivalent oxide thickness (EOT)  $\approx$  1.1 1.6 nm

INTERNATIONAL

160

SEN

- Channel physical length ( $L_g$ )  $\approx$  45 nm

- Extension junction depth  $\approx$  25 nm

- Power supply = 1 V

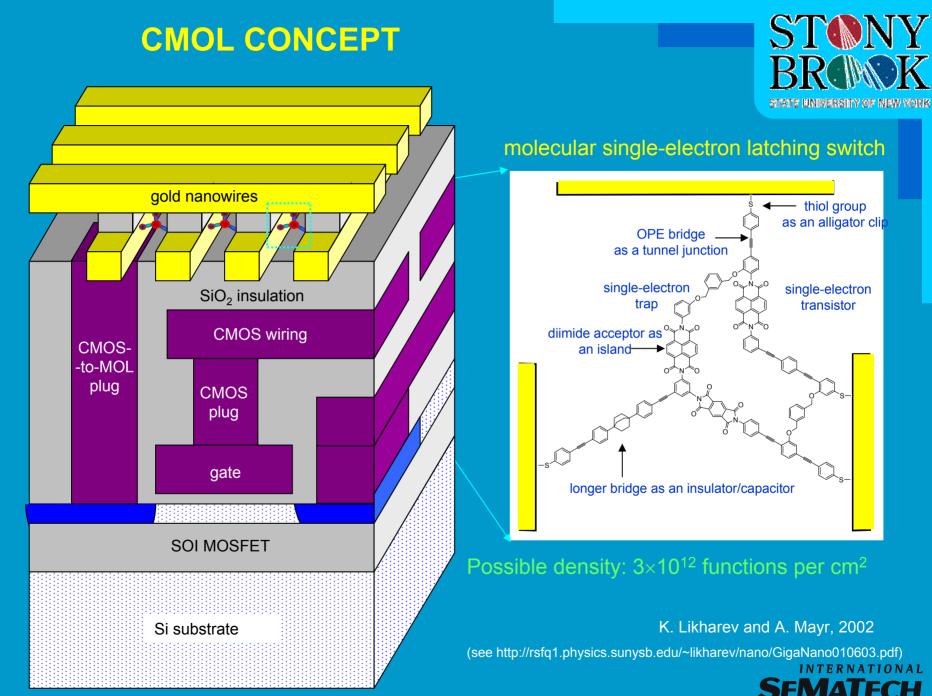

#### Evolving Trends of Alternative Novel Device Structures Beyond CMOS

#### Requirements

- Capability to be integrated with Si-CMOS

- Room-temperature operation

- Capability for SOC, including gigabytes of memory storage

- Portable capability, with opportunity for large-scale market

#### Examples (non-ranked)

- Opto-electronic system (with multi-layered epitaxial structures)

- Spintronics

- Self-assembled nanostructures (including molecular structures)

- Nanowire arrays

- Microclusters/quantum dots in "SiO<sub>2</sub>" (in higher-dimensional matrix)

- Carbon nanotubes

- Cellular automata

- Fullerenes

- Single-electron structures

- Optical computers

- DNA computers

- Quantum computers

Mar 25, 2003

Mar 25, 2003

2003 International Conference on Characterization and Metrology for ULSI Technology

162

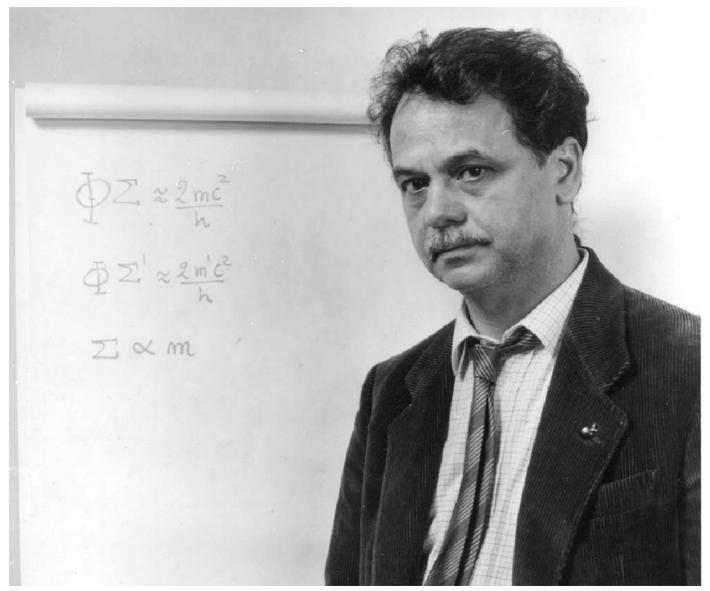

### **MOSFETS Below 10 nm: Quantum Theory** Konstantin K. Likharev – NanoMES 2003<sup>\*</sup> – Tempe, AZ

- "Room-temperature devices with gate length (L<sub>g</sub>) as short as 5 nm still have high transconductance and relatively small DIBL effects and thus may be suitable for nearly all digital applications. Moreover, transistors with L<sub>g</sub> as small as 2.5 nm may still feature voltage gain above unity and hence may be the basis for digital electronics

- However, all characteristics of such devices are extremely sensitive to very small variations of their geometrical parameters (L<sub>g</sub>, T<sub>Si</sub> and T<sub>EOT</sub>) as well as single charged impurities inside (or in the immediate vicinity of the channel)

- As a result of this sensitivity, fabrication of sub-10 nm devices with acceptable yield will require extremely tight specifications, far exceeding recent ITRS projections for the year 2016"

\* To be published in Physica E (2003)

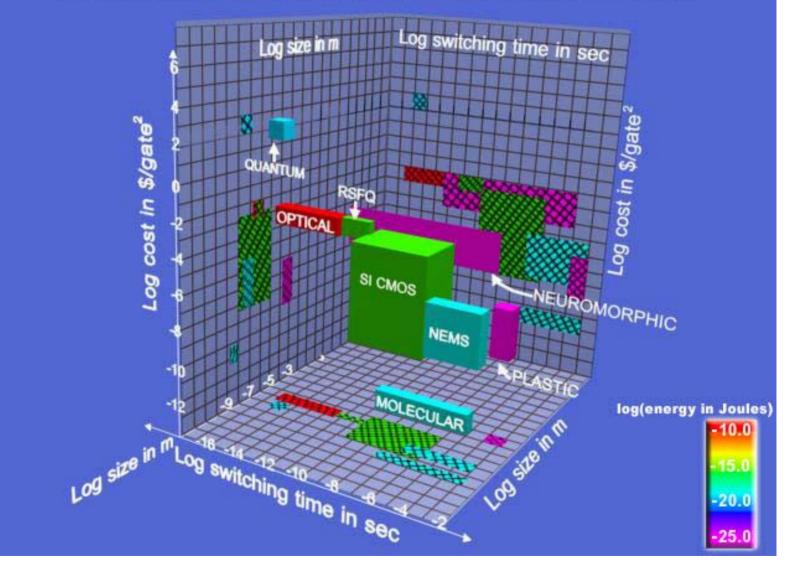

#### **Emerging Technology Parametrization**

Jim Hutchby

Mar 25, 2003 2003 International Conference on Characterization and Metrology for ULSI Technology

SEMATECH

INTERNATIONAL

## **Microelectronics Revolution**

- Gordon Moore (a)

- "But then you see the numbers or hear your company's name on the evening news ... and you are once again reminded that this is no longer just an industry, but an economic and cultural phenomenon, a crucial force at the heart of the modern world"

- Gordon Moore (b)

### – "No exponential is forever: but "forever" can be delayed!"

INTERNATIONAL

165

(a) *Beyond Imagination:Commemorating 25 Years*, SIA (2002) [Introduction by Gordon Moore](b) ISSCC 2003 / Session 1/ Plenary 1.1 (2003)

### **Gordon Moore**

Mar 25, 2003

### **John Bardeen**

Courtesy of Lillian Hoddeson

# Agenda

- Introduction

- Threshold events

- Transistor Fabrication

- Point-contact

- Grown-junction

- Alloy formation

- Diffusion

- Mesa and planar advances

- Integrated circuit beginnings

- Bipolar IC and DRAM IC Issues

- (1960-1980's)

- Prognosis

- Acknowledgements

Mar 25, 2003

# Acknowledgements

- Presentation dedicated To Gordon K. Teal (1907-2003)

- We are indebted to the numerous industrial, university and government personnel, internationally, who have and continue to contribute to the content and formulation of the IC industry