# Simulating the Dynamic Electrothermal Behavior of Power Electronic Circuits and Systems

Allen R. Hefner, Senior Member, IEEE, and David L. Blackburn, Fellow, IEEE

Abstract-A methodology is presented for simulating the dynamic electrothermal behavior of power electronic circuits and systems. In the approach described, the simulator solves for the temperature distribution within the semiconductor devices, packages, and heatsinks (thermal network) as well as the currents and voltages within the electrical network. The thermal network is coupled to the electrical network through the electrothermal models for the semiconductor devices. The electrothermal semiconductor device models calculate the electrical characteristics based upon the instantaneous value of the device silicon chip surface temperature and calculate the instantaneous power dissipated as heat within the device. The thermal network describes the flow of heat from the chip surface through the package and heatsink and thus determines the evolution of the chip surface temperature used by the semiconductor device models. The thermal component models for the device silicon chip, packages, and heatsinks are developed by discretizing the nonlinear heat diffusion equation and are represented in component form so that the thermal component models for various packages and heatsinks can be readily connected to one another to form the thermal network.

## I. NOMENCLATURE<sup>1</sup>

| А                  | Device active area, heat flow area $(cm^2)$ .     |

|--------------------|---------------------------------------------------|

| $A_{\mathrm{fin}}$ | Total heatsink fin area $(cm^2)$ .                |

| $BV_k$             | Junction breakdown voltage coefficient.           |

| с                  | Specific heat (J/cm · K).                         |

| С,                 | Thermal capacitance of node $i$ (J/K).            |

| $C_{cer}$          | Collector-emitter redistribution capacitance (F). |

| $C_{gd}$           | Nonlinear gate-drain capacitance (F).             |

| $D_n$ . $D_p$      | Electron, hole diffusivity $(cm^2/s)$ .           |

| f                  | Forced convection correction factor.              |

| $H_i$              | Heat energy at node $i$ (J).                      |

| $h'_{ m for}$      | Forced convection heat transfer coefficients.     |

| $h'_{\rm nat}$     | Natural convection heat transfer coefficients.    |

| i                  | Discretization indices.                           |

| $I_{bss}$          | Charge control base current (A).                  |

| $I_c$              | Collector current (A).                            |

| $I_{ m ccer}$      | Collector-emitter redistribution current (A).     |

| $I_{\rm css}$      | Charge control collector current (A).             |

| $I_{ m mos}$       | MOSFET channel current (A).                       |

| Imult              | Multiplication current (A).                       |

Manuscript received October 22, 1992; revised July 21, 1993. This paper was presented at the IEEE Workshop on Computers in Power Electronics, Berkeley, CA, August 9–11, 1992.

The authors are with the Semiconductor Electronics Division, National Institute of Standards and Technology, Gaithersburg, MD 20899.

IEEE Log Number 9213644.

$^{\rm I}\,Model$  parameters with subscript I represent temperature coefficients and the sans serif symbols represent computer mnemonics.

Emitter electron saturation current (A). Isn. Anode current (A).  $I_T$ *k*· Boltzmann's constant (J/K). k(T)Thermal conductivity (W/cm · K).  $k_{i,i+1}$ k(T) between nodes i and i + 1 (W/cm · K).  $K_p$ MOSFET transconductance parameter (A/V<sup>2</sup>).  $n_i$ Base intrinsic carrier concentration  $(cm^{-3})$ . Heatsink fin height, orientation parameter (cm).  $P_{\mathrm{fin}}$ Power Total dissipated power(W).  $Q_{gs}$ Gate-source capacitance charge (C).  $Q_{ds}$ Nonlinear drain-source capacitor charge (C). 0 Bipolar transistor base charge (C).  $R_b$ Conductivity modulated base resistance  $(\Omega)$ .  $R_{\rm for}$ Forced convection thermal resistance (K/W).  $R_g$ Gate drive resistance  $(\Omega)$ .  $R_{i,i+1}$ Thermal resistance between  $x_i$  and  $x_{i+1}$  (K/W).  $R_{\rm nat}$ Natural convection thermal resistance (K/W). Cylindrical, spherical radius of node i (cm).  $r_i$  $T_0$ Reference temperature (K).  $T_a$ Ambient temperature (K).  $T_c$ Package case temperature (K).  $T_f$ Heatsink fin temperature (K).  $T_h$ Package header temperature (K).  $T_i$  $T_j$ Temperature at node i (K). Silicon chip surface temperature (K).  $V_a$ Anode-cathode voltage (V).  $V_{aa}$ Anode supply voltage (V).  $V_{ae}$ Voltage across  $R_b$  (V).  $V_{gs}$ Gate-source voltage (V).  $V_T$ MOSFET threshold voltage (V). Forced convection air velocity (cm/s).  $r_{\rm air}$ vusat, vusat Electron, hole saturation velocity (cm/s). x, Position of node i (cm).  $Z_{\rm fin}$ Height of heatsink fin (cm).  $\alpha_1, \alpha_2$ Carrier-carrier scattering coefficients.  $\beta_{tr,v}$ Relative size of current tail. Cylindrical, spherical angle fraction. High-level injection lifetime (s). THL. Mass density (g/cm<sup>3</sup>). 0  $\mu_n$ ,  $\mu_n$ Electron, hole mobility  $(cm^2/V \cdot s)$ .

## II. INTRODUCTION

**E**FFECTIVE simulation of power electronic circuits requires the availability of accurate models for the power semiconductor devices in the simulators used by circuit and system designers. Because the structures of power devices are significantly different than their microelectronic integrated circuit counterparts, the semiconductor models in most commercial circuit simulators do not adequately describe the behavior of power devices. Recently though, accurate physicsbased power semiconductor models have been implemented into circuit and system simulation programs [1]–[5] and characterized power device part numbers have been included in simulator component libraries [2], [4]. However, the device temperature is a critical parameter in determining the electrical behavior of power devices because the devices dissipate a considerable amount of heat and are often operated in high-temperature environments. In addition, the simulation of electrothermal behavior is important in the design of power modules and power circuit boards because of the thermal coupling between adjacent semiconductor devices.

Although the traditional microelectronic semiconductor device models include temperature dependence, the temperature used by the device models in programs such as SPICE (Simulation Program with Integrated Circuit Emphasis) must be chosen by the user prior to the simulation and hence must remain constant at the predetermined value during the simulation. The unique approach taken in this work is to define the temperatures at various positions within the silicon chips, packages, and heatsinks (thermal network) as simulator system variables so that the dynamic temperature distribution within the thermal network is solved for by the simulator in the same way as the node voltages within the electrical network are solved for. Because the device electrical characteristics depend upon the instantaneous temperature calculated from the thermal network models, the dynamic self-heating is accounted for and the dynamic heating of adjacent devices can be described (e.g., thermal coupling between devices in a power module or on a common heatsink).

The purpose of this paper is to describe the new methodology for simulating the dynamic electrothermal behavior of power electronic circuits and systems. The new methodology enables the designer to incorporate thermal management considerations into the design of electronic systems. For example, the designer can readily interchange semiconductor devices having similar electrical characteristics but with different chip areas and thus different thermal characteristics. The designer can also interchange thermal network components such as packages and heatsinks and can change the topology of the thermal components within the thermal network. For example, the behavior of a system including thermal coupling between adjacent electrical devices mounted on a single heatsink can be compared with the behavior of the same system but with the devices having separate heatsinks. In this paper, the methods used to develop the electrothermal semiconductor device models and the thermal network component models are given, and the methods used to implement these models into the Saber<sup>2</sup> circuit simulator are described. Examples are also given to demonstrate the accuracy, computational efficiency, and ease of use of the new methodology.

## **III. ELECTROTHERMAL SIMULATION METHODOLOGY**

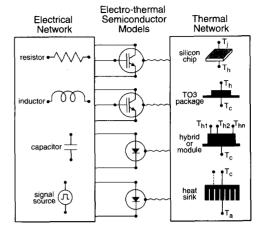

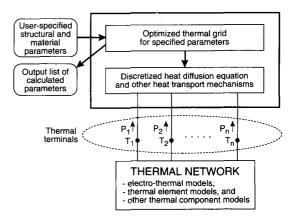

Fig. 1 is a diagram of the electrothermal network simulation methodology indicating that the electrical and thermal networks are coupled through the electrothermal models for the semiconductor devices. The electrothermal models for the semiconductor devices (IGBT's and power diodes in Fig. 1)

Fig. 1. Diagram indicating interconnection of electrical and thermal networks through electrothermal models for semiconductor devices.

have electrical terminals that are connected to the electrical network and a thermal terminal that is connected to the thermal network. The thermal nodes in the thermal network have units of temperature (K) across the nodes and units of power (W) flowing through the nodes, whereas the through and across variables for electrical networks are current and voltage. The thermal network is represented using thermal network component models so that the thermal models for different packages and heatsinks can be readily interconnected in the same way that the electrical network components are interconnected. The thermal network models for power modules and heatsinks contain multiple terminals and account for the thermal coupling between the adjacent semiconductor devices.

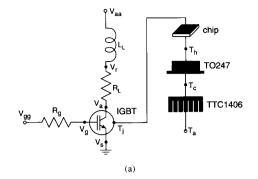

As an example, Fig. 2(a) is a schematic of an electrothermal network, and Fig. 2(b) is the corresponding Saber simulator netlist using the IGBT electrothermal model [6] and the thermal component models of the silicon chip, the T0247 package, and the TTC1406 heatsink [7]. The first column of the Saber netlist in Fig. 2(b) specifies the name of the template that contains the model equations for each component (LHS of the period) and the instance within the circuit (RHS of the period). The remaining columns on the LHS of the equal sign indicate the terminal connection points of the components within the network, where the electrothermal IGBT model is connected to both the electrical and thermal networks. The parameters used by the model templates to describe the specific components are listed on the RHS of the equal sign. For example, the temperature coefficients of the IGBT base lifetime and transconductance parameter are changed from the default values. It is evident from Fig. 2 that the thermal network component models developed in this work are interconnected to form the thermal network in the same way as the electrical components are interconnected to form the electrical network.

An advantage of the new methodology is that the interconnection of the thermal and electrical components are easily changed so that the system designer can readily examine different electrical and thermal network topologies and can

<sup>&</sup>lt;sup>2</sup>Saber<sup>TM</sup> is a trademark of Analogy Inc., Beaverton, OR. The models described in this paper are provided within Saber version 3.2

#IGBT electro-thermal simulation

| #Electronic ne                 | etwo | rk | CC  | mpone | ents | 5 |                          |

|--------------------------------|------|----|-----|-------|------|---|--------------------------|

| v.vaa                          | vaa  | 1  | 0   |       |      |   | 300                      |

| 1.11                           | vaa  | 1  | vr  |       |      | = | 80u                      |

| r.rl                           | vr   |    | va  |       |      | = | 30                       |

| r.rg                           | vgg  | J  | vg  |       |      | = | 10                       |

| pulsgen.1                      | vgq  | J  | 0   |       |      | = | 20                       |

| #IGBT electro-<br>igbt_therm.1 |      |    |     |       |      | = | tauhl_1=1.6,<br>kp_1=1.5 |

| #Thermal netwo                 | ork  | со | mpc | onent | s    |   |                          |

| chip_therm.1                   |      | tj |     | th    |      | = | thick=0.05,              |

|                                |      |    |     |       |      |   | a_chip=0.1               |

| to247_therm.1                  |      | th |     | tc    |      | = | a_chip=0.1,              |

|                                |      |    |     |       |      |   | ychedm=0.2               |

| ttc1406_therm.                 | .1   |    |     |       |      |   | a_heat=0.4               |

| t.ta                           |      | ta |     | 0     |      | = | 300                      |

|                                |      |    | (]  | b)    |      |   |                          |

|                                |      |    |     |       |      |   |                          |

Fig. 2. (a) Schematic and (b) Saber netlist of an example electrothermal network.

easily exchange different thermal and electrical component types. To simplify the system design process, the thermal component models are represented in the same form as the electrical component models, and the details of the thermal component model physics are transparent to the user. However, the structural and physical parameters of the thermal models enable the user to provide the specific information necessary to perform accurate simulations. Furthermore, by connecting the thermal terminal of the electrothermal semiconductor device models to a constant temperature source, the models reduce to the traditional global temperature-dependent models used for traditional electrical network simulation. Thus, the traditional semiconductor models can be completely replaced by the electrothermal semiconductor models so that design engineers can incorporate the thermal management considerations at any point in the traditional electrical network design process.

Because the time constants for heat flow within the silicon chip, package, and heatsink are many orders of magnitude longer than the time constants of the electronic devices and circuits, the self-heating effects behave dynamically even for circuit conditions that are considered to be static for the electronic devices. In addition, for circuit conditions that result

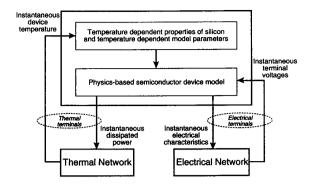

Fig. 3. Structure of the electrothermal semiconductor device models.

in high power dissipation levels, the heat is applied rapidly to the chip and only diffuses a few micrometers into the chip surface. Therefore, the chip-heating process is nonquasi-static, and the temperature distribution within the thermal network depends upon the rate at which the heat is applied. The thermal network component models used in this work accurately describe the dynamic temperature distribution in the thermal network for the full range of applicable power dissipation levels. The new dynamic electrothermal network simulation methodology provides a procedure for developing accurate and computationally efficient thermal network component models and electrothermal semiconductor models. The simulation speed for typical electrothermal network simulations is comparable to that of the electrical network alone.

#### **IV. ELECTROTHERMAL SEMICONDUCTOR MODELS**

The electrothermal semiconductor device models couple the electrical and thermal networks. Fig. 3 is a diagram of the structure of the electrothermal semiconductor device models indicating the interaction with the thermal and electrical networks through the electrical and thermal terminals, respectively. The electrothermal semiconductor models use the instantaneous device temperature (temperature at the silicon chip surface  $T_i$ ) to evaluate the temperature-dependent properties of silicon and the temperature-dependent model parameters. These temperature-dependent values are then used by the physics-based semiconductor device model to describe the instantaneous electrical characteristics and the instantaneous dissipated power. The network simulator solves the system of electrothermal equations by iterating the system variables (electrical node voltages, thermal node temperatures, and explicitly defined system variables) until the components of currents into each electrical node sum to zero (Kirchhoff's current law) and the components of power flow into each thermal node sum to zero (energy conservation). In the remainder of this section, the Saber electrothermal IGBT model is used as an example [6].

The temperature-dependent expressions for the physical properties of silicon are given in Table I and the temperature-

TABLE I TEMPERATURE-DEPENDENT PROPERTIES OF SILICON

$$\mu_n(T_j) = 1500 \cdot (300/T_j)^{2.5} \tag{T1.1}$$

$$\mu_p(T_i) = 450 \cdot (300/T_i)^{2.5} \tag{T1.2}$$

$$D_n(T_i) = \mu_n \cdot kT_i/q \tag{T1.3}$$

$$D_p(T_j) = \mu_p \cdot kT_j/q \tag{T1.4}$$

$$n_i(T_j) = 3.88 \times 10^{16} \cdot (T_j)^{1.5} / \exp(7000/T_j)$$

(T1.5)

$$v_{nsat}(T_j) = 10^7 \cdot (300/T_j)^{0.87}$$

(T1.6)

$$v_{psat}(T_i) = 8.37 \times 10^6 \cdot (300/T_i)^{0.52}$$

(T1.7)

$$\alpha_1(T_j) = 1.04 \times 10^{21} \cdot (T_j/300)^{1.5}$$

(T1.8)

$$\alpha_2(T_j) = 7.45 \times 10^{13} \cdot (T_j/300)^2 \tag{T1.9}$$

$$BV_k(T_j) = 5.34 \times 10^{13} \cdot (T_j/300)^{0.35}$$

(T1.10)

dependent IGBT model parameters are given in Table II [6]. The empirical expressions of Table II are developed using the extracted values of the model parameters versus temperature [8]. An accurate extraction sequence [1], [2] is required to resolve the temperature dependence of the IGBT model parameters. The parameters in Table II with subscript 0 are the extracted values of the model parameters at the nominal temperature  $T_0$ , and the parameters with subscript 1 are the extracted temperature coefficients of the IGBT model parameters. The advantage of using a physics-based model for the power semiconductor devices is that the well-known temperature-dependent properties of silicon can be used to describe the temperature dependence of the model, and only a few temperature-dependent model parameter expressions must be developed. However, for models that rely heavily on empirical-based formulas, each of the empirical formulas must be calibrated versus temperature. Therefore, it is recommended that the electrothermal models be developed using models that are derived directly from semiconductor device physics without unsubstantiated approximations.

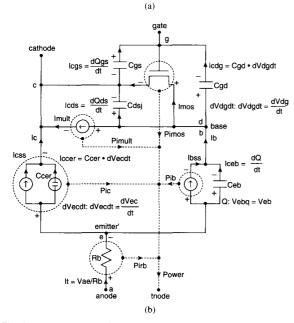

To implement electrothermal models into the Saber circuit simulator, the components of current into electrical nodes and the components of power into thermal nodes are expressed in terms of simulator system variables. System variables for electrothermal models are the electrical node voltages, thermal node temperatures, and other system variables defined to solve implicit model equations. Fig. 4(a) is the equations section of the Saber electrothermal IGBT model, and Fig. 4(b) is an analog circuit representation of the Saber electrothermal IGBT model equations where the components of power dissipation are indicated by dashed lines. The first six statements in Fig. 4(a) specify the components of current between the device electrical terminals and the internal electrical nodes,

| TABLE                 | 11   |             |  |

|-----------------------|------|-------------|--|

| TEMPERATURE-DEPENDENT | IGBT | P ARAMETERS |  |

$$\tau_{HL}(T_j) = \tau_{HL0} \cdot (T_j/T_0)^{\tau_{HL1}}$$

(T2.1)

$$I_{sne}(T_j) = \frac{I_{sne0} \cdot (T_j/T_0)^{I_{sne1}}}{\exp\left[14000 \cdot (1/T_j - 1/T_0)\right]}$$

(T2.2)

$$V_T(T_j) = V_{T0} + V_{T1} \cdot (T_j - T_0)$$

(T2.3)

$$K_p(T_j) = K_{p0} \cdot (T_0/T_j)^{K_{p1}}$$

(T2.4)

and the next five statements specify implicit model functions [3]. Finally, the last statement in Fig. 4(a) specifies the power delivered to the thermal terminal (tnode). The model functions used in the equations section, e.g., Qgs, Cgd, Imos,  $\cdots$ , and power of Fig. 4 are evaluated in terms of the system variables in the values section of the Saber IGBT electrothermal template.

To incorporate the electrothermal effects into the Saber IGBT model described in [3], the expressions in Tables I and II are added to the beginning of the values section of the Saber IGBT template, and the temperature coefficients are added to the template parameter list. The model functions used to calculate the electrical characteristics ( in [3, Table 1] ) are then evaluated using these temperature-dependent quantities, whereas in the traditional approach used in the nonelectrothermal Saber IGBT model, these quantities are model parameters that do not change value during simulation. Finally, the expression for the dissipated power is calculated at the end of the values section of the Saber electrothermal IGBT template using the temperature-dependent model functions. The dissipated power must be calculated using the internal components of current as indicated in Fig. 4(b) and not simply the terminal currents and voltages, because the power delivered to internal device capacitances is not dissipated immediately as heat but is stored in the electric field energy of the capacitors [6].

### V. THERMAL NETWORK COMPONENT MODELS

In the new electrothermal network simulation methodology, the thermal network is represented as an interconnection of thermal component models where each component represents an indivisible building block used by the designer to form the thermal network (see Fig. 1). Fig. 5 shows the structure of the thermal component models, indicating that the thermal component models interact with the external thermal network through thermal terminals. The terminals of the thermal component can be connected to the thermal terminals of other thermal component models, to the thermal terminals of electrothermal models, and to thermal element models such as temperature sources. To use the thermal component models, the designer only needs to specify the connection points of the thermal terminals within the thermal network and the structural and material parameters of the model. The thermal component models are parameterized in terms of structural and material

```

equations {

d_by_dt(Qgs)

i(gate - > cathode)

dVdgdt

i(drain - > gate)

d_by_dt(Qds)

i(drain - > cathode)

+≕ Imos

dVecdt

i(emitter - > cathode)

\pm = lcss

Ccer

i(emitter - > drain)

+= lbss

d_by_dt(Q)

i(anode - > emitter)

+= Vae/Rb

dVdgdt : dVdgdt= d_by_dt(Vdg)

dVecdt= d_by_dt(Vec)

dVecdt ·

Vebq=Veb

Q

Nsat=lc/(q^*A^*vpsat) - Imos/(q^*A^*vnsat)

Nsat

muciny :

mucinv = Pm*log(1. + alpha2/Pm**(2./3.))/alpha1

```

Fig. 4. (a) Equations section of Saber IGBT electrothermal template, and (b) schematic of components of current and dissipated power within IGBT electrothermal model.

parameters so that the details of the heat transport physics are transparent to the user.

The thermal component models are based upon a discretization of the heat diffusion equation for various threedimensional coordinate system symmetry conditions and include the nonlinear thermal conductivity of silicon and nonlinear convection heat transfer. A logarithmic grid spacing is used by the thermal component models to provide the high resolution needed near the heat sources for high power dissipation levels without resulting in an excessive number of thermal nodes. As indicated in Fig. 5, the user-defined structural and material parameters are used by the model to determine the optimized thermal grid for the discretization as well as the appropriate discretization coefficients. This

Fig. 5. Structure of the thermal component models.

results in both accurate and computationally efficient (compact) thermal models that are suitable for simulation of large electrothermal networks. The thermal models also provide an output list of internally calculated parameters such as the thermal node positions that are useful for interpreting the simulated temperature waveforms.

The three-dimensional heat diffusion equation for isotropic materials (thermal conductivity is independent of direction) can be written as:

$$\nabla \cdot (k(T)\nabla T) = \rho c \frac{\partial T}{\partial t}$$

(1a)

where the thermal conductivity is nonlinear for silicon and is given by [9]:

$$k(T) = 1.5486 \cdot (300/T)^{4/3}$$

. (1b)

For various symmetry conditions, this partial differential equation can be discretized into a finite number of first-order ordinary differential equations of the form

$$\frac{T_{i+1} - T_i}{R_{i,i+1}} - \frac{T_i - T_{i-1}}{R_{i-1,i}} = \frac{dH_i}{dt}$$

(2a)

where

$$H_i = C_i \cdot T_i \tag{2b}$$

is the heat energy stored at thermal node *i*. The heat equation and the discretization coefficients  $(R_{i,i+1}, \text{ and } C_i)$  are given in Table III for the rectangular coordinate system with *y*and *z*-axis symmetry, Table IV for the cylindrical coordinate system with *z* and  $\theta$  symmetry, and Table V for the spherical coordinate system with  $\theta$  and  $\phi$  symmetry. The discretization coefficients are obtained by integrating the heat diffusion equations across the thermal element represented by each node (e.g., between  $(x_{i-1} + x_i)/2$  and  $(x_i + x_{i+1})/2$  for node *i* in rectangular coordinates), and by then applying finite differences to evaluate the spatial derivatives.

To implement thermal component models into Saber templates, the models are formulated such that the components of power flow between the thermal nodes are expressed in terms of the node temperatures. An example equations section for the discretized form of the heat diffusion equation is shown in Fig.

380

$$A\frac{\partial}{\partial x}\left(k(T)\frac{\partial I}{\partial x}\right) = A\rho c\frac{\partial I}{\partial t}$$

(T3.1)

$$C_{i} = A\rho c \cdot (x_{i+1} - x_{i-1})/2$$

(T3.2)

$$c_i = i \mu c \quad (w_{i+1} \quad w_{i-1}) / 2 \qquad (1012)$$

$$R_{i,i+1} = (x_{i+1} - x_i)/A/k_{i,i+1}$$

(T3.3)

| TABLE IV                                                                                                                          |        |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------|--------|--|--|--|--|--|

| Cylindrical Coordinate $z$ and $\theta$ Symmetry                                                                                  |        |  |  |  |  |  |

|                                                                                                                                   |        |  |  |  |  |  |

| $A\frac{1}{\pi}\frac{\partial}{\partial r}\left(k(T)r\frac{\partial T}{\partial r}\right) = A\rho c\frac{\partial T}{\partial t}$ | (T4.1) |  |  |  |  |  |

$$r \partial r \left( \begin{array}{c} \cdot & \partial r \end{array} \right) \quad \partial t$$

(T4.2)

$A = 2\pi r \gamma z$

$$C_i = \pi \gamma z \rho c \left[ \left( \frac{r_{i+1} + r_i}{2} \right)^2 - \left( \frac{r_i + r_{i-1}}{2} \right)^2 \right] \qquad (T4.3)$$

$$R_{i,i+1} = \frac{1}{2\pi\gamma z k_{i,i+1}} \ln\left(\frac{r_{i+1}}{r_i}\right)$$

(T4.4)

TABLE V

SPHERICAL COORDINATE

$$\theta$$

AND  $\phi$  SYMMETRY

$A \frac{1}{r^2} \frac{\partial}{\partial r} \left( k(T)r^2 \frac{\partial T}{\partial r} \right) = A\rho c \frac{\partial T}{\partial t}$

(T5.1)

$$A = 4\pi r^2 \gamma \tag{T5.2}$$

$$C_{i} = \frac{4}{3}\pi\gamma\rho c \left[ \left( \frac{r_{i+1} + r_{i}}{2} \right)^{3} - \left( \frac{r_{i} + r_{i-1}}{2} \right)^{3} \right]$$

(T5.3)

$$R_{i,i+1} = \frac{1}{4\pi\gamma k_{i,i+1}} \left(\frac{1}{r_i} - \frac{1}{r_{i+1}}\right)$$

(T5.4)

6. The first six statements of Fig. 6 describe the heat conduction between adjacent nodes using the thermal resistance [LHS of (2a)]. The last five statements describe the components of power stored as heat energy in the thermal capacitance at each thermal node [RHS of (2a)]. The discretized heat diffusion equation has a similar form for all of the thermal component models except that each model uses a different method to calculate the discretization coefficients.

For example, the silicon chip thermal model is based upon the rectangular coordinate heat diffusion equation and includes the nonlinear thermal conductivity of silicon. The parameters of the chip\_therm template described in the netlist of Fig. 2(b) are the chip area a\_chip and the chip thickness thick. Using these parameter values, the template calculates the positions of the internal nodes  $x_i$  to form the logarithmic grid spacing. The node positions, the chip area, and the instantaneous node temperatures are used to evaluate the model functions  $R_{i,i+1}, C_i$ , and  $H_i$  that are used by the equations section (Fig. 6). The node positions and equations {

| <br>                |     |             |

|---------------------|-----|-------------|

| p(junct - > node1)  | +=  | (Tj-T1)/Rj1 |

| p(node1 - > node2)  | +=  | (T1-T2)/R12 |

| p(node2 - > node3)  | +≈  | (T2-T3)/R23 |

| p(node3 — > node4)  | +== | (T3-T4)/R34 |

| p(node4 - > node5)  | +≃  | (T4–T5)/R45 |

| p(node5 - > header) | +=  | (T5-Th)/R5h |

|                     |     |             |

| p(node1)            | +=  | d_by_dt(H1) |

| p(node2)            | +=  | d_by_dt(H2) |

| p(node3)            | +=  | d_by_dt(H3) |

| p(node4)            | +≈  | d_by_dt(H4) |

| p(node5)            | +=  | d_by_dt(H5) |

| }                   |     |             |

| )                   |     |             |

Fig. 6. Equations section for discretized form of heat diffusion equation.

heat capacitances are calculated in the parameters section of the Saber template prior to simulation time because they do not depend on simulator system variables. These calculated parameters can be listed when the templates are loaded by setting the parameter list > 0.

The package models describe the two-dimensional lateral heat spreading, the die attachment thermal resistance, and the heat capacity of the periphery of the package. The lateral heat spreading in the package results in an effective heat flow area that increases with depth into the package. In the model, the effective heat flow area at each depth into the package is obtained by combining the components of heat flow area resulting from cylindrical heat spreading along the edges of the chip, the spherical heat spreading at the corners of the chip, and the rectangular coordinate component of heat flow directly beneath the chip. However, the lateral heat spreading does not extend beyond the edge of the package, so the distance that the heat spreads in each direction is limited in the model by the distance from each edge of the chip to the edges of the package. The effective heat flow area and the discretization coefficients are calculated internally by the model when the model templates are loaded, so the user only needs to specify the structural parameters such as the chip area, the location of chip on the package, and the package thickness to describe the lateral heat spreading.

The heatsink models describe the heat spreading at the heatsink package interface, the semicylindrical heat flow from the package toward the heatsink fins, and the nonlinear forced and natural convection heat transfer at the heatsink fins. The value of the effective heat flow area at the package—heatsink interface is determined by the package model and is used as a parameter for the heatsink models [a\_heat of Fig. 2(b)]. This parameter is used in calculating the heat spreading in the heatsink directly beneath the package and in determining the size of the grid spacing in the heatsink. For larger distances from the package within the heatsink, the heat flow becomes semicylindrical as the heat flows toward the heatsink fins. At the heatsink fins the heat is transferred to the ambient terminal by forced and natural convection.

The natural convection thermal resistance is given by [10]:

$$h'_{\rm nat} = 4.84 \times 10^{-4} \frac{A_{\rm fin}}{P_{\rm fin}^{0.35}} \tag{3a}$$

$$R_{\rm nat} = \frac{1}{h'_{\rm nat} \cdot (T_f - T_a)^{0.35}}$$

(3b)

and the forced convection thermal resistance is given by:

$$f = \begin{cases} 1.7 + 0.148 \cdot \ln(v_{\rm air}/508) & \text{for } v_{\rm air} \le 508 \text{ cm/s} \\ 1.7 + 0.433 \cdot \ln(v_{\rm air}/508) & \text{for } v_{\rm air} > 508 \text{ cm/s} \end{cases}$$

(42)

$$h'_{\rm for} = f \cdot 4.88 \times 10^{-4} \frac{A_{\rm fin}}{\sqrt{Z_{\rm fin}}}$$

(4b)

$$R_{\rm for} = \frac{1}{h'_{\rm for} \cdot \sqrt{v_{\rm air}}} \tag{4c}$$

where the fin-to-ambient thermal resistance is the parallel combination of the forced convection thermal resistance, the natural convection thermal resistance, and the shunt mounting thermal resistance. Because  $h'_{\rm nat}$  and  $h'_{\rm for}$  do not depend upon the simulator system variables they are calculated in the parameters section of the Saber template and can be listed when the templates are loaded.

# VI. ELECTROTHERMAL SIMULATION RESULTS

The new electrothermal network simulation methodology provides the capability to incorporate thermal management considerations into the design of electronic systems. The electrothermal semiconductor models can be used to predict the temperature-dependence of the semiconductor device characteristics for user-defined bias or transient conditions. The thermal network component models can be used to predict the transient thermal response of a user-defined thermal network topology for user-defined power dissipation functions. Finally, the electrothermal semiconductor models can be combined with the thermal network component models to predict the interaction of the electrical and thermal networks. In this section, example electrothermal simulations are given, and the results are verified by comparison with measurements. The temperature waveforms are verified using several different temperature measurement methods: 1) infrared microradiometer measurement of chip surface temperature waveforms [7], [11], [12], 2) thermocouple probe measurements of heatsink temperature waveforms, 3) threedimensional transient finite element simulations of temperature [13], and 4) device temperature-sensitive electrical parameter measurements [11], [12].

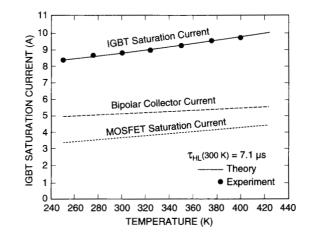

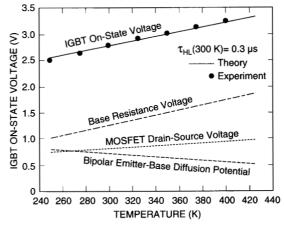

The temperature dependence of semiconductor device electrical characteristics varies with device part number as well as bias conditions or transient operating conditions. Therefore, semiconductor device data sheets cannot describe the temperature dependence for all of the applicable operating conditions. However, the electrothermal semiconductor models discussed in this work can be used to describe the temperature dependence of a given device part number for user-defined bias conditions or transient operating conditions. For example, Figs. 7 and 8 compare the measured and simulated temperature dependence of the IGBT saturation current and

Fig. 7. Simulated and measured temperature dependence of IGBT saturation current for  $V_{gs} = 9$  V and  $V_a = 10$  V.

Fig. 8. Simulated and measured temperature dependence of IGBT on-state voltage for  $V_{gs} = 20$  V and  $I_T = 10$  A.

on-state voltage characteristics for specific device types and bias conditions. The saturation current of Fig. 7 increases with temperature, but for higher currents or lower transconductance IGBT's, the saturation current decreases with temperature. The on-state voltage of Fig. 8 increases with temperature, but for IGBT's with higher base lifetimes or for lower anode currents, the on-state voltage can decrease with temperature. The simulations of Figs. 7 and 8 are performed using the Saber dc transfer analysis to sweep the ambient temperature source  $T_a$ , which is connected directly to the IGBT thermal terminal. For transient conditions, a family of waveforms each for a different temperature can be generated using a Saber vary loop to step the device temperature.

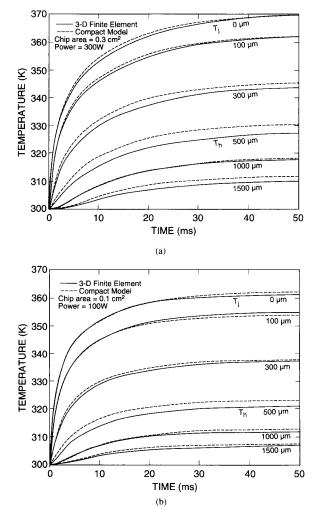

Traditional methods for simulating the transient temperature distribution in semiconductor devices and packages are not suitable for simulating large thermal networks because they do not result in compact models that are both accurate and computationally efficient [7]. However, the new thermal network component models can be used to simulate the transient

Fig. 9. Comparison of the thermal step response predicted by the thermal network component models with three-dimensional finite element simulations for a) a  $0.3 \text{-cm}^2$  area chip and b) a  $0.1 \text{-cm}^2$  area chip is a TO247 package, where the temperature waveforms at various positions in the chip (0 through 500  $\mu$ m) and the TO247 package (500 through 2500  $\mu$ m) are indicated.

thermal response of user-defined thermal networks for userdefined power dissipation functions. For example, Fig. 9 compares the thermal step response predicted by the thermal component models with three-dimensional finite element simulations [13] for a) a 0.3-cm<sup>2</sup> area chip and b) a 0.1-cm<sup>2</sup> area chip in a T0247 package, where the temperature waveforms at various positions in the chip (0 through 500  $\mu$ m) and the TO247 package (500 through 2500  $\mu$ m) are indicated. The temperature drop in the package  $(T_h - 300 \text{ K})$  is larger for the large chip area [Fig. 9(a)] than for the smaller chip area [Fig. 9(b)] at the same power per unit area  $1000 \text{ W/cm}^2$ . This occurs because the lateral heat spreading in the package is more significant for the smaller chip and because the smaller chip is located farther from the edge of the package. The package model accounts for these effects, while the user only needs to specify the dimensions and location of the chip on the package.

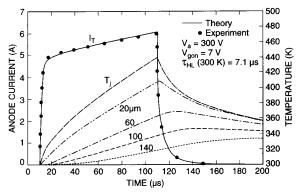

Fig. 10. Simulated and measured IGBT short-circuit current and simulated temperature waveforms at selected positions within silicon chip.

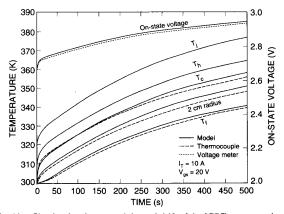

Fig. 11. Simulated and measured thermal drift of the IGBT on-state voltage where the temperature waveforms are measured using thermocouple probes at the package-heatsink interface  $(T_c)$ . a 2-cm radius from the package within the heatsink, and at the heatsink fins  $(T_f)$ .

Finally, the interaction of the electrical and thermal networks are described for different circuit operating conditions. For electrothermal simulations, the instantaneous power dissipation determined by the electrical model is used by the thermal network to determine the evolution of the chip surface temperature. As the chip surface temperature changes, the electrical characteristics and power dissipation also change. Fig. 10 shows an electrothermal simulation for an IGBT shortcircuit condition, and Fig. 11 shows the thermal drift of the IGBT on-state voltage. The short circuit current of Fig. 10 increases with time because the saturation current increases with temperature (Fig. 7). The on-state voltage of Fig. 11 increases with time because the on-state voltage increases with temperature (Fig. 8). Because the temperature dependencies of the saturation current and on-state voltage have been verified for known chip temperatures (Figs. 7 and 8), the agreement between the simulated and measured electrical waveforms in Figs. 10 and 11 verify that the surface temperature waveforms are simulated accurately.

The heating of the thermal network is a nonquasi-static process so that the shape of the transient temperature distribution within the thermal network depends upon the power

dissipation level. For the high-power dissipation level of Fig. 10 (1800 W/0.1-cm<sup>2</sup> chip area), only the top 150  $\mu$ m of the silicon chip are heated during the transient condition and only 180 mJ of dissipated energy results in a 140 K rise in chip surface temperature at the end of the  $100-\mu s$ short circuit pulse. However, for the relatively low power dissipation level of Fig. 11 (25 W/0.1-cm<sup>2</sup> chip area), the heat diffuses throughout the thermal network in the 1000-s on-state condition, and several kilojoules of dissipated power are required so heat the chip surface to 100 K above the ambient temperature. The logarithmically spaced grid of the thermal models accurately describes the heating process for the full range of applicable power dissipation levels so that the user does not need to specify a different thermal grid for the different thermal heating conditions. If one were to assume a quasi-static model for the silicon chip such as a single thermal resistor and thermal capacitor, the predicted chip temperature of Fig. 10 would be a factor of five smaller than the actual temperature.

# VII. DISCUSSION OF COMPUTATION EFFICIENCY

The goal of the new methodology described in this paper is to produce accurate and computationally efficient (compact) models that are suitable for simulating large electrothermal networks. Several aspects of the new methodology, such as the principle of logarithmic grid spacing and the use of symmetry conditions to account for three-dimensional heat flow, are essential for practical electrothermal simulation. Without these innovations, the types of simulations demonstrated in Figs. 9 through 11 would not be practical given the wide range of time constants of electrothermal systems and the wide range of power dissipation levels that are applicable for the semiconductor devices. The primary factors that contribute to numerical complexity and reduce simulation speed are: 1) the number of simulator system variables that must be iterated by the simulator to solve the nonlinear model equations, 2) the degree of nonlinearity of the model functions, and 3) the relative time constants associated with simulator state variables that are integrated for transient simulation.

The heating of the thermal network is a nonquasi-static process, and a discretized heat equation with a wide range of time constants is required to describe the temperature distribution for the full range of applicable power dissipation levels. In the discretization process of (2), it is assumed that the temperature gradient and thermal conductivity do not vary substantially between adjacent thermal nodes. Therefore, the accuracy of the thermal component models is determined by the number and locations of the thermal nodes within the component. For high power dissipation levels during short periods of time (e.g., for switching transients), the surface temperature rises faster than the heat diffuses into the chip (nonquasi-static heating), and a high density of thermal nodes is required at the silicon chip surface. However, the thermal gradients disperse as the heat diffuses through the thermal network, so a grid spacing that increases logarithmically with distance from the heat source (silicon chip surface) results in the minimum number of thermal nodes required to describe the temperature distribution for the range of applicable power dissipation levels.

In general, a discretization approach for solving a partial differential equation results in a larger number of system variables (one for each node) with small time constants associated with each node (proportional to the inverse square of the number of nodes). However, the logarithmic grid spacing principle and the use of symmetry conditions reduces the number of nodes required by the thermal models by several orders of magnitude. In addition, thermal time constants are much longer than electrical time constants, so the discretized heat equation does not result in fast time constants that reduce simulation speed. If a discretization approach were used to solve the semiconductor device electrical equations, the discretization time constants would become the fastest time constants of the system and would slow the simulation speed dramatically. Finally, the nonlinearities for the thermal network are generally weak functions of temperature. As a consequence, the simulation CPU times of the new electrothermal network simulation methodology are comparable to those of the corresponding electrical network, not including the thermal network.

Although the electrothermal CPU times are comparable to those of the corresponding electrical network, the simulation intervals required to describe thermal phenomena such as the thermal drift of Fig. 11 can be as long as several minutes, whereas typical simulation intervals for electronic circuits are several milliseconds. Because the electrothermal networks have time constants that range from nanoseconds to kiloseconds, the class of problems that result in practical simulation times is limited. For example, in the simulation of Fig. 11, the fast time constants of the semiconductor device are not activated, and the simulation CPU time is less than 1 min on a Sun SparcStation 2. However, if one were to simulate the same circuit but with a 20 kHz switching frequency, millions of switching cycles would occur during the 500 s simulation interval and the simulation CPU time would be much longer. When simulating electrothermal phenomena that require long simulation intervals, the user must be careful not to activate fast time constants that are unnecessary for the understanding of the circuit. The long electrothermal simulation intervals can also be reduced by using a thermal simulation with an average power dissipation to set the initial conditions of the thermal network temperatures before the high frequency electrothermal simulation begins.

#### VIII. CONCLUSION

A new circuit simulation methodology has been developed in which the temperature used by the electrothermal semiconductor device models is determined by the simulator. The electrothermal models are developed using physics-based semiconductor models, the temperature-dependent properties of silicon, and the extracted temperature dependence of the model parameters. The power dissipated in the semiconductor devices is used by the thermal network models to determine the dynamic temperature distribution within the thermal network, where the thermal network is represented by an interconnection of thermal components so that different thermal network topologies can readily be examined. The thermal components are parameterized in terms of structural and material parameters so that the details of the heat transport physics are transparent to the user. A systematic procedure has been presented for developing both the electrothermal semiconductor models and the thermal network component models. The electrothermal network simulations are useful for determining 1) the temperature dependence of semiconductor device electrical characteristics for user-defined operating conditions, 2) the response of thermal networks to user-defined power dissipation functions, and 3) the interaction of electrical and thermal networks.

#### REFERENCES

- A. R. Hefner, "Device models, circuit simulation, and computercontrolled measurements for the IGBT," in *Rec. 2nd IEEE Workshop* on Computers in Power Electron., 1990, p. 233.

- [2] —, "Semiconductor measurement technology: INSTANT—IGBT network simulation and transient analysis tool," NIST Special Pub. 400-88, 1992.

- [3] A. R. Hefner and D. M. Diebolt, "An experimentally verified IGBT model implemented in the Saber circuit simulator," in *IEEE PESC Conf. Rec.*, 1991, p. 10.

[4] Saber Manual, "IGBT template description," Analogy Inc., Beaverton,

- [4] Saber Manual, "IGBT template description," Analogy Inc., Beaverton, OR, vol. T-2, p. 31-32, 1992.

[5] C. S. Mitter, A. R. Hefner, D. Y. Chen, and F. C. Lee, "Insulated

- [5] C. S. Mitter, A. R. Hefner, D. Y. Chen, and F. C. Lee, "Insulated gate bipolar transistor (IGBT) modeling using IG-SPICE," in *Conf. Rec. IEEE Industry Applicat. Society Meet.*, 1991, p. 1515; also to appear in *IEEE Trans. Industry Applicat.*, Jan. 1994.

- [6] A. R. Hefner, "A dynamic electro-thermal model for the IGBT," in Conf. Rec. Industry Applicat. Society Meet., 1992, p. 1094; also to appear in IEEE Trans. Industry Applicat., March 1994.

- IEEE Trans. Industry Applicat., March 1994.

[7] A. R. Hefner and D. L. Blackburn, "Thermal component models for electro-thermal network simulation," in *Proc. IEEE Semicond. Thermal Measurement and Management SEMI-THERM Symp.*, 1993, p. 88; also to appear in *IEEE Trans. Compon.*, Hybrids, and Manuf. Technol., 1994.

- [8] P. O. Lauritzen, G. A. Franz, and A. R. Hefner, "Component characterization and parameter extraction," in notes of *IEEE PESC Conf. Tutorial Course on Modeling Devices Used in Circuit Simulators*, 1991, pp. 4-16, 4-17.

- [9] S. Selberherr, Analysis and Simulation of Semiconductor Devices. New York: Springer-Verlag, p. 119, 1984.

- [10] G. N. Ellison, *Thermal Computations for Electronic Equipment*. New York: Van Nostrand Reinhold, 1984, p. 218,

[11] F. F. Oettinger and D. L. Blackburn, "Semiconductor measurement

- [11] F. F. Oettinger and D. L. Blackburn, "Semiconductor measurement technology: Thermal resistance measurements," NIST Special Pub. 400-86, July 1990.

- [12] D. L. Blackburn, "A review of thermal characterization of power transistors," in Proc. IEEE Semicond. Thermal Measurement and Management SEMI-THERM Symp., 1988, pp. 1–7.

[13] ANSYS Engineering Analysis Systems Users Manual, Swanson Analysis Systems Inc.; Houston, PA, 1989.

Allen R. Hefner, Jr. (S'84–M'84–SM'93) was born in Washington, DC on June 29, 1959. He received the B.S., M.S., and Ph.D. degrees in electrical engineering from the University of Maryland in 1983, 1985, and 1987, respectively.

He joined the Semiconductor Electronics division of the National Institute of Standards and Technology (formerly the National Bureau of Standards) in 1983. He is currently Project Leader for the Electrical and Thermal Characterization Project in the Device Technology Group of the Semiconductor

Electronics Divison at NIST. His research interests include characterization, modeling, and circuit utilization of power semiconductor devices. He is the author of 20 publications in IEEE TRANSACTIONS and conference proceedings.

Dr. Hefner received the U.S. Department of Commerce Silver Metal Award for his pioneering work in modeling advanced power semiconductor devices for electrothermal circuit simulation. He is also the recipient of an IEEE Industry Applications Society prize paper award. He was also an instructor for the IEEE Power Electronic Specialist Conference tutorial course (1991 and 1993). He has served as a program committee member for the IEEE Power Electronics Specialist Conference (1991–1993) and as the IEEE Industry Applications Society Transactions Review Chairman for the Power Semiconductor Committee (1989–1993).

**David L. Blackburn** received the B.S. degree in physics from Ohio University, Athens, in 1965 and the M.S. degrees in physics from Case Western Reserve University, Cleveland, OH, in 1968.

Since 1968, he has been involved with research on semiconductor materials and devices at the National Institute of Standards and Technology (NIST) (formerly the National Bureau of Standards) in Gaithersburg, MD. His current research interests include the safe limit and thermal characterization of power semiconductor devices and the thermal

characterization of GaAs devices and circuits. In addition to his duties at NIST, he has been an instructor in the Electrical Engineering Department at the University of Maryland, College Park, MD. Currently, he is Group Leader for the Device Technology Group in the Semiconductor Electronics Division at NIST.

Mr. Blackburn received the U.S. Department of Commerce Silver Medal Award for contributions in reducing electronic failures and increasing the reliability of electronic systems. He has been Program Chairman for SEMI-THERM V and X and General Chairman of SEMI-THERM VI.