## Spatial distributions of trapping centers in HfO<sub>2</sub>/SiO<sub>2</sub> gate stacks

Dawei Heh,<sup>a)</sup> Chadwin D. Young, George A. Brown, P. Y. Hung, Alain Diebold, and Gennadi Bersuker *SEMATECH, Inc., Austin, Texas 78741*

Eric M. Vogel

Semiconductor Electronics Division, National Institute of Standards and Technology, Gaithersburg, Maryland 20899

Joseph B. Bernstein

Center for Reliability Engineering, University of Maryland, College Park, Maryland 20742

(Received 14 November 2005; accepted 8 March 2006; published online 13 April 2006)

A methodology to analyze charge pumping (CP) data, which allows positions of probing traps in the dielectric to be identified, was applied to extract the spatial profile of traps in  $SiO_2/HfO_2$  gate stacks. The results suggest that traps accessible by CP measurements in a wide frequency range, down to few kilohertz, are located within or near the interfacial  $SiO_2$  layer rather than in the bulk of the high*k* film. © 2006 American Institute of Physics. [DOI: 10.1063/1.2195896]

As the gate oxide thickness of metal-oxide semiconductor field effect transistors (MOSFETs) is scaled down, gate leakage current increases exponentially raising concerns about power dissipation and the reliability of traditionally used silicon dioxide.<sup>1-4</sup> To reduce the large gate leakage while further scaling oxide thickness, gate dielectric materials with high dielectric constants (high-k), in particular HfO<sub>2</sub> and Hf silicates, have been proposed to replace SiO2.5-7 However, these materials, as other transition metal oxides, exhibit a high density of intrinsic electron traps.<sup>8,9</sup> The growth of Hf-based oxides on the Si substrate by any deposition method is known to lead to the formation of a multilayer dielectric stack, which includes a SiO<sub>2</sub> layer at the interface between the Hf film and the substrate. This interfacial layer, whose properties are strongly process dependent, is suggested to be essentially substoichiometric,<sup>10,11</sup> which would result in a higher density of the electron traps. Therefore, to evaluate high-k dielectrics and deposition methods, it is critical to separate contributions from the traps in high-kfilm and the interfacial layer to device electrical characteristics. Knowing the spatial distribution of the traps affecting transistor performance can help in understanding the physical nature of the defects.

Charge pumping (CP) has been widely used to study interface traps in Si/SiO<sub>2</sub> system for more than 30 years.<sup>12,13</sup> It has been shown qualitatively that, by changing the pulse frequency of the CP measurement, the trap probing in the Si/SiO<sub>2</sub> system can be controlled.<sup>14,15</sup> In this work, we first describe a quantitative model for interpreting the probing depth dependence of the CP measurements under various test conditions (frequency, raise/fall time, amplitude, etc.). We then apply the developed model to the HfO<sub>2</sub>/SiO<sub>2</sub> system having various SiO<sub>2</sub> interface thickness values.

The devices used in this work are fully processed MOSFETs with  $HfO_2/SiO_2$  stacked gate dielectrics. High-*k* gate dielectric transistors were fabricated on 200 mm p/p+ epitaxial Si<100> wafers using a standard complementary metal-oxide-semiconductor process with 1000 °C/10 s dopant activation anneal. The gate stacks were formed by depositing a 3 nm ALD HfO<sub>2</sub> dielectric on various scaled thermal oxide interface layers (ILs). A gate electrode was formed by chemical vapor deposition TiN with a poly-Si cap.<sup>16</sup> CP measurements were performed by applying periodic trapezoidal pulses with a fixed rise/fall  $(t_r/t_f)$  time and amplitude  $(V_a)$  to the gate. The dc electron-hole recombination current was measured from the substrate. To probe traps at different depths in the dielectric, pulse on and off times  $(t_{on} \text{ and } t_{off})$ were kept of equal value and varied from 50 ns to 100 ms.

The generalized CP equation can be expressed as  $1^{11}$

$$I_{\text{CP,MAX}} = qfA_G N_{\text{mit}}$$

$$= qfA_G \int_0^{x_{\text{min}}} \int_{E_{\text{min}}}^{E_{\text{max}}} N_t(x, E_t) \Delta F(x, E_t) dE_t dx, \quad (1)$$

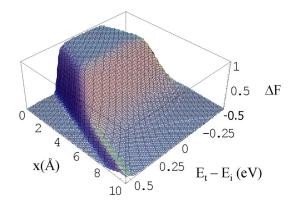

where  $N_{\rm mit}$  (cm<sup>-2</sup>) is the total measured trap density per unit area during the CP measurement and could be expressed as a double integral of multiplication of  $N_t$  and  $\Delta F$ .  $N_t$  is the trap volume density (cm<sup>-3</sup>), and  $\Delta F$  indicates the probability that a trap can be probed by CP measurement. Both of these are functions of the distance from the Si-substrate/gate-dielectric interface (*x*) and the trap energy ( $E_t$ ). Figure 1 shows a threedimensional (3D) simulation contour of  $\Delta F$  as a function of

FIG. 1. 3D  $\Delta F$  contour simulation result.  $\Delta F$  is equal to one within the trapezoidal plateau, which indicates the region having the maximum probability of being probed. The parameters used in this simulation are  $t_{onloff}$ =50 ns,  $t_{rlf}$ =30 ns,  $V_a$ =1.2 V,  $m_{elh}$ =0.5/0.4 eV,  $\Phi_{elh}$ =3.1/3.8 eV, and  $\sigma_{nlp}(0)$ =10<sup>-14</sup>/10<sup>-16</sup> cm<sup>-2</sup>.

88. 152907-1

© 2006 American Institute of Physics

Downloaded 26 Jul 2010 to 129.6.65.17. Redistribution subject to AIP license or copyright; see http://apl.aip.org/apl/copyright.jsp

<sup>&</sup>lt;sup>a)</sup>Electronic mail: dawei.heh@sematech.org

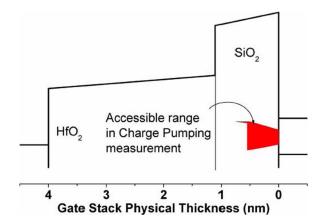

FIG. 2. Schematic of the band diagram for the high-k gate stack. The CP accessible range for the employed CP measurements conditions is shown overlapping the band diagram.

$E_t$  and x. Traps located inside the trapezoidal plateau with  $\Delta F$  equal to 1 have the maximum probability of being probed and contribute to  $I_{CP,MAX}$  during the CP measurement. Details of the simulation can be found elsewhere.<sup>15</sup> It can be seen that  $\Delta F$  drops from 1 to 0 at approximately 0.3 nm. Traps beyond this depth are not detectable by CP. Therefore, the maximum depth probed by CP ( $x_{max}$ ) can be defined. The parameters used in this simulation are also shown in the figure. The accessible range during CP and the band diagram were schematically shown in Fig. 2. It suggests that detectable traps by CP are most likely to be located within the interfacial layer.

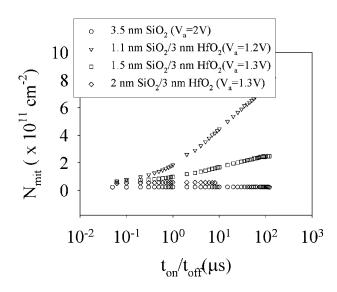

Figure 3 shows the total measured trap density per unit area  $(N_{\rm mit} \, {\rm cm}^{-2})$  as a function of  $t_{\rm on}/t_{\rm off}$  for devices with interfacial layer oxide thicknesses ranging from 1.1 nm to 1.9 nm.  $N_{\rm mit}$  for a control SiO<sub>2</sub> dielectric is also shown for comparison. The values of  $N_{\rm mit}$  at the smallest  $t_{\rm on}/t_{\rm off}$  (or *x*) for all dielectrics are very similar, which suggests that all dielectrics have approximately the same number of traps within the SiO<sub>2</sub> interfacial region. These traps are attributed to the commonly observed interface traps at the Si/SiO<sub>2</sub> interface. The SiO<sub>2</sub> control shows a constant  $N_{\rm mit}$  throughout

FIG. 3. The comparison of  $N_{\rm mit}$  in dielectrics with different thicknesses of the SiO<sub>2</sub> interfacial layer. At the same depth,  $N_{\rm mit}$  is higher for the dielectric with a thicker interfacial layer. As for the SiO<sub>2</sub> dielectric,  $N_{\rm mit}$  is constant, which indicates no further traps exist in the bulk dielectric.

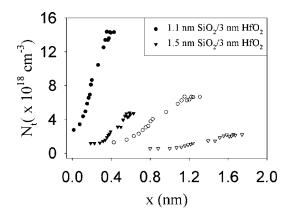

FIG. 4. The comparison of  $N_t$  in dielectrics with different thicknesses of the SiO<sub>2</sub> interfacial layer. The pure SiO<sub>2</sub>, SiO<sub>2</sub>/HfO<sub>2</sub> diffusion, and pure HfO<sub>2</sub> regions can be identified clearly in both dielectrics.

the detectable depth range. It suggests that all of the traps are located near the Si/SiO<sub>2</sub> interface, which is expected and is consistent with observations from other groups.<sup>12,13</sup> For HfO<sub>2</sub>/SiO<sub>2</sub> stacks,  $N_{\text{mit}}$  increases with depth and  $N_{\text{mit}}$  at a given depth decreases with increasing SiO<sub>2</sub> interfacial layer thickness. The thickest interfacial layer (1.9 nm) shows behavior similar to that of the control SiO<sub>2</sub> dielectric. This suggests that the 1.9 nm interfacial layer is sufficiently thick that the depth probed by CP does not reach the transition region between the SiO<sub>2</sub> and HfO<sub>2</sub> layers.

To obtain the trap volume density,  $N_t$  (cm<sup>-3</sup>), the derivative of  $N_{\text{mit}}(x)$  with respect to x is taken and the result is shown in Fig. 4. Since the dielectric with a  $1.9 \text{ nm SiO}_2$ interfacial layer does not indicate the measurement of the SiO<sub>2</sub>/HfO<sub>2</sub> interface, only dielectrics with thinner SiO<sub>2</sub> interfacial layers are plotted. It should be recalled that the relationship between  $t_{on}/t_{off}$  and x is affected by values of dielectric parameters such as effective electron/hole mass inside the dielectric  $(m_{e/h})$ , effective electron/hole barrier height  $(\Phi_{e/h})$ , electron and hole capture cross section at the substrate/IL interface  $[\sigma_{n/p}(0)]$ , and  $V_a$ .<sup>12,13</sup> In Fig. 4,  $N_t$  is plotted as a function of x by using two different sets of parameters under the simplified assumption of a homogeneously thick dielectric. For the solid symbols, the parameters are  $m_{e/h}=0.5/0.4 \text{ eV}$ ,  $\Phi_{e/h}=3.1/3.8 \text{ eV}$ ,  $\sigma_{n/p}(0)=10^{-14}/10^{-16} \text{ cm}^{-2}$ , which are the commonly accepted values for pure SiO<sub>2</sub>.<sup>18,19</sup> The trapping appears to occur within the first 5 Å of the 1 nm interfacial layer by using these parameters. These traps may be generated by the interaction between HfO<sub>2</sub> and the interfacial layer, which was modified by the HfO<sub>2</sub> film and became oxygen deficient.<sup>10,11</sup>

To estimate the upper depth limit for traps probed by the CP measurements, a set dielectric parameters corresponding to HfO<sub>2</sub> was employed:  $m_{e/h}=0.1/0.1$  eV (the smallest values reported),  $\Phi_{e/h}=1.5/3.1$  eV,  $\sigma_{n/p}(0)=10^{-14}/10^{-15}$  cm<sup>-2</sup> (Ref. 20) ( $\sigma_p$  is chosen to be an order of magnitude larger than SiO<sub>2</sub>), as open symbols in Fig. 4. Even with this set of parameters, which favor deeper penetration, the accessible traps are still located within the interfacial layer, and their density gradually increases toward the interface with the high-*k* film. As can be seen in Fig. 4, the  $N_t$  distributions for the gate stacks with 1.1 and 1.5 nm interfacial SiO<sub>2</sub> layer are shifted with respect to each other by approximately 0.3 nm, which is close to the difference between the SiO<sub>2</sub> interfacial layer thicknesses. This indicates that although the exact

Downloaded 26 Jul 2010 to 129.6.65.17. Redistribution subject to AIP license or copyright; see http://apl.aip.org/apl/copyright.jsp

probing depth is unknown, the relative trap spatial distribution is accurate.

The results of this study clearly show that the trap density in the high-*k* gate stack increases with CP probing depth, from the Si/SiO<sub>2</sub> interface toward the SiO<sub>2</sub>/HfO<sub>2</sub> region. This trap profile appears to reflect on structural modifications of the interfacial SiO<sub>2</sub> layer by the overlaying HfO<sub>2</sub> film. The spatially deepest traps accessible by the CP measurements at the kilohertz range are located within or near the interfacial layer rather than in the bulk of the HfO<sub>2</sub> film. This result suggests that the quality of the interfacial layer in high-*k* gate dielectric stacks may represent an important factor that significantly affects high-*k* transistor performance.

- <sup>1</sup>E. Wu, S. H. Lo, W. Abadeer, A. Acovic, D. Buchanan, T. Furukawa, D. Brochu, and R. Dufresne, *Proceedings of the International Reliability Physics Symposium*, 1997, p. 184.

- <sup>2</sup>J. H. Stathis and D. J. DiMaria, Tech. Dig. Int. Electron Devices Meet. **1998**, 167.

- <sup>3</sup>E. M. Vogel, D. Heh, J. B. Bernstein, and J. S. Suehle, IEEE Electron Device Lett. **23**, 667 (2002).

- <sup>4</sup>D. Heh, E. M. Vogel, and J. B. Bernstein, Appl. Phys. Lett. **82**, 3242 (2003).

- <sup>5</sup>T. Kauerauf, R. Degraeve, E. Cartier, C. Soens, and G. Groeseneken, IEEE Electron Device Lett. **23**, 215 (2002).

- <sup>6</sup>R. Degraeve, T. Kauerauf, A. Kerber, E. Cartier, B. Govoreanu, Ph. Roussel, L. Pantisano, P. Blomme, B. Kaczer, and G. Groeseneken, *Proceedings of the International Reliability Physics Symposium*, 2003, p. 23.

- <sup>7</sup>W. J. Zhu, T. P. Ma, S. Zafar, and T. Tamagawa, IEEE Electron Device

- <sup>8</sup>C. W. Yang, Y. K. Fang, C. H. Chen, S. F. Chen, C. Y. Lin, C. S. Lin, M. F. Wang, Y. M. Lin, T. H. Hou, C. H. Chen, L. G. Yao, S. C. Chen, and M. S. Liang, Appl. Phys. Lett. **83**, 308 (2003).

- <sup>9</sup>J. C. Wang, S. H. Chiao, C. L. Lee, T. F. Lei, Y. M. Lin, M. F. Wang, S. C. Chen, C. H. Yu, and M. S. Liang, J. Appl. Phys. **92**, 3936 (2002).

- <sup>10</sup>G. Bersuker, J. Barnett, N. Moumen, B. Foran, C. D. Young, P. Lysaght, J. Peterson, B. H. Lee, P. M. Zeitzoff, and H. R. Huff, Jpn. J. Appl. Phys., Part 1 43, 7899 (2004).

- <sup>11</sup>G. Bersuker, J. Perterson, J. Barnett, A. Korkin, J. H. Sim, R. Choi, B. H. Lee, J. Greer, P. Lysaght, and H. R. Huff, *Proceedings of the 2005 ECS Spring Meeting*, 2005, Vol. 2005-05, p. 141.

- <sup>12</sup>Y.-L. Chu, D.-W. Lin, and C.-Y. Wu, IEEE Trans. Electron Devices **47**, 348 (2000).

- <sup>13</sup>S. Mahapatra, C. D. Parikh, V. Ramgopal Rao, C. R. Viswanathan, and J. Vasi, IEEE Trans. Electron Devices **47**, 171 (2000).

- <sup>14</sup>Y. Maneglia and D. Bauza, J. Appl. Phys. **79**, 4187 (1996).

- <sup>15</sup>D. Bauza and Y. Maneglia, IEEE Trans. Electron Devices **44**, 2262 (1997).

- <sup>16</sup>J. Barnett, N. Moumen, J. Gutt, M. Gardner, C. Huffman, P. Majhi, J. J. Peterson, S. Gopalan, B. Foran, H.-J. Li, B. H. Lee, G. Bersuker, P. Zeitzoff, G. A. Brown, P. Lysaght, C. D. Young, R. W. Murto, and H. R. Huff, presented at 2004 Spring Meeting of the Material Research Society, 2004, p. E1.4.1.

- <sup>17</sup>D. Heh, E. M. Vogel, J. B. Bernstein, C. D. Young, G. A. Brown, G. Bersuker, P. Y. Hung, and A. Diebold (unpublished).

- <sup>18</sup>N. S. Saks and M. G. Ancona, IEEE Electron Device Lett. **11**, 339 (1990).

<sup>19</sup>M. G. Ancona and N. S. Saks, J. Appl. Phys. **71**, 4415 (1992).

- <sup>20</sup>G. Bersuker, J. Sim, C. S. Park, C. Young, S. Nadkarni, R. Choi, and B. H. Lee, *Proceedings of the International Reliability Physics Symposium*, 2006, p. 179.

Lett. 23, 597 (2002).